原創(chuàng)聲明:

本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處。

適用于板卡型號(hào):

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

實(shí)驗(yàn)Vivado工程為“pwm_l

實(shí)驗(yàn)Vivado工程為“rs422_test”。

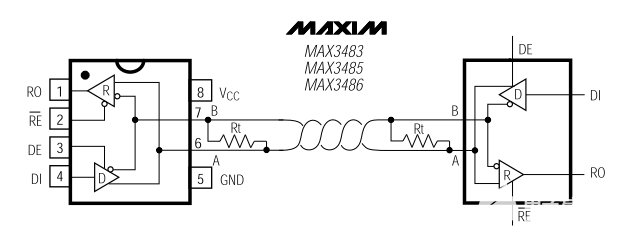

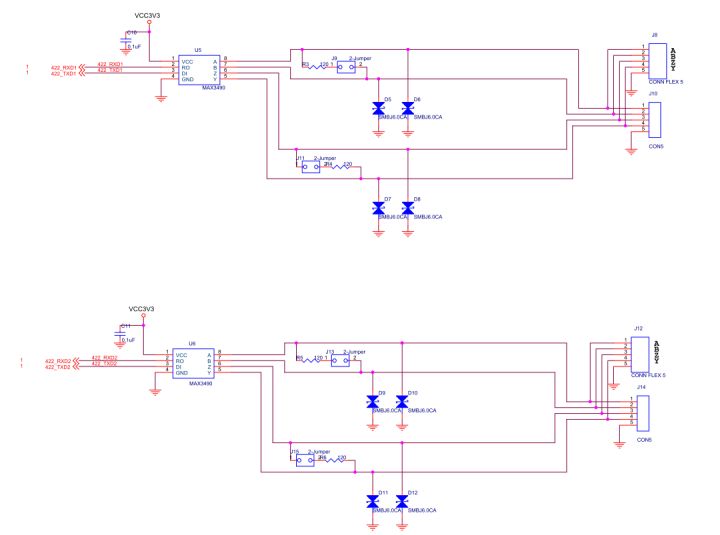

本章利用AN3485模塊實(shí)現(xiàn)RS422接口數(shù)據(jù)傳輸。關(guān)于模塊,在前面的RS232實(shí)驗(yàn)中已經(jīng)介紹過(guò),本實(shí)驗(yàn)不再贅述。RS422與RS232在與FPGA的連接的接口上是一樣的,都是TXD和RXD,因此,本實(shí)驗(yàn)在RS232實(shí)驗(yàn)的基礎(chǔ)上,例化出兩路連接到RS422接口芯片MAX3490上。

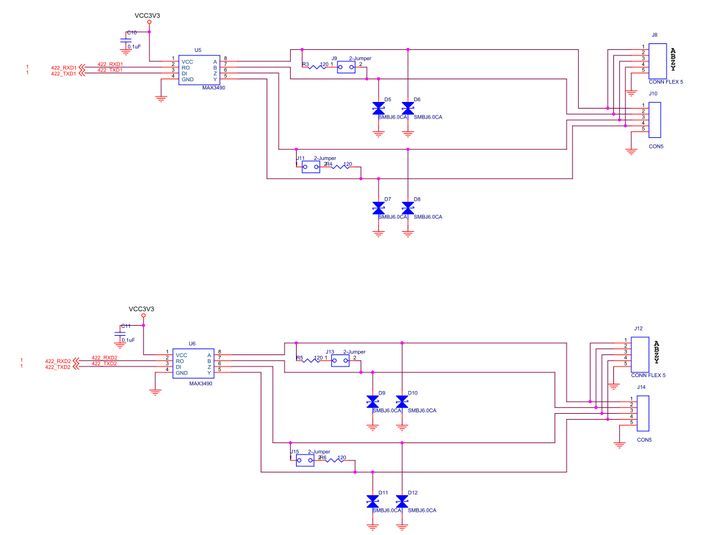

RS422接口部分原理圖

RS422接口部分原理圖

1. 程序設(shè)計(jì)

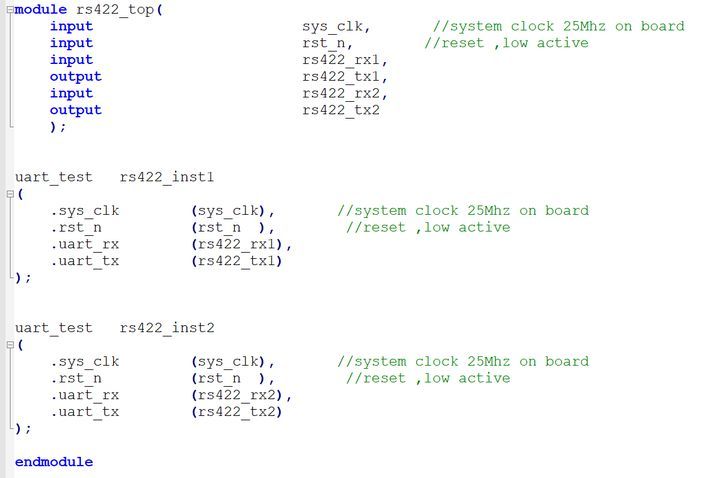

程序設(shè)計(jì)比較簡(jiǎn)單,以RS232實(shí)驗(yàn)為基礎(chǔ),例化兩路uart_test即可。

2. 實(shí)驗(yàn)測(cè)試

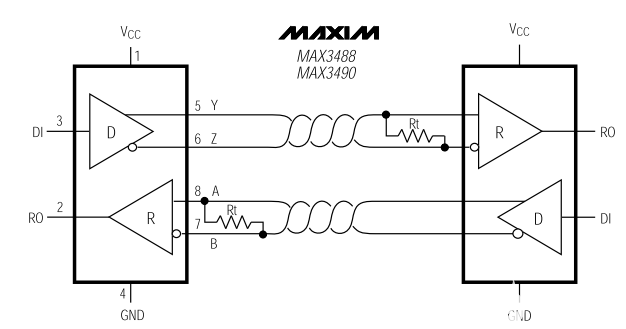

RS422的接口部分是差分的信號(hào),共四根信號(hào)線,兩根發(fā)送TXD+和TXD-,對(duì)應(yīng)Y和Z,兩根接收RXD+和RXD-,對(duì)應(yīng)A和B。

與RS232實(shí)驗(yàn)一樣,也采用USB轉(zhuǎn)串口的設(shè)備連接,使用杜綁線將模塊的RS422_1的Y和Z分別與設(shè)備的R+和R-連接,將模塊的A和B分別與設(shè)備的T+和T-連接。

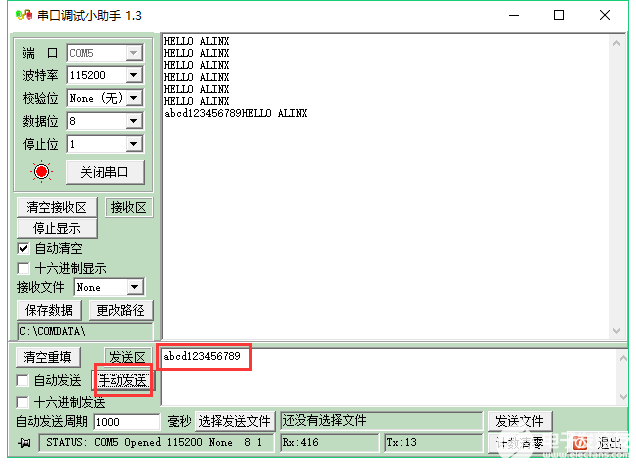

下載程序后,即可在串口工具中看到RS232實(shí)驗(yàn)同樣的效果,可以利用同樣的方法測(cè)試RS422_2接口。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613939 -

RS422

+關(guān)注

關(guān)注

4文章

80瀏覽量

36991 -

MAX3

+關(guān)注

關(guān)注

0文章

98瀏覽量

40121 -

Zynq

+關(guān)注

關(guān)注

10文章

614瀏覽量

48011 -

MPSoC

+關(guān)注

關(guān)注

0文章

199瀏覽量

24615

發(fā)布評(píng)論請(qǐng)先 登錄

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十三章RS485實(shí)驗(yàn)

明德?lián)P視頻分享點(diǎn)撥FPGA課程---第十二章??學(xué)習(xí)自檢方法

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

Zynq UltraScale+ MPSoC的發(fā)售消息

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十二章 RS422實(shí)驗(yàn)

如何調(diào)試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

米爾電子zynq ultrascale+ mpsoc底板外設(shè)資源清單分享

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設(shè)計(jì)

Zynq UltraScale+ MPSoC中的隔離方法

Zynq UltraScale+ MPSoC的隔離設(shè)計(jì)示例

Zynq UltraScale+ MPSoC驗(yàn)證數(shù)據(jù)手冊(cè)

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十二章RS422實(shí)驗(yàn)

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十二章RS422實(shí)驗(yàn)

評(píng)論