原創聲明:

本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

本章采用AN3485模塊的RS232電路實現UART數據傳輸。

1.模塊介紹

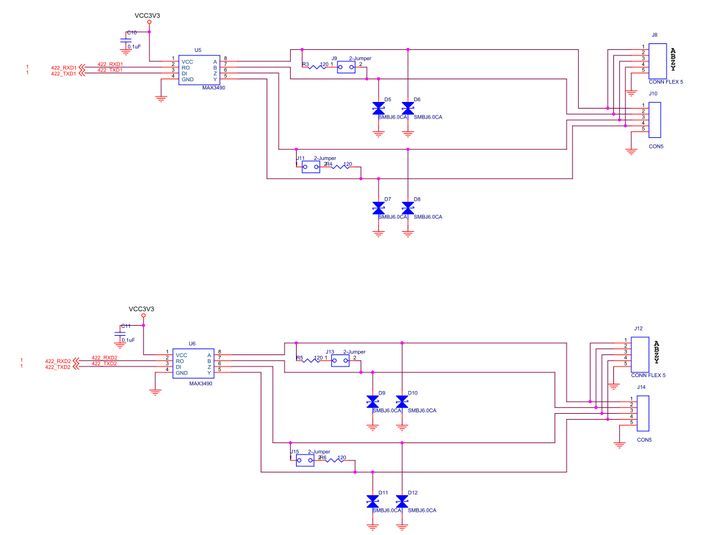

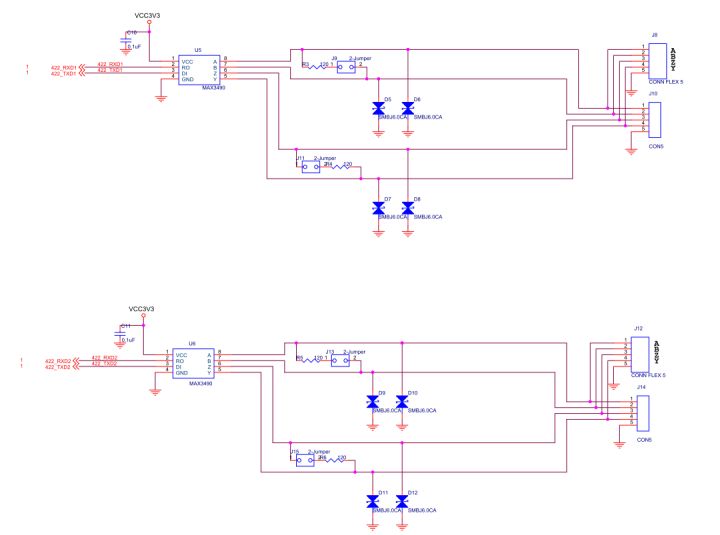

AN3845模塊專門為工業現場應用設計的RS232/485/422通信模塊。它包含一路RS232接口,2路RS485和2路RS422通信接口。配合開發板實現RS232、485和422的數據遠程傳輸和通信。RS232、485和422接口分別采用MAX3232、MAX3485和MAX3490芯片作為電平轉換芯片。模塊留有一個40針的排母用于連接開發板,RS232接口為一個標準的DB9串口公座,通過串口線直接連接電腦或者其他設備; RS485和RS422接口采用接線端子跟外部連接,超遠距離傳輸可達上千米,另外RS485和RS422接口部分帶有正負15KV的ESD防護功能。

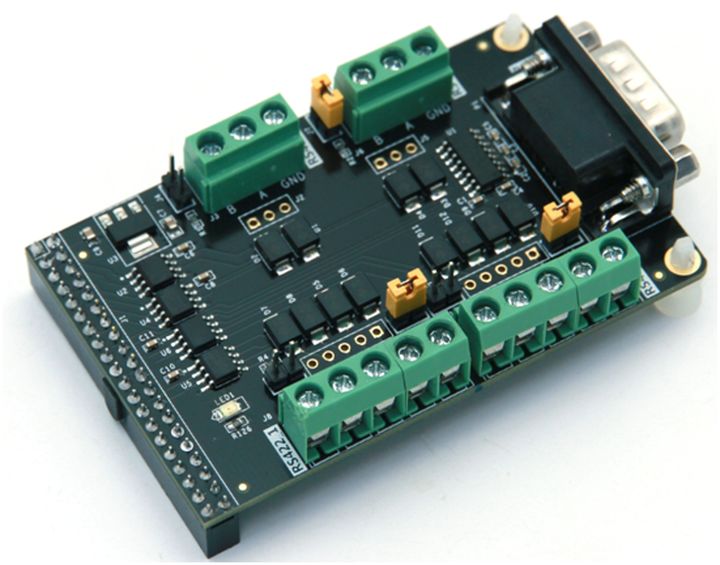

AN3845模塊實物照片如下:

AN3845通信模塊正面圖

1.1 模塊參數說明

以下為AN3485通信模塊的詳細參數:

RS232接口

-

-

一路標準的DB9公座串行接口;

-

使用MAX3232作為RS232和 TTL電平的轉換;

-

傳輸率高達120Kbps數據通訊速率

-

RS485接口

RS422接口

-

-

兩路RS422接口,采用5線的接線端子;

-

使用MAX3490作為RS422和TTL的電平轉換;

-

工業級設計,抗干擾能力超強,同時采用有效的防雷設計;

-

具有120歐匹配電阻,插上跳線帽即可使能匹配電阻,長距離傳輸時建議短接。

-

支持多機通訊,允許接在最多128個設備的總線上

-

傳輸率高達500Kbps數據通訊速率。

-

1.2 模塊功能說明

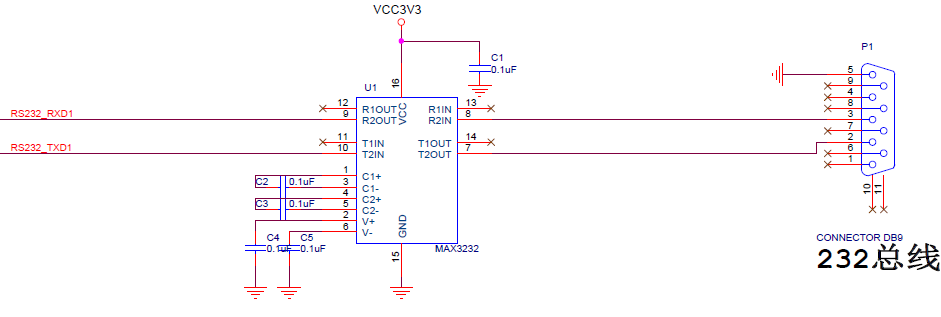

AN3485模塊的RS232接口采用MAX3232芯片實現RS232和+3.3V TTL電平的轉換。TTL電平的串口接收和發送信號(RXD, TXD)連接到40針的連接器上跟外面的FPGA芯片或者ARM芯片實現串口通信。RS232串口通信的最高速度為120kbps,RS232接口的原理設計圖如下圖所示。

2. 程序設計

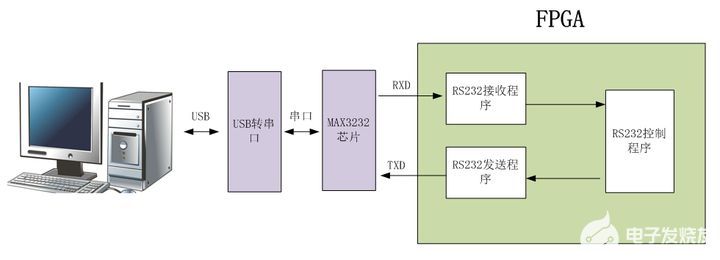

本文所述的串口指異步串行通信,異步串行是指UART(Universal Asynchronous Receiver/Transmitter),通用異步接收/發送。本實驗程序設計為每秒鐘向串口發送”HELLO ALINX”,如果收到RXD接收的數據,再把接收的數據發送出去,實現回環的功能。

2.1 異步串口通信協議

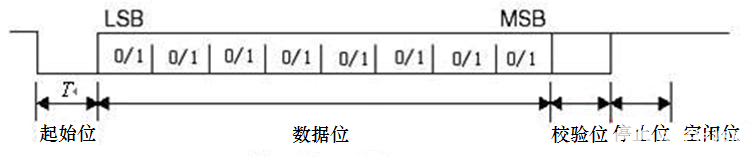

消息幀從一個低位起始位開始,后面是7個或8個數據位,一個可用的奇偶位和一個或幾個高位停止位。接收器發現開始位時它就知道數據準備發送,并嘗試與發送器時鐘頻率同步。如果選擇了奇偶校驗,UART就在數據位后面加上奇偶位。奇偶位可用來幫助錯誤校驗。在接收過程中,UART從消息幀中去掉起始位和結束位,對進來的字節進行奇偶校驗,并將數據字節從串行轉換成并行。UART 傳輸時序如下圖所示:

從波形上可以看出起始位是低電平,停止位和空閑位都是高電平,也就是說沒有數據傳輸時是高電平,利用這個特點我們可以準確接收數據,當一個下降沿事件發生時,我們認為將進行一次數據傳輸。

2.2 波特率

常見的串口通信波特率有2400 、9600、115200等,發送和接收波特率必須保持一致才能正確通信。波特率是指1秒最大傳輸的數據位數,包括起始位、數據位、校驗位、停止位。假如通信波特率設定為9600,那么一個數據位的時間長度是1/9600秒,本實驗中的波特率由50MHz時鐘產生。

2.3 接收模塊設計

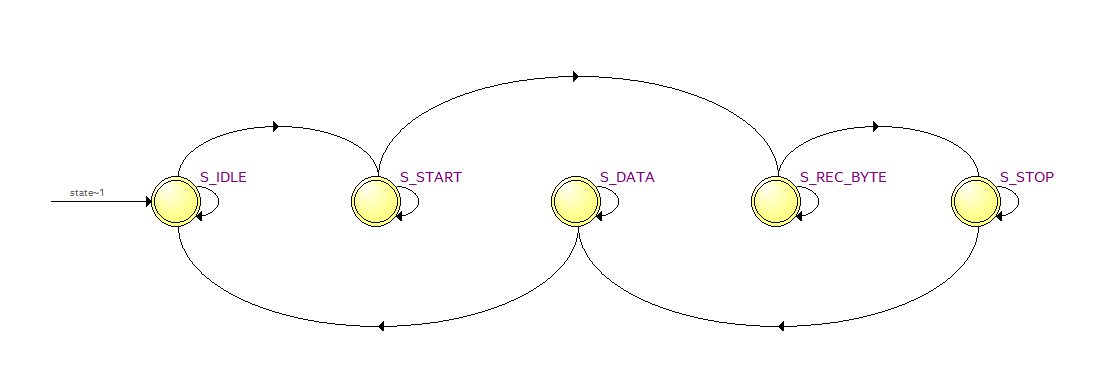

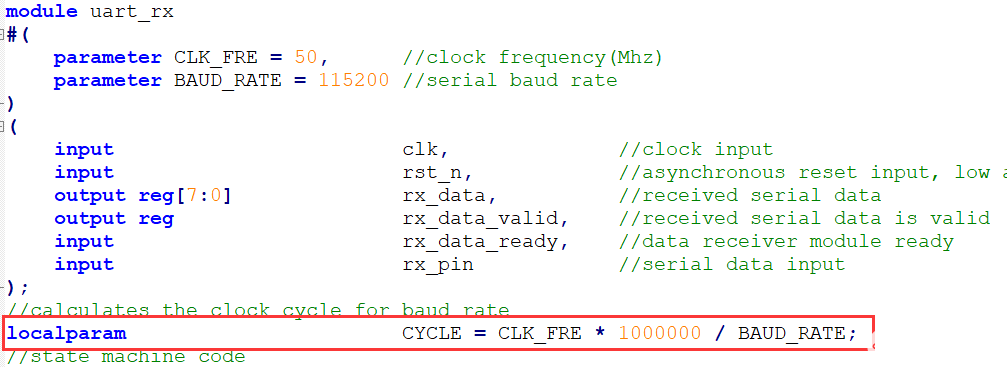

串口接收模塊uart_rx是個參數化可配置模塊,參數“CLK_FRE”定義接收模塊的系統時鐘頻率,單位是Mhz,參數“BAUD_RATE”是波特率。接收狀態機狀態轉換圖如下:

“S_IDLE”狀態為空閑狀態,上電后進入“S_IDLE”,如果信號“rx_pin”有下降沿,我們認為是串口的起始位,進入狀態“S_START”,等一個BIT時間起始位結束后進入數據位接收狀態“S_REC_BYTE”,本實驗中數據位設計是8位,接收完成以后進入“S_STOP”狀態,在“S_STOP”沒有等待一個BIT周期,只等待了半個BIT時間,這是因為如果等待了一個周期,有可能會錯過下一個數據的起始位判斷,最后進入“S_DATA”狀態,將接收到的數據送到其他模塊。在這個模塊我們提一點:為了滿足采樣定理,在接受數據時每個數據都在波特率計數器的時間中點進行采樣,以避免數據出錯的情況:

//receiveserialdatabitdataalways@(posedgeclkornegedgerst_n)begin if(rst_n==1'b0) rx_bits<=8'd0; elseif(state?==?S_REC_BYTE?&&?cycle_cnt?==?CYCLE/2-1) rx_bits[bit_cnt]<=?rx_pin; else rx_bits?<=?rx_bits;end

注意:本實驗沒有設計奇偶校驗位。

| 信號名稱 | 方向 | 寬度(bit) | 說明 |

| clk | in | 1 | 系統時鐘 |

| rst_n | in | 1 | 異步復位,低電平復位 |

| rx_data | out | 8 | 接收到的串口數據(8位數據) |

| rx_data_valid | out | 1 | 接收到的串口數據有效(高有效) |

| rx_data_ready | in | 1 | 表示用戶可以從接收模塊接收數據,當rx_data_ready和rx_data_valid都為高時數據送出 |

| rx_pin | in | 1 | 串口接收數據輸入 |

串口接收模塊uart_rx端口

2.4 發送模塊設計

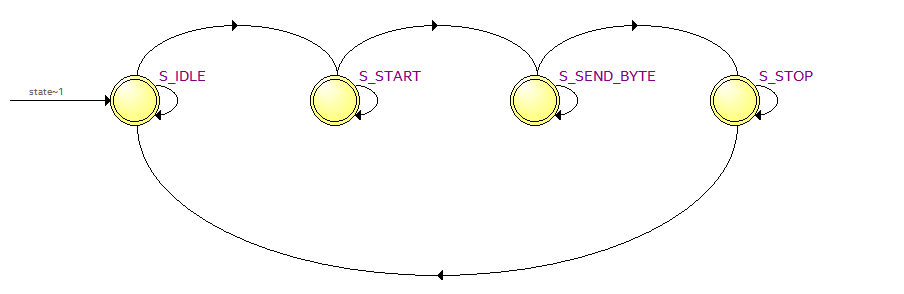

發送模塊uart_tx設計和接收模塊相似,也是使用狀態機,狀態轉換圖如下:

上電后進入“S_IDLE”空閑狀態,如果有發送請求,進入發送起始位狀態“S_START”,起始位發送完成后進入發送數據位狀態“S_SEND_BYTE”,數據位發送完成后進入發送停止位狀態“S_STOP”,停止位發送完成后又進入空閑狀態。在數據發送模塊中,從頂層模塊寫入的數據直接傳遞給寄存器‘tx_reg’,并通過‘tx_reg’寄存器模擬串口傳輸協議在狀態機的條件轉換下進行數據傳送:

always@(posedgeclkornegedgerst_n)begin if(rst_n==1'b0) tx_reg<=1'b1; else case(state) S_IDLE,S_STOP: tx_reg?<=1'b1; S_START: tx_reg?<=1'b0; S_SEND_BYTE: tx_reg?<=?tx_data_latch[bit_cnt]; default: tx_reg?<=1'b1; endcaseend

| 信號名稱 | 方向 | 寬度(bit) | 說明 |

| clk | in | 1 | 系統時鐘 |

| rst_n | in | 1 | 異步復位,低電平復位 |

| tx_data | in | 8 | 要發送的串口數據(8位數據) |

| tx_data_valid | in | 1 | 發送的串口數據有效(高有效) |

| tx_data_ready | out | 1 | 發送模塊已準備好發送數據,用戶可將tx_data_valid信號拉高發送數據給發送模塊。當tx_data_ready和tx_data_valid都為高時數據被發送 |

| tx_pin | out | 1 | 串口發送數據發送 |

串口發送模塊uart_tx端口

2.5 波特率的產生

在發送和接收模塊中,聲明了參數CYCLE,也就是UART一個周期的計數值,當然計數是在50MHz時鐘下進行的。用戶只要設定好CLK_FRE和BAUD_RATE這兩個參數即可。

測試程序

測試程序設計FPGA為1秒向串口發送一次“HELLO ALINX\r\n”,不發送期間,如果接受到串口數據,直接把接收到的數據送到發送模塊再返回。“\r\n”,在這里和C語言中表示一致,都是回車換行。

測試程序分別例化了發送模塊和接收模塊,同時將參數傳遞進去,波特率設置為115200。

always@(posedgesys_clkornegedgerst_n)begin if(rst_n==1'b0) begin wait_cnt<=32'd0; tx_data?<=8'd0; state?<=?IDLE; tx_cnt?<=8'd0; tx_data_valid?<=1'b0; end else case(state) IDLE: state?<=?SEND; SEND: begin wait_cnt?<=32'd0; tx_data?<=?tx_str; if(tx_data_valid?==1'b1&&?tx_data_ready?==1'b1&&?tx_cnt?<8'd12)//Send?12?bytes?data begin tx_cnt?<=?tx_cnt?+8'd1;//Send?data?counter end elseif(tx_data_valid?&&?tx_data_ready)//last?byte?sent?is?complete begin tx_cnt?<=8'd0; tx_data_valid?<=1'b0; state?<=?WAIT; end elseif(~tx_data_valid) begin tx_data_valid?<=1'b1; end end WAIT: begin wait_cnt?<=?wait_cnt?+32'd1; if(rx_data_valid?==1'b1) begin tx_data_valid?<=1'b1; tx_data?<=?rx_data;//?send?uart?received?data end elseif(tx_data_valid?&&?tx_data_ready) begin tx_data_valid?<=1'b0; end elseif(wait_cnt?>=CLK_FRE*1000000)//waitfor1second state<=?SEND; end default: state?<=?IDLE; endcaseend//combinational?logic//Send?"HELLO?ALINX\r\n"always@(*)begin case(tx_cnt) 8'd0:??tx_str?<="H"; 8'd1:??tx_str?<="E"; 8'd2:??tx_str?<="L"; 8'd3:??tx_str?<="L"; 8'd4:??tx_str?<="O"; 8'd5:??tx_str?<="?"; 8'd6:??tx_str?<="A"; 8'd7:??tx_str?<="L"; 8'd8:??tx_str?<="I"; 8'd9:??tx_str?<="N"; 8'd10:??tx_str?<="X"; 8'd11:??tx_str?<="\r"; 8'd12:??tx_str?<="\n"; default:tx_str?<=8'd0; endcaseenduart_rx#(.CLK_FRE(CLK_FRE),.BAUD_RATE(115200))?uart_rx_inst(.clk????????????????????????(sys_clk??????????????????),.rst_n??????????????????????(rst_n????????????????????),.rx_data????????????????????(rx_data??????????????????),.rx_data_valid??????????????(rx_data_valid????????????),.rx_data_ready??????????????(rx_data_ready????????????),.rx_pin?????????????????????(uart_rx??????????????????));uart_tx#(.CLK_FRE(CLK_FRE),.BAUD_RATE(115200))?uart_tx_inst(.clk????????????????????????(sys_clk??????????????????),.rst_n??????????????????????(rst_n????????????????????),.tx_data????????????????????(tx_data??????????????????),.tx_data_valid??????????????(tx_data_valid????????????),.tx_data_ready??????????????(tx_data_ready????????????),.tx_pin?????????????????????(uart_tx??????????????????));

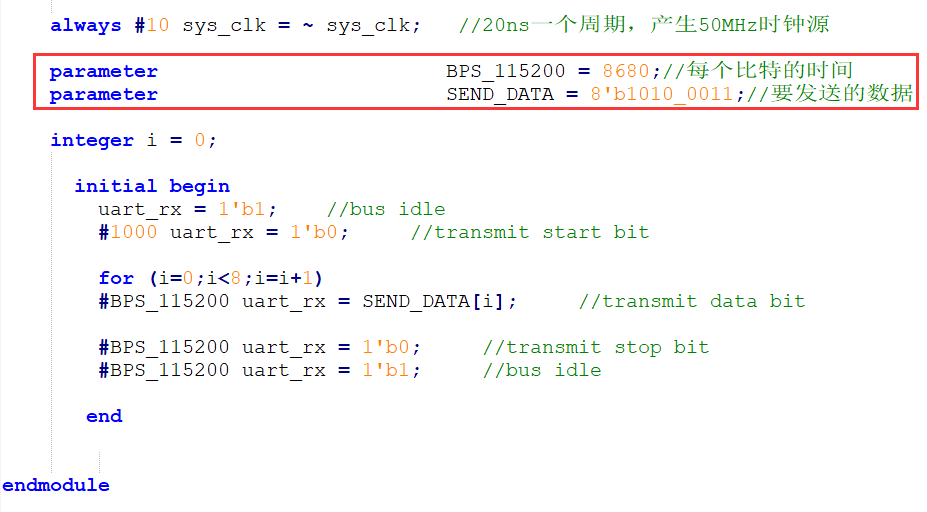

3. 仿真

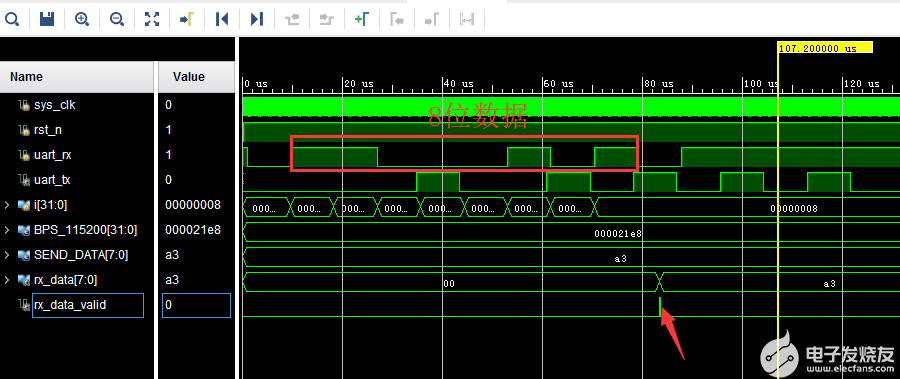

這里我們添加了一個串口接收的激勵程序vtf_uart_test.v文件,用來仿真uart串口接收。這里向串口模塊的uart_rx發送0xa3的數據, 每位的數據按115200的波特率發送,1位起始位,8位數據位和1位停止位。

仿真的結果如下,當程序接收到8位數據的時候,rx_data_valid有效,rx_data[7:0]的數據位a3。

實驗測試

將AN3485模塊插到J11擴展口上,這里使用了USB轉RS232/RS485/RS422的設備,由于很多電腦都沒有9針的串行接口,我們通過串口線與USB轉串口設備連接,再通過USB連接到電腦上。如果電腦有串口的話,可以直接連接串口。

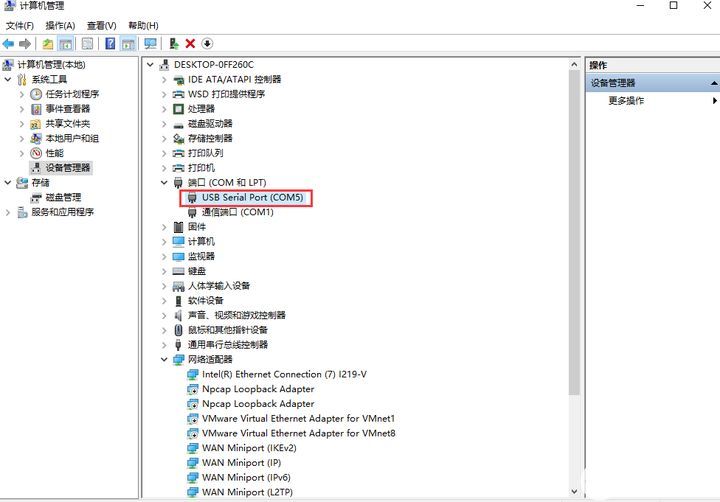

在設備管理器中找到串口號”COM5”

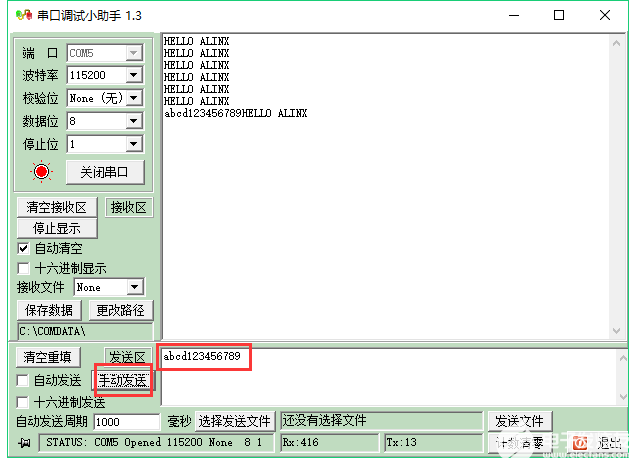

打開串口調試,端口選擇“COM5”(根據自己情況選擇),波特率設置115200,檢驗位選None,數據位選8,停止位選1,然后點擊“打開串口”。此軟件在例程文件夾下。

打開串口以后,每秒可收到“HELLO ALINX”,在發送區輸入框輸入要發送的文字,點擊“手動發送”,可以看到接收到自己發送的字符。

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613940 -

RS232

+關注

關注

13文章

795瀏覽量

95505 -

uart

+關注

關注

22文章

1264瀏覽量

103216 -

Zynq

+關注

關注

10文章

614瀏覽量

48011 -

MPSoC

+關注

關注

0文章

199瀏覽量

24615

發布評論請先 登錄

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十二章RS422實驗

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

Zynq UltraScale+ MPSoC的發售消息

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十二章 RS422實驗

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

米爾電子zynq ultrascale+ mpsoc底板外設資源清單分享

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

Zynq UltraScale+ MPSoC中的隔離方法

Zynq UltraScale+ MPSoC的隔離設計示例

Zynq UltraScale+ MPSoC驗證數據手冊

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十一章RS232實驗

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十一章RS232實驗

評論