電子發燒友網核心提示:本文介紹使用Altera低成本Cyclone V SoC FPGA,實現典型雷達系統數字化處理的可行性。與定制ASIC 相比,這一方法的優勢在于縮短了產品面市時間,支持現場更新升級,能夠在浮點、預集成ARM Cortex-A9雙核微處理器系統中快速方便的實現,而且還可以使用汽車級器件。

引言

雷達一直用在軍事和商業應用中。最近,雷達開始出現在高端汽車應用中,用于實現輔助駐車和車道偏離報警等功能。下一代汽車雷達一定會非常復雜,在主動防碰撞和自適應巡航系統中,雷達將扮演關鍵角色。雷達一旦集成到主動控制車輛的系統中后,與僅僅提供報警信號不同,它與防止車輛碰撞密切相關,因此,對系統可靠性的要求更加嚴格。

本文介紹怎樣使用Altera 快速原型設計和開發工具流程,發揮數字處理功能的優勢,通過稱之為DSP Builder 高級數字信號處理(DSP) 的設計,開發汽車雷達系統。結果提供了雷達處理數字部分的實際電路和性能指標。數字處理功能采用了新一代可編程邏輯,稱之為SoC FPGA,它在低成本FPGA 架構中嵌入了功能強大的600MHz ARM Cortex-A9 雙核處理器。還可以使用汽車級的這些器件,支持600 MHz CPU 時鐘速率。

從雷達到光探測和測距(LIDAR),直至紅外和可見光攝像機等應用,SoC FPGA 為這些應用提供了靈活的可伸縮平臺。而且,FPGA 硬件和ARM 軟件實現都使用了浮點處理,與FPGA 或者ASIC 中實現的傳統定點方法相比,這在雷達應用中更具優異的性能優勢。與其他ASIC 解決方案相比,這些低成本SoC FPGA 器件支持大批量應用,而且產品能夠更迅速面市。

SoC FPGA 方法支持對產品線甚至是現場固件進行軟件和硬件更新,這對于越來越復雜的汽車雷達系統而言非常重要。SoC FPGA 也是攝像機集成視頻處理功能的理想選擇。視頻分析處理可以結合雷達探測信息,用在名為傳感器融合的過程中,在這一過程中,多個傳感系統相結合,產生最可靠的數據,進行基本判斷。

汽車雷達的脈沖多普勒方法

很多雷達系統采用了脈沖多普勒方法,發送器工作一段很短的時間,然后,系統切換到接收模式,直到產生下一個發送脈沖。脈沖多普勒雷達按照一定的間隔或者脈沖重復間隔(PRI) 來發送連續脈沖。雷達信號返回后,對反射信號進行連續處理,提取出被探測目標的范圍和相對運動信息。空時自適應雷達(STAP) 等更復雜的處理方法進一步處理雷達反射信號信息,即使是在地雜波嚴重遮蔽,或者背景反射被探測目標周圍物體的情況下,也能夠提取出目標數據。

在汽車雷達中,探測范圍可以短到只有幾米,也能夠長達幾百米。對于2 m 的范圍,雷達脈沖的往返傳輸時間是13 ns。這么短的距離要求發送器和接收器能夠同時工作,這就需要使用相互分開的天線。脈沖多普勒雷達周期性的發送脈沖,發送器工作的時間與總時間之比就是占空比。由于占空比一般較小,因此,這一比例限制了總發送功率。功率大小也就限制了探測范圍。實現1 到2 m 范圍的探測分辨率還要求100MSPS甚至更高量級的采樣率,能夠對目標范圍和多普勒大小數據進行數字化處理。較高的采樣率提高了雷達系統的成本。

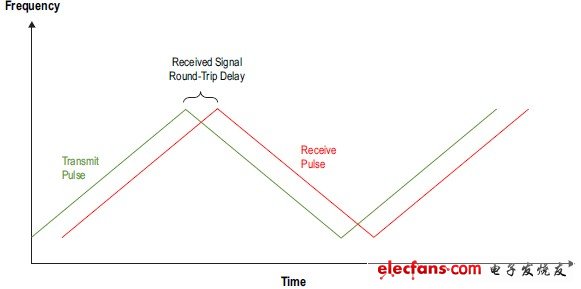

或者,可以采用名為連續波頻率調制(CWFM) 的雷達方法。CWFM 并不發射脈沖,然后監視返回信號,即雷達回波。而是連續發送載波頻率。為能夠從連續返回波中提取出有用信息,載波頻率隨時間穩步增大,然后下降,如圖1 所示。發送器和接收器都是連續工作。為防止發送信號泄漏到接收器中,我們的發送和接收天線是分開的。

雷達必須確定被探測目標的范圍。在CWFM 中,通過測量與發送頻率的瞬時接收頻率差,即delta,來獲得這一范圍。在發送周期的頻率斜坡上升部分,接收頻率要小于發送頻率,這取決于時間延時。在發送周期的頻率斜坡下降部分,接收頻率要大于發送頻率,這也取決于時間延時。這些頻率差,或者偏移,與往返延時成正比,因此,提供了測量范圍的一種手段。范圍越大,從發送器到接收器的時間延時就越大。由于發送頻率在不斷變化,因此,任何時候的發送和接收頻率之差都與發送信號從雷達傳輸至目標然后返回所花費的時間成正比。

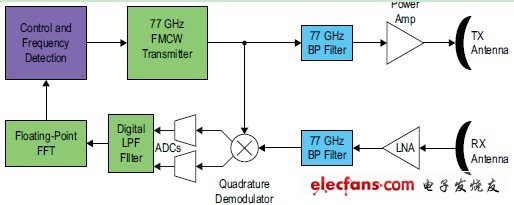

圖2 所示是CWFM 雷達的實際結構圖。汽車雷達工作在毫米范圍,意味著,發送信號的波長只有幾個毫米。常用的頻率是24 GHz (λ =12.5 mm) 和77 GHz (λ = 3.9 mm)。我們之所以使用這些頻率主要是考慮到,需要尺寸較小的天線,頻譜的相對可用性,射頻信號的快速衰減( 汽車雷達范圍限制在數百米) 等因素。通過使用CWFM,就不需要幅度調制,發送器僅在頻率上變化。使用FM,支持發送電路工作在飽和狀態,這是所有RF 放大器最高效的模式。

由于采用了模擬合成器電路,因此,接收器低通濾波器只需要通過接收和發送信號之間的差值,不需要通過相對于發送周期500 MHz 帶寬的接收信號。很容易由實例來說明這一信號差值的通過特性。讓我們假設接收反射信號處于系統的極端范圍內,即:1m 距離和300 m 的距離。當頻率斜坡是0.5 ms 內500 MHz 時,即每ns 1 kHz,接收信號的頻率如下:其中,光速是3 x 10e8 m/s:1m距離=2m往返延時=2m/(3*10e8m/s) =7ns;300m距離 =600m往返延時 =600m/(3 *10e8 m/s) = 2us。

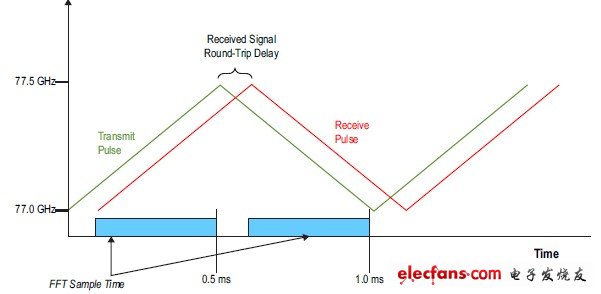

在頻率斜坡上升期間,從1 m 距離的物體反射回的信號具有-7 kHz 的偏移。在頻率斜坡下降期間,從1m距離的物體反射回的信號具有+7 kHz的偏移。在頻率斜坡上升期間,從300 m 距離的物體反射回的信號具有-2 MHz 的偏移。在頻率斜坡下降期間,從1 m 距離的物體反射回的信號具有+2 MHz 的偏移。這些偏移告訴我們,接收器會看到±2 MHz 范圍的頻率,它取決于產生回波信號的目標的范圍。通過對圖3 所示的時間間隔進行快速傅里葉變換(FFT),可以探測到這一頻率。如果接收器采樣是5 MSPS,那么對于大約0.4 ms 的接收器FFT 采樣間隔,可以使用2,048 點的FFT,其頻率分辨率大約為1 kHz,足以達到一米以下的分辨率。通過對FFT 輸出進行插值處理,還可以進一步提高分辨率。

圖3. 接收器FFT 采樣間隔

觀察到的這種頻率偏移為接收器提供了目標范圍,但是不能用于分辨迎面行駛的車輛、同向行駛的車輛,以及同樣范圍內的靜止物體。為能夠對此進行分辨,必須利用反射信號的多普勒頻移特性。

還是通過一個實例來很好的說明怎樣探測到多普勒頻移。假設裝備了77 GHz 雷達的汽車,時速達到80 km/ 小時,即,22.2 m/s,考慮在30 m 的距離上有三個目標—— 一個是迎面以50 km/ 小時速度行駛的車輛,另一個是以100 km/ 小時速度同向行駛的車輛,還有一個靜止的物體。當目標接近時,多普勒頻移是正值,意味著返回信號的頻率高于發送信號的頻率。直觀的,這是因為,由于距離接近,導致信號波峰看起來更靠近一些。相反,當雷達和目標之間的距離拉遠時,即,彼此越來越遠,那么,結果是負的多普勒頻移。可以按照方程1 來計算多普勒頻移的大小。

方程1. 多普勒頻移

多普勒頻移 = (2*速度差)/波長

迎面行駛的汽車速度是50km/小時,安裝了雷達的汽車速度是80km/小時,接近速度是130 km/小時,即時36.1m/s。

多普勒頻移 = 2 (36.1 m/s)/(.0039 m)=18.5kHz

對于靜止物體,安裝了雷達的汽車速度是80km/小時,那么,接近速度是80km/小時,即22.2m/s。

多普勒頻移 = 2 (22.2 m/s)/(.0039 m) = 11.4kHz

前面同向行駛的汽車速度是100 km/ 小時,安裝了雷達的汽車速度是80 km/ 小時,那么,拉開的速度是20km/小時,即5.56 m/s。

多普勒頻移 = -2 (5.56 m/s)/(.0039 m) =-2.8kHz

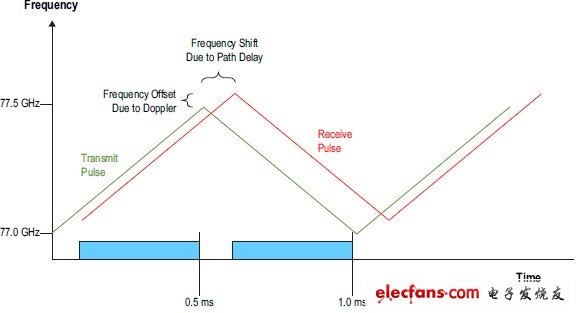

這些多普勒頻移會對探測到的頻率上升和下降斜坡的頻率差產生偏移。沒有相對運動時,對于上升和下降頻率斜坡,沒有多普勒頻移,那么接收頻率差相等,但是符號相反。那么,可以通過對比發送信號頻率斜坡上升期間和下降期間的接收頻率偏移,找到多普勒頻移。方程2 描述了這一關系,使用發送器頻率斜坡上升和下降期間的結果,通過FFT 的輸出來確定范圍和相對速度。

方程2. 相對速度

相對速度( 目標和雷達之間) = ( 波長÷2)×( 探測到的頻率上升斜坡–探測到的頻率下降斜坡)÷2

接收器接收到的頻率,以及FFT 處理的頻率如圖4 所示。接收器使用發送信號作為本地振蕩器(LO),進行解調,或者下轉換,那么,FFT 會處理發送和接收波形之間的頻率差。圖4 顯示了一個目標脈沖回波;但是,會有多個( 我們的例子中是三個) 不同的目標產生多個頻率,FFT 能夠探測出這些頻率。

圖4. 多普勒頻率探測

返回到實例中來,在30 m 距離上有三個目標—— 一個是迎面以50 km/ 小時速度行駛的車輛,另一個是以100 km/ 小時速度同向行駛的車輛,還有一個靜止的物體。安裝了雷達的汽車速度是80 km/ 小時,即22.2 m/s。對于30 m 距離的所有三個目標,接收頻率偏移是:

30 m 范圍 = 60 m往返延時 = 60m÷(3 *10e8 m/s) =200ns

頻率偏移:下降頻率斜坡和上升頻率斜坡分別是±200 kHz。

多普勒偏移必須加到由范圍延時導致的頻率偏移中。表1 對這些數值進行了總結。

表1. 由于范圍和多普勒導致的目標頻率偏移

只使用觀察到的下降和上升頻率偏移,可以通過方程3、方程4 和方程5 來確定目標范圍和相對多普勒頻移。由于已經知道安裝了雷達的汽車的行駛速度,因此,很容易計算出目標的速度。相似的,也能夠知道雷達的頻率斜率。

方程3. 范圍

范圍 = (光速÷(4×頻率斜率))×(下降頻率偏移–上升頻率偏移)

方程4. 相對速度

相對速度 = (光速÷(4×載波頻率))×(下降頻率偏移+上升頻率偏移)

方程5. 絕對目標速度

絕對目標速度 = 相對速度–裝有雷達的車輛的速度

在這一例子中,頻率斜率是0.5 ms 內500 MHz,即,每秒1,000 GHz。插入我們的實例值,我們發現:

對于接近50 km/h 的車輛:

范圍 = (3·10e8 /(4*1000*10e9))*(218.5*10e3 – -181.5*10e3) =30 m

相對速度 = (3·10e8/(4*77*10e9))*(218.5*10e3 + -181.5*10e3) = 36m/s= 130 km/hr

絕對目標速度 = 130–80 =50 km/小時接近速率

其他目標的計算也是相似的。

在出現多個目標時,需要考慮的一個關鍵因素是,不太容易知道怎樣對下降和上升斜坡周期的頻率進行配對。在雷達術語中,這一問題被稱為“ 模糊”,需要特殊方法來處理它,與多普勒雷達相比,在CWFM 雷達中,這一問題要更復雜一些。

解決這一問題的一個方法是改變斜坡的持續時間和頻率,研究在具有不同頻率斜坡陡度的頻譜中,被探測的頻率是怎樣變化的。這種變化支持上升頻率和下降頻率進行精確的配對,以識別每一目標。由于斜坡大概每毫秒變化一次,因此,在不到一秒的時間內能夠分析數百次這種變化。一般是控制處理器完成這一工作,在 SoC FPGA 的一個ARM Cortex-A9 處理器中實現控制處理器,控制頻率斜坡和持續時間的設置,從上升和下降頻率斜坡中探測到的FFT 輸出頻率來確定目標范圍和多普勒。

使用其他的傳感技術也會有所幫助。攝像機有助于分辨來自車輛較強的反射信號和來自人員較弱的反射信號,以及可能會出現哪一類多普勒偏移。如果采用了立體攝像機,那么,也可以通過圖像分析技術來幫助估算范圍。

另一種選擇是多模式雷達,使用CWFM 來找到開闊高速公路較遠距離上的目標,而在城市區域使用短距多普勒雷達,在城市中,近距離內會有很多目標反射信號。在擁擠的目標環境中,多普勒雷達的模糊探測問題不太嚴重。

雷達鏈路預算

雷達性能主要是由鏈路預算方程決定的,它確定了探測可以使用哪一級的接收信號。方程6 表達了簡化的雷達鏈路預算。

方程6. 雷達鏈路預算

Prcv = Ptrx*G*G*σ*λ*λ*τ/(( 4π)e3* Re4)

其中:

Ptrx 是峰值發送功率;G 是發送和接收天線增益;σ是目標區域的雷達交叉部分;λ是雷達波長;τ是發送器占空比;R 是目標范圍。

一般以對數標度來設定參數,使用分貝(dB),或者dBm (dB 是以1 mW 為參考)。這個例子中使用了這一標度,但也同時會給出瓦特指標。我們必須做出一些假設。可以實現的接收器噪聲指標是5 dB,接收器靈敏度指標應該在-120dBm (10-15 W)。假設大約20 dB 的信噪比(SNR) 能夠實現合理的頻率探測,那么,在最差環境下,將要求Prcv 應至少為100 dBm (10-13 W)。天線增益大約為30 dB,即,1000。對于拋物面天線,可以采用方程7 來計算天線軸向增益。

方程7. 天線軸向增益

G = 4πAeff /λ ?

回到前面的工作,我們發現77 GHz 時,天線需要的區域是.0012 m2,其直徑是0.04m,即4 cm,這一尺寸完全可以在汽車頭部安裝實現。( 注意,我們至少需要一面發送和一面接收天線)。

在CWFM 中,占空比? 是100%,即,1。如果我們假設發送功率是0.1 W (20 dBm),最大范圍300 m,目標車輛反射區域是1 m2,我們可以找到在一定環境下最差情況的接收功率。

Prcv = (0.1* 1000e2*1*.0039e2 *1)/(( 4π)e3 *300e4 ) = 9.4* 10e(-14)W,即,-100 dBm

使用非常接近的范圍,例如,2 m,以及10 m2 相同的橫截面積( 例如,拖拉機后部),我們可以計算出在一定環境下能夠得到的最大Prcv。

Prcv = (0.1* 1000e2*1*.0039e2*10)/(( 4π)e3 * 2e-4) = 4.8*10e-4 W,即-3.2 dBm

這些計算告訴我們,我們的系統需要動態范圍非常高的接收器,量級在120 dB 左右。大動態范圍對接收器和模數轉換器(ADC) 線性度提出了很高的要求。但是,2 m 外很大的目標會遮擋其他目標的雷達視線。因此,可以采用模擬自動增益控制(AGC) 環來減小接收器和ADC 的動態范圍,在出現很大的回波信號時,通過衰減降低接收器的敏感度。

在要求不太高的情況下,例如,4 m 距離外1 m2 的目標,還是需要很高的靈敏度,用于探測很遠距離外的其他目標。在這種情況下,較大回波信號的接收功率是:

Prcv = (0.1*?1000e2 *1* *.0039e2*1)/(( 4π)e3 * 4e4) = 3.0* 10e-6W,即-25dBm

使用AGC 將動態范圍要求降低到大約95 dBm,使用16 位ADC 就能夠實現。為給出一定的余量,ADC 可以工作在32x 過采樣( 超出Nyquist 要求),再獲得有效的3 比特,進一步把量化噪聲基底降低18 dB。或者,采用18 位ADC,但是成本可能會高出很多。

實施時的考慮

CWFM 雷達體系結構的優勢在于,其模擬和數字實現方法都比較簡單。在模擬側,可以使用具有標準參考晶體的直接數字合成器(DDS) 來實現發送器。DDS 為鎖相環(PLL) 產生一個模擬頻率斜坡參考,以獲得所需的發送頻率調制。例如,如果PLL 的分頻器是1000,那么,在我們的例子中,參考的中心位于77 MHz,有5 MHz 頻率斜坡。這一模擬斜坡信號驅動PLL 參考,用于77 GHz 振蕩器。對電路的振蕩器輸出進行放大,產生連續波(CW) 信號,在500 MHz 內上升或者下降,其中心頻率是77 GHz。使用刻蝕在高epsilon R 介質電路卡中的無源器件可以實現77 GHz 的濾波和匹配電路,從而減少了所需的元器件數量。圖5 顯示了一個模擬電路的結構圖。

圖5. 模擬電路結構圖

在接收器中,前端需要濾波和低噪聲放大器(LNA),其后是一個正交解調器。正交解調器混合77 GHz 接收信號和斜坡發送信號,輸出一個復雜的基帶信號,它含有發送和接收波形在任意時刻的差值。抵消了斜坡,我們可以看到固定頻率取決于目標返回信號的范圍和多普勒頻移。還是可以使用刻蝕無源器件來實現77 GHz 的高頻濾波功能。正交解調器的輸出是在低頻,最大范圍是±2 MHz。因此,可以采用傳統的無源器件和運算放大器,在同相(I) 和正交(Q) ADC 之前提供抗混疊低通濾波功能。或者,采用中頻(IF) 體系結構,但是需要偏移接收LO 生成電路。

I 和Q 輸入的ADC 必須至少工作在5 MSPS 才能滿足Nyquist 標準。如果采用了40MSPS 的8x 采樣頻率,然后是8:1 數字抽取濾波器,那么,可以進一步將分辨率提高大約3 比特。這種抽取技術支持16 位ADC 高效的工作在18 位到19 位范圍內,動態范圍超過100 dB。使用16 位I 和Q 輸入采樣,數字濾波器可以工作在160 MHz,輸出采樣是5 MHz,但是取整為24 比特。信號處理的下一步是使用FFT 進行頻率識別,隨后是差值電路。

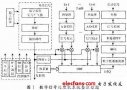

FFT 的特性是通過處理級進行處理來提高數據精度。對于我們的例子,假設2,048 點的FFT,這可能要額外的10 比特精度才能避免數據的丟失。但是,通過在單精度浮點處理中實現FFT 能夠避免這種比特的增長。通過FFT 能夠保持全24 位尾數精度(23 位加上符號),很容易實現被探測目標的100+ dB 動態范圍。遠距離和弱目標返回信號不會被近距離目標和強返回信號遮擋,因此,避免了雷達系統被較強的近距離反射信號“ 致盲”。浮點處理還能夠防止弱反射信號被“ 淹沒” 在FFT 的數字噪聲基底中。圖6 顯示了一個數字電路的結構圖。

圖6. 數字電路結構圖

浮點FFT 電路雖然只處理10 MSPS 的復數數據,但是,其時鐘也是160 MHz。采用Altera 的DSP Builder 高級工具流程,只需要很少的邏輯就能夠實現浮點電路。除了產生全浮點電路外,當時鐘速率高于數據速率時,還能夠對數據通路進行“ 折疊”,從而節省了邏輯和DSP 模塊資源,也降低了功耗。在Cyclone V SoC FPGA 中實現了這些優化措施,DSP Builder 工具自動完成時序收斂過程。低成本Cyclone V SoC FPGA還具有DSP 模塊,同時支持18 x 19 和27 x 27 乘法器。規模較大的27 x 27 乘法器適用于在浮點設計中使用。

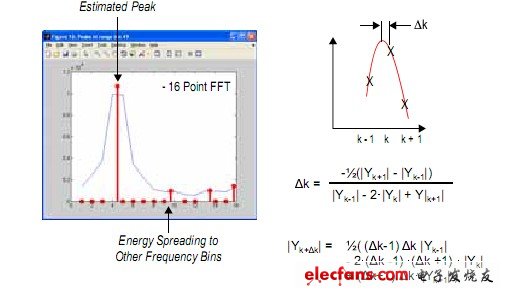

FFT 輸出插值有助于提高頻率分辨精度。如果其能量在頻率箱之間,那么插值能夠將FFT 能量混疊到其他箱中,從而防止錯過弱返回信號,如圖7 所示。

圖7.FFT 插值

可以使用一個ARM Cortex-A9 微處理器來完成探測處理。可以采用從簡單閾值到更復雜的恒定虛警率(CFAR) 等算法。能夠在邏輯中或者軟件中實現FFT 結果插值,這取決于系統設計人員的選擇。

對干擾的考慮

必須要考慮實際上有很多車輛裝備了工作在77 GHz 的雷達。迎面行駛而來的車輛上的雷達發送器可能會產生比大部分目標反射信號更強的信號。但是,發送器工作在數百MHz,特別是這個例子中的500 MHz接收器輸入帶寬在5 MHz 量級,大約是發送帶寬的1%。如果迎面而來的車輛雷達發送器掃過這一帶寬的1%,同時另一接收器也恰巧掃過這一帶寬,那么就會出現干擾。統計上,不太會經常發生這種重疊,一旦出現時,可以通過隨機調整發送斜坡時序來消除它。對于很多設備使用隨機訪問技術在共享通道上偶爾進行通信的系統,這一問題比較常見。

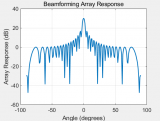

聚束

目前為止介紹的雷達系統能夠探測目標的范圍和速度,但是不能提供目標方向的任何信息,即使目標位于車輛前部,在天線波束范圍內。如果系統能夠搜索或者控制雷達發送和接收天線的方向,監視搜索時目標產生的回波變化,那么就能夠確定目標方向。

假設所描述的系統使用了拋物面天線。拋物面天線將發送或者接收到的電磁波聚焦到一個特定的方向上。聚焦角度主要取決于天線面積和波長。使用毫米波雷達減小了天線的體積。

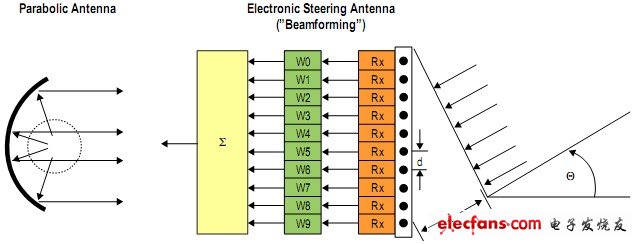

可以通過機械方式把拋物面天線“ 瞄準” 所需的方向,這主要限制在機械運動的速度,以及可靠性和成本等因素上。流行的替代方案是使用電子聚束轉向技術。在這個例子中,天線由獨立接收或者發送天線變成線性或者二維陣列。通過連續組合獨立的天線信號,合成和分解波前信號能夠大幅度提高某一方向的增益,同時減小其他方向的增益。

對于汽車雷達,雷達一般并不需要俯仰轉向( 上和下),因此,不需要兩維天線陣列。線性陣列,或者天線陣,支持對天線的方位( 側向) 進行調整。代價是成本和復雜度。

在這個例子中,調整接收方向非常簡單,這是因為對接收信號進行了數字處理。每一接收器必須單獨調整接收信號的相位。

這種相位調整技術支持對天線波束的方向調整。只有當接收信號同相到達所有天線單元時,才會出現最強信號。天線陣能夠“ 瞄準” 所需方向上天線的主波瓣。每一天線單元都有延時,或者相位調整,這樣,進行了這種調整后,所有單元都具有共同的信號相位。如果角度= 0,那么,所有單元會同時接收到信號,不需要進行相位調整。對于非零角,每一單元會有延時對天線陣的波前進行對齊,如圖8 所示。

圖8. 電動轉向天線

電動轉向天線需要復制N 個天線接收節點每一個的模擬接收器電路。好在對于毫米波雷達,包括天線罩、濾波器和匹配電路在內的大部分電路都可以直接在PCB 上實現。

對于N 個節點中的每一個,也必須復制LNA、正交解調器和ADC,對成本影響最大的可能是ADC。

對于數字電路,來自每一天線節點ADC 對的每一組I 和Q 輸入都必須有同相延時。對于N 個接收節點中的每一個,通過具有N 個獨立復數系數Wi 的復數乘法器來實現這一延時。Cyclone V SoC FPGA 的DSP 模塊非常適合用于實現這一功能,一個DSP 模塊能夠實現高速復數乘法器。控制處理器通過周期性的更新第N 個復數系數,“ 掃描” 接收天線,監視目標反射振幅的變化。還需要很少的其他FPGA DSP 模塊和邏輯資源來支持大小4 到16 的N 個節點的聚束功能。

在前向汽車雷達中,所需的方位調整角度大約只有汽車中心線的5 到10 度。對于成本效益問題,可以使用拋物面發送天線,它有很寬的天線波瓣,使用較窄的波瓣轉向接收天線,以便能夠區分不同方位上的目標。或者,采用更復雜的發送器和發送聚束天線,以提高所需發送方位上的增益,但是成本和復雜度都會增大。

多模式雷達選擇

在較短的距離范圍內,可以選擇脈沖多普勒雷達。由于脈沖多普勒雷達所使用的發送啁啾有較短的占空比,發射功率小于CWFM,因此,脈沖多普勒雷達的探測范圍較近。脈沖多普勒雷達的確具有降低探測模糊的優勢,但代價是需要較高的采樣率和信號處理速率,而且還使用了外部存儲器。例如,使用具有64 范圍箱的100 MHz (10 ns) 采樣率,可以支持大約100 m 往返距離范圍,范圍分辨率達到1.5 m。64 個發送脈沖收集響應支持多普勒探測在每一范圍上使用64 個采樣。存儲要求是64x64 = 4096 復數采樣,這必須進行存儲用于處理,需要外部DDR 存儲芯片。好在Altera SoC FPGA 含有硬核DDR 存儲器控制器。存儲器帶寬足夠寬,因此,ARM 處理子系統可以共享這一DDR,這通過DDR 控制器仲裁來實現。

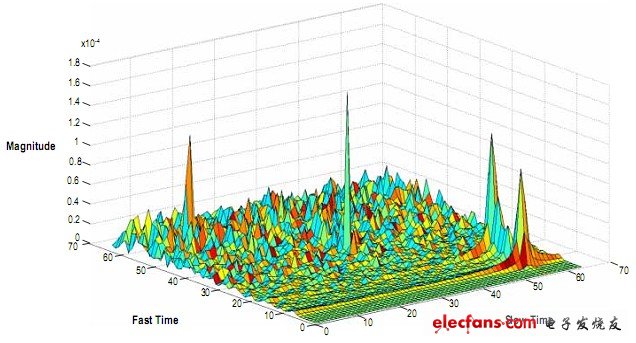

在范圍和多普勒上使用鑒別技術,能夠對所有方向上的目標進行分辨,如圖9 所示。如果采用的脈沖重復速率是250 kHz,那么,脈沖間隔是4 μs,避免了范圍問題。對于從一個脈沖返回的目標信號出現在下一PRI 的情況,需要1,200 m 或者更長的往返距離才能發生,即,600 m 的距離,衰減會導致無法探測到返回信號。對于250 kHz 的延長PRI ( 在下一發送脈沖之前,雷達在采樣每一接收間隔后會暫停),多普勒模糊也不是問題。使用浮點處理,可以得到所有范圍(“ 快” 時) 和多普勒(“ 慢” 時)的實際曲線,在軟件中完成探測處理。

圖9. 浮點脈沖多普勒目標探測

使用SoC FPGA 的優點是,通過部分重新配置功能,設備可以在幾個毫秒內從CWFM 模式轉換到脈沖多普勒雷達模式。因此,FPGA 不同時支持這兩種模式,從而節省了硬件資源。而且,部分重新配置功能支持ARM 處理子系統或者接口電路等FPGA 的其他部分在進行部分重新配置時保持工作狀態,不受影響。

FPGA 資源估算

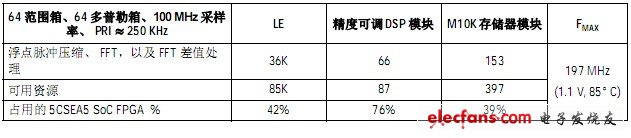

表 2 和表3 列出了Altera Quartus II 軟件估算的FPGA 資源使用情況。CWFM 設計使用的資源要比脈沖多普勒設計少得多,而且很容易在Altera 成本最低的SoC FPGA 中實現CWFM。

表2. 在Altera Cyclone V SoC FPGA 中實現CWFM 雷達

表3. 在Altera Cyclone V SoC FPGA 中實現的脈沖多普勒雷達(64 范圍箱、64 多普勒箱、100 MHz 采樣率、PRI 250 KHz)

結論

汽車傳感器系統采用了雷達、LIDAR、紅外和可視攝像機以及其他技術,今后這一系統會越來越復雜,功能也越來越多。本文介紹使用Altera 低成本Cyclone V SoC FPGA,實現典型雷達系統數字化處理的可行性。與定制ASIC 相比,這一方法的優勢在于縮短了產品面市時間,支持現場更新升級,能夠在浮點、預集成ARM Cortex-A9 雙核微處理器系統中快速方便的實現,而且還可以使用汽車級器件。這一方法支持雷達集成各種技術,實現“ 傳感器融合”,使用多個傳感系統完成對車輛控制最合理的判斷。這里雖然并沒有進一步展開傳感器融合這一概念,但是它會在今后的汽車輔助駕駛系統中扮演越來越重要的角色。

電子發燒友App

電子發燒友App

評論