現(xiàn)代社會(huì)正向數(shù)字化、信息化方向高速發(fā)展,在這一過程中,往往需要高速信號(hào)的實(shí)時(shí)性數(shù)字化處理。例如,隨著科技的進(jìn)步,現(xiàn)代雷達(dá)等應(yīng)用信號(hào)的數(shù)字化處理上有了長(zhǎng)足的發(fā)展,但也帶來了新的問題,這些應(yīng)用的數(shù)字

2019-10-17 08:27:44

Altera公司意欲通過更先進(jìn)的制程工藝和更緊密的產(chǎn)業(yè)合作,正逐步強(qiáng)化FPGA協(xié)同處理器,大幅提升SoC FPGA的整體性能,為搶攻嵌入式系統(tǒng)市場(chǎng)版圖創(chuàng)造更大的差異化優(yōu)勢(shì)。隨著SoC FPGA在

2019-08-26 07:15:50

SoC FPGA將大舉進(jìn)軍機(jī)器視覺、馬達(dá)控制和工業(yè)乙太網(wǎng)路等工廠自動(dòng)化應(yīng)用。FPGA開發(fā)商正紛紛祭出SoC設(shè)計(jì)策略,透過整合多核心CPU、數(shù)位訊號(hào)處理器和微控制器等運(yùn)算核心,強(qiáng)化處理效率并增進(jìn)高階

2019-07-03 06:07:38

先進(jìn)的設(shè)計(jì)與仿真驗(yàn)證方法成為SoC設(shè)計(jì)成功的關(guān)鍵。一個(gè)簡(jiǎn)單可行的SoC驗(yàn)證平臺(tái),可以加快SoC系統(tǒng)的開發(fā)與驗(yàn)證過程。FPGA器件的主要開發(fā)供應(yīng)商都針對(duì)自己的產(chǎn)品推出了SoC系統(tǒng)的開發(fā)驗(yàn)證平臺(tái),如

2019-10-11 07:07:07

仿真,解決了嵌入式系統(tǒng)在進(jìn)行仿真時(shí)內(nèi)存處理速度與繪圖資源消耗較大的矛盾,實(shí)現(xiàn)了對(duì)典型雷達(dá)航跡的圖形化顯示和航跡點(diǎn)坐標(biāo)的實(shí)時(shí)動(dòng)態(tài)模擬。

2019-07-10 08:11:02

` ZYNQ系列是Xilinx推出的高端嵌入式SoC,其在片上集成了ARM處理器和FPGA。ZYNQ與傳統(tǒng)的嵌入式CPU相比,具有強(qiáng)大的并行處理能力。開發(fā)人員利用FPGA強(qiáng)大的并行處理能力,不僅

2021-01-15 17:09:15

我研究了在設(shè)計(jì)中實(shí)現(xiàn)HDMI,DVI和Displayport的可行性。在這種設(shè)計(jì)中,FPGA將具有用于HDMI,DVI和DisplayPort的接收器,以接收來自外部源的信號(hào)。現(xiàn)在我不確定以下

2019-02-19 10:09:29

能量收集:在商業(yè)可行性上取得突破

2019-05-29 11:59:24

數(shù)字式雷達(dá)信號(hào)處理器系統(tǒng)組成及工作原理是什么?數(shù)字式雷達(dá)信號(hào)處理器的基本工作流程有哪些?

2021-04-21 06:36:22

,無時(shí)空限制。 ◆數(shù)字化:監(jiān)控圖像,控制及報(bào)警信息數(shù)字化后進(jìn)入計(jì)算機(jī),可以充分利用高科技手段進(jìn)行系統(tǒng)管理和圖像處理。 ◆廣域化:可以實(shí)現(xiàn)全行業(yè)大范圍內(nèi)的監(jiān)控報(bào)警聯(lián)網(wǎng)。 ◆智能化:通過監(jiān)控軟件對(duì)各種

2020-12-11 14:10:14

數(shù)據(jù)采集卡已經(jīng)成為實(shí)現(xiàn)各種數(shù)據(jù)采集、存儲(chǔ)、處理等核心單元。由于雷達(dá)回波信號(hào)通常為模擬量信號(hào),所以準(zhǔn)確地將雷達(dá)模擬量回波信號(hào)量化處理,構(gòu)建穩(wěn)定可靠的數(shù)據(jù)采集系統(tǒng),是后續(xù)數(shù)字信號(hào)分析等功能實(shí)現(xiàn)的重要前提。雷達(dá)

2016-07-01 11:47:58

可以像軟件一樣通過編程來修改。FPGA有別于DSP、ARM、MCU的地方主要在于它的并行處理能力,它的強(qiáng)大并行性使復(fù)雜的運(yùn)算得到極大的速度比提升。 SOC: 系統(tǒng)芯片是一個(gè)將計(jì)算機(jī)或其他電子系統(tǒng)

2017-04-13 08:55:14

1 引言在信息技術(shù)高速發(fā)展的今天,電子系統(tǒng)數(shù)字化已經(jīng)成為有目共睹的趨勢(shì),從傳統(tǒng)應(yīng)用中小規(guī)模芯片構(gòu)造電路系統(tǒng)到廣泛地應(yīng)用單片機(jī),到今天DSP及FPGA在系統(tǒng)設(shè)計(jì)中的應(yīng)用,電子設(shè)計(jì)技術(shù)已邁入了一個(gè)全新

2021-10-29 08:55:40

根據(jù)移動(dòng)通信技術(shù)和市場(chǎng)的發(fā)展趨勢(shì),為提升公司在LTE 技術(shù)、產(chǎn)品、人才等方面的積累,保持公司在技術(shù)、產(chǎn)品和市場(chǎng)方面的競(jìng)爭(zhēng)優(yōu)勢(shì),進(jìn)一步夯實(shí)公司未來發(fā)展的基礎(chǔ),公司擬使用超募資金1043.1萬元投資實(shí)施《LTE 網(wǎng)絡(luò)測(cè)試系統(tǒng)的基礎(chǔ)技術(shù)研究》項(xiàng)目。那LTE網(wǎng)絡(luò)測(cè)試系統(tǒng)的基礎(chǔ)技術(shù)研究究竟有哪些可行性呢?

2019-08-07 08:09:38

多個(gè) CPU 時(shí),可能是在高可靠性或高性能應(yīng)用中,PolarFire SoC FPGA 提供五個(gè)強(qiáng)化的 RISC-V 內(nèi)核。這種支持 Linux 的 SoC 具有跨內(nèi)核的一致內(nèi)存子系統(tǒng)和可配置的分支

2021-09-07 17:59:56

ADC的電源域,可估算邊帶雜散水平。 結(jié)論RF 采樣(或GSPS)ADC 可對(duì)寬帶寬進(jìn)行數(shù)字化處理,在系統(tǒng)設(shè)計(jì)方面具有獨(dú)特的優(yōu)勢(shì)。針對(duì)這些GSPS ADC,業(yè)界正在力求降低電源設(shè)計(jì)的復(fù)雜度、尺寸

2018-07-27 08:11:10

我的設(shè)計(jì)需要1天20小時(shí)才能執(zhí)行“2.7階段設(shè)計(jì)可行性檢查”。其他一切 - 從xst到bitgen- 需要2個(gè)小時(shí)。現(xiàn)在,我知道工具應(yīng)該花費(fèi)很長(zhǎng)時(shí)間才能運(yùn)行,但顯然這里有些奇怪。有什么建議,特別是

2018-10-10 11:02:39

在實(shí)際的外場(chǎng)試飛過程中是不可能實(shí)現(xiàn)的,這也是雷達(dá)信號(hào)模擬器對(duì)場(chǎng)外試飛的一大優(yōu)勢(shì)。FPGA作為高性能數(shù)字信號(hào)處理系統(tǒng)中的關(guān)鍵部件,在雷達(dá)信號(hào)模擬和雷達(dá)信號(hào)采集等方面有著巨大的開發(fā)潛能,采用這些技術(shù)對(duì)雷達(dá)

2019-07-10 07:30:35

是人們在應(yīng)用該芯片時(shí)必須解決的關(guān)鍵問題。本文提出了一種簡(jiǎn)單易行的測(cè)試方法,并在基于ADSP21062的雷達(dá)信號(hào)處理系統(tǒng)調(diào)試中獲得了成功,驗(yàn)證了該方法的可行性。

2019-07-19 08:16:35

DSP技術(shù)廣泛應(yīng)用于各個(gè)領(lǐng)域,但傳統(tǒng)的數(shù)字信號(hào)處理器由于以順序方式工作使得數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應(yīng)用目標(biāo)的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理系統(tǒng),具有很強(qiáng)的實(shí)時(shí)性和靈活性,因此利用FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理成為數(shù)字信號(hào)處理領(lǐng)域的一種新的趨勢(shì)。

2019-10-17 08:12:27

【3-5分鐘閱讀】【動(dòng)態(tài)Flash的可行性】新加坡公司Unisantis上月發(fā)表了一篇論文,描述了對(duì)"動(dòng)態(tài)閃存(DFM)"的研究,這是一種混合設(shè)備,結(jié)合了動(dòng)態(tài)RAM和Flash

2021-07-26 07:16:48

盡可能短、實(shí)驗(yàn)成本盡可能低,最好能在實(shí)驗(yàn)室直接驗(yàn)證設(shè)計(jì)的準(zhǔn)確性和可行性,因而出現(xiàn)了現(xiàn)場(chǎng)可編程邏輯門陣列FPGA。對(duì)于芯片設(shè)計(jì)而言,FPGA的易用性不僅使得設(shè)計(jì)更加簡(jiǎn)單、快捷,并且節(jié)省了反復(fù)流片驗(yàn)證的巨額成本。對(duì)于某些小批量應(yīng)用的場(chǎng)合,甚至可以直接利用FPGA實(shí)現(xiàn),無需再去訂制專門的數(shù)字芯片。

2019-08-30 08:26:38

功能和時(shí)序仿真,仿真結(jié)果驗(yàn)證了設(shè)計(jì)的正確性和可行性。關(guān)鍵詞:Delta變換型UPS;現(xiàn)場(chǎng)可編程門陣列;正弦脈寬調(diào)制;逆變器

2019-06-21 07:53:14

模數(shù)轉(zhuǎn)換、FFT快速、準(zhǔn)確的要求,并且具有高度集成、高可靠性和可編程等特點(diǎn),減少了系統(tǒng)硬件開發(fā)周期,所以選用基于FPGA來實(shí)現(xiàn)雷達(dá)信號(hào)處理系統(tǒng)的設(shè)計(jì)。回映電子是一家基于Edge-AI技術(shù)的個(gè)護(hù)健康

2021-12-27 17:08:50

1.必要性分析隨著數(shù)字芯片處理能力的不斷提高,當(dāng)今的通信系統(tǒng)和雷達(dá)系統(tǒng)的結(jié)構(gòu)已經(jīng)轉(zhuǎn)向具有模擬和強(qiáng)大數(shù)字處理功能的混合系統(tǒng)。系統(tǒng)中,數(shù)字信號(hào)處理部分完成的功能越來越多,廣泛應(yīng)用于發(fā)射信號(hào)建立和接收信號(hào)的解調(diào)處理等功能。高性能ADC/DAC器件和FPGA技術(shù)的進(jìn)步也大大擴(kuò)展了數(shù)字電路的功能和性能。

2019-07-19 07:44:42

在實(shí)際的外場(chǎng)試飛過程中是不可能實(shí)現(xiàn)的,這也是雷達(dá)信號(hào)模擬器對(duì)場(chǎng)外試飛的一大優(yōu)勢(shì)。FPGA作為高性能數(shù)字信號(hào)處理系統(tǒng)中的關(guān)鍵部件,在雷達(dá)信號(hào)模擬和雷達(dá)信號(hào)采集等方面有著巨大的開發(fā)潛能,采用這些技術(shù)對(duì)雷達(dá)

2019-07-15 06:48:33

RAM)的FIFO模塊設(shè)計(jì)和電平判定檢測(cè)設(shè)計(jì)。 由于接收機(jī)設(shè)計(jì)的目的是正確實(shí)時(shí)地處理輸進(jìn)數(shù)據(jù),高速A/D的輸出必須由高速數(shù)字電路處理,否則數(shù)字化后的數(shù)據(jù)就會(huì)丟失,或者系統(tǒng)只能工作在非實(shí)時(shí)模式,所以

2018-08-15 09:43:14

集成化程度的提高,不僅可使系統(tǒng)的體積變小、重量減輕、功耗降低,更重要的是可使系統(tǒng)的可靠性大大地提高,因此電子系統(tǒng)日趨數(shù)字化、復(fù)雜化和大規(guī)模集成化。而由于可編程邏輯器件(如FPGA、CPLD)是一種數(shù)字

2019-07-12 08:32:59

的通話質(zhì)量進(jìn)行評(píng)估,并對(duì)ZigBee網(wǎng)絡(luò)的語(yǔ)音應(yīng)急通信的可行性進(jìn)行了分析和研究。結(jié)果表明在節(jié)點(diǎn)間通信少于兩跳及無線鏈路質(zhì)量較好的情況下,ZigBee網(wǎng)絡(luò)能夠提供語(yǔ)音服務(wù)。 關(guān)鍵詞: ZigBee

2009-09-19 09:25:14

無論用做獨(dú)立的處理單元,或者與輔助處理器聯(lián)合使用,SoC FPGA器件均可以改善嵌入式處理的安全性。雖然可以利用專用安全器件來構(gòu)建嵌入式處理器模塊,實(shí)施監(jiān)測(cè)和靜態(tài)密匙存儲(chǔ),然而,整合系統(tǒng)關(guān)鍵功能的SoC FPGA器件若能提供安全特性,便可以提供更大的安全性、靈活性和更好的性能。

2019-06-19 06:57:45

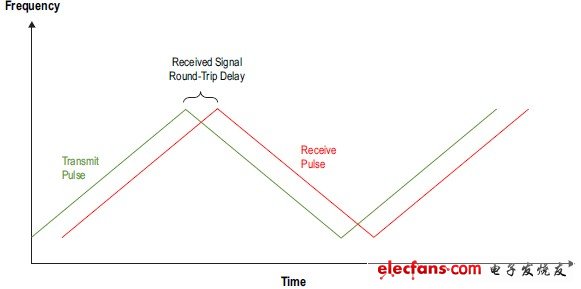

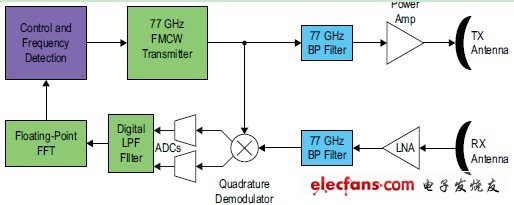

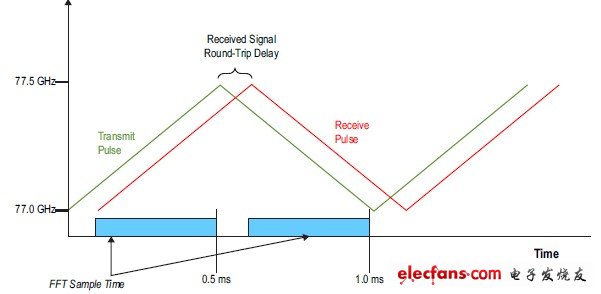

使用SoC FPGA,實(shí)現(xiàn)汽車雷達(dá)的數(shù)字化處理本白皮書介紹使用Altera? 低成本Cyclone? V SoC FPGA,實(shí)現(xiàn)典型雷達(dá)系統(tǒng)數(shù)字化處理的可行性。與定制ASIC 相比,這一方法的優(yōu)勢(shì)

2013-11-13 15:56:28

本文以FPGA為核心構(gòu)建了一種通用的雷達(dá)回波信號(hào)實(shí)時(shí)模擬系統(tǒng)。該系統(tǒng)采用FPGA作為回波信號(hào)模擬的運(yùn)算單元,充分利用了FPGA資源豐富、并行處理能力強(qiáng)的特點(diǎn),提高了系統(tǒng)的實(shí)時(shí)性;采用System

2021-04-29 06:14:20

FPGA是新型的可編程邏輯器件,能夠?qū)⒋罅康倪壿嫻δ芗捎趩蝹€(gè)器件中,它所提供的門數(shù)從幾百門到上百萬門,符合系統(tǒng)芯片(SOC—System On Chip)的發(fā)展要求,具有高度集成、低功耗、硬件升級(jí)

2019-08-01 06:56:06

微波電磁環(huán)境測(cè)試系統(tǒng)是由哪些部分組成的?如何去測(cè)試微波電磁環(huán)境測(cè)試系統(tǒng)的可行性?

2021-05-25 06:11:15

形式進(jìn)行采集和存儲(chǔ),便于壓縮,分析,處理和顯示,抗干擾能力強(qiáng),適合網(wǎng)絡(luò)傳輸。因此,數(shù)字化是視頻監(jiān)控系統(tǒng)的發(fā)展方向。傳統(tǒng)的視頻處理系統(tǒng)為了滿足實(shí)時(shí)性和靈活的實(shí)際接口需要,多采用FPGA+ DSP或者

2019-08-02 06:18:40

定速空調(diào)改為變頻空調(diào)的可行性。有網(wǎng)友能提供技術(shù)方案,供相互探討?

2009-05-21 18:39:02

對(duì)基帶信號(hào)進(jìn)行數(shù)字化處理時(shí)為什么需使用輸入濾波器?

2023-12-21 06:55:35

來至網(wǎng)友的提問:對(duì)基帶信號(hào)進(jìn)行數(shù)字化處理時(shí)為什么需使用輸入濾波器?

2018-12-12 09:07:39

本文詳細(xì)介紹了自行設(shè)計(jì)適合自身需要的虛擬儀器的全過程。實(shí)現(xiàn)了自制虛擬儀器的可行性、經(jīng)濟(jì)性、快速性和便攜性。

2021-04-15 06:16:12

可以阻塞回復(fù),也可以異步方式通過回讀確定上次寫效果是否實(shí)現(xiàn)。方法二:在esp32上實(shí)現(xiàn)modbusTCP slave轉(zhuǎn)modbus RTU master的功能,但這樣效率肯定不高。延遲厲害。所以重點(diǎn)談?wù)摲椒?的可行性。

2022-08-16 11:23:45

◆ 強(qiáng)大的PC端軟件Signal Explorer ◆ NI公司LabVIEW DAQmx USB接口 ◆ USB連接電腦主機(jī)cw工作模式FSK工作模式FMCW工作模式常見運(yùn)用: ◆ 開發(fā)數(shù)據(jù)處理算法 ◆ 信號(hào)分析及記錄 ◆ 學(xué)習(xí)、探索雷達(dá)原理 ◆ 評(píng)估項(xiàng)目應(yīng)用可行性,協(xié)助產(chǎn)品選型

2015-01-20 17:10:23

樓主一個(gè)朋友做大功率LED,最近想做一個(gè)檢測(cè)LED的電流的小東西,采集電能等參數(shù),通過433或GPRS無線發(fā)送出去,以此判斷燈的好壞,要求小型化。求可行性的方案,關(guān)鍵是盡量小型化,穩(wěn)定可靠。

2019-03-21 03:06:13

目前基于FPGA和DSP結(jié)構(gòu)的軟件無線電技術(shù)被廣泛應(yīng)用在數(shù)字接收機(jī)設(shè)計(jì)中,雷達(dá)接收機(jī)領(lǐng)域的數(shù)字化技術(shù)也在日趨發(fā)展,如何借助數(shù)字化的軟硬件優(yōu)勢(shì)設(shè)計(jì)出易實(shí)現(xiàn)、靈活,并滿足不同性能指標(biāo)和目的的數(shù)字接收機(jī)成為工程設(shè)計(jì)的焦點(diǎn)。

2019-08-16 06:42:07

交通系統(tǒng)中發(fā)揮的作用。重點(diǎn)討論了毫米波雷達(dá)感知技術(shù)的原理與功能,研究以毫米波雷達(dá)為主要感知設(shè)備搭建車路協(xié)同系統(tǒng)的可行性,研究毫米波雷達(dá)技術(shù)在智能交叉路口、智能高速 / 快速公路、智能停車場(chǎng)三種車路協(xié)同

2020-07-01 14:16:38

電子設(shè)計(jì)競(jìng)賽的可行性2.1 學(xué)生具備了一定的計(jì)算機(jī)操作基礎(chǔ)。現(xiàn)在的學(xué)生從小學(xué)、初中開始就學(xué)習(xí)電腦知識(shí),他們擁有...

2021-07-19 08:04:19

各位大神 小弟初來乍到,有一個(gè)問題一直困惑不解,作為電容這樣的儲(chǔ)能元件,在某種意義上說是可以充當(dāng)電池使用的,在一些電路中也有這樣的應(yīng)用(小型時(shí)鐘電路),小弟有這樣一個(gè)設(shè)想不知可否用電容替代一些小型便攜設(shè)備的電源,比如mp3、手機(jī)之類的,是否具有可行性。求各位大神指點(diǎn)

2013-08-11 18:21:10

上以數(shù)字通信方式取代“硬連接”方式接入并挖掘、增強(qiáng)現(xiàn)有電氣系統(tǒng)的功能,即研制電廠電氣監(jiān)控管理系統(tǒng)是未來的發(fā)展趨勢(shì)。 2、發(fā)電廠電氣監(jiān)控管理的可行性 近年來,微機(jī)自動(dòng)化技術(shù)已經(jīng)在電力系統(tǒng)的高、中

2020-12-04 15:05:12

雷達(dá)系統(tǒng)該如何向認(rèn)知化和數(shù)字化方向發(fā)展?

2021-04-06 07:51:18

路面檢測(cè)方案比較及可行性分析 環(huán)境圖像采集部分可以采用陣列紅外探頭和CCD或CMOS圖像傳感器來實(shí)現(xiàn),前者的特點(diǎn)是價(jià)格低廉、電路簡(jiǎn)單、應(yīng)用方便,缺點(diǎn)是性能有限,對(duì)復(fù)雜環(huán)境的適應(yīng)能力較弱,效果較差

2011-07-12 15:26:33

inetis系列MCU都具有secure功能,可防止代碼被外部調(diào)試器被惡意讀取或者破解,而在本文中將介紹如何在secure狀態(tài)下,利用實(shí)現(xiàn)加載加密可行性文件的過程,這也是KBOOT v2.0新功能,BB到這吧,上文檔。

2016-08-22 15:19:29

運(yùn)放并聯(lián)的可行性并聯(lián)運(yùn)放以獲取雙倍輸出電流是可行的嗎?

2021-04-06 07:11:50

簡(jiǎn)析運(yùn)放并聯(lián)的可行性

2021-03-18 08:06:57

全部:我目前正在探索通過Virtex 5 FPGA上的SATA連接將數(shù)據(jù)流式傳輸?shù)紿DD或SSD的可行性。我很難找到如何做到這一點(diǎn)的示例,或者它是否可行。到目前為止,我已經(jīng)找到

2020-06-02 06:28:15

討論了合金相圖信息的存儲(chǔ)、處理,用VB 6.0編程工具作為系統(tǒng)開發(fā)平臺(tái),建立了合金平衡相圖的數(shù)字化處理系統(tǒng)軟件。該系統(tǒng)軟件用于合金平衡相圖中相和組織組成物的定量計(jì)算

2008-11-15 21:03:39 13

13 嵌人式飛行參數(shù)傳感系統(tǒng)的設(shè)計(jì)與可行性驗(yàn)證

摘要: 簡(jiǎn)要介紹了嵌入式飛行參數(shù)傳感系統(tǒng)( F A D S ) 的空氣動(dòng)力學(xué)模型, 并以美國(guó)的X - 3 3飛行器為例, 詳細(xì)描述了該系統(tǒng)的算

2009-05-07 10:40:57 21

21 電視信號(hào)的實(shí)時(shí)監(jiān)測(cè)與數(shù)字化處理:基于射頻和視頻指標(biāo)的測(cè)量將模擬視頻信號(hào)數(shù)字化, 對(duì)采樣數(shù)據(jù)進(jìn)行處理,判斷和識(shí)別,并對(duì)異常狀態(tài)進(jìn)行報(bào)警和記錄,構(gòu)成了一套對(duì)電視信號(hào)進(jìn)

2009-06-22 19:14:38 14

14 基于FPGA 的SOC 系統(tǒng)中的串口設(shè)計(jì)

作者:葛銳 歐鋼摘要:本文在XILINX FPGA 中采用嵌入式處理器Picoblaze 進(jìn)行SOC 設(shè)計(jì),以較少的

2010-02-08 09:48:37 21

21

針對(duì)AGVS(自動(dòng)導(dǎo)引小車系統(tǒng))柔性問題的研究現(xiàn)狀,為了解決AGVS柔性可行性的判斷問題,提出了一種處理因生產(chǎn)任務(wù)臨時(shí)調(diào)整而引起的AGVS路線調(diào)整的可行性判斷方法,并給出了該

2010-02-22 14:40:22 47

47 論文對(duì)數(shù)字化技術(shù)在雷達(dá)中的應(yīng)用(雷達(dá)數(shù)字化技術(shù))發(fā)展以及雷達(dá)數(shù)字化技術(shù)

研究方法進(jìn)行了全面綜述,指出了雷達(dá)數(shù)字化包括用數(shù)字部件代替大部分模擬部件,

雷達(dá)

2010-08-12 17:18:52 25

25 FreeDev數(shù)字圖象開發(fā)套件是低成本FPGA器件上的高速數(shù)字化視頻圖象開發(fā)平臺(tái),為應(yīng)用設(shè)計(jì)工程師提供了一個(gè)視頻數(shù)據(jù)采集、數(shù)字化處理、網(wǎng)絡(luò)傳輸視頻圖象開發(fā)實(shí)驗(yàn)平臺(tái)。

2011-05-09 10:45:02 2431

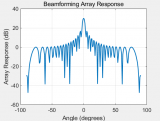

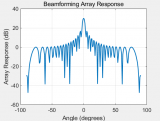

2431 本文提出了一種基于FPGA的雷達(dá)數(shù)字信號(hào)處理機(jī)設(shè)計(jì),接收機(jī)采用了脈沖多普勒、數(shù)字波束形成等主流雷達(dá)技術(shù)。

2012-03-31 09:53:13 2559

2559

SoC FPGA使用寬帶互聯(lián)干線鏈接,在FPGA架構(gòu)中集成了基于ARM的硬核處理器系統(tǒng)(HPS),包括處理器、外設(shè)和存儲(chǔ)器接口。Cyclone V SoC FPGA在一個(gè)基于ARM的用戶可定制芯片系統(tǒng)(SoC)中集成了

2012-09-04 14:18:14 4604

4604

白皮書介紹使用Altera?低成本 Cyclone? V SoC FPGA,實(shí)現(xiàn)典型雷達(dá)系統(tǒng)數(shù)字化處理的可行性。與定制ASIC 相比,這一方法的優(yōu)勢(shì)在于縮短了產(chǎn)品面市時(shí)間,支持現(xiàn)場(chǎng)現(xiàn),而且還可以使用汽車級(jí)器

2013-10-10 21:09:24 0

0 基于FPGA的雷達(dá)信號(hào)處理系統(tǒng)設(shè)計(jì)的論文

2015-10-30 10:38:12 6

6 基于DSP_FPGA的LFMCW雷達(dá)測(cè)距信號(hào)處理系統(tǒng)設(shè)計(jì)_陳林軍

2017-03-19 19:07:17 4

4 基于FPGA的導(dǎo)流葉片角度數(shù)字化測(cè)量系統(tǒng)_潘瑨

2017-03-19 19:08:35 0

0 基于Cortex_A8和FPGA的嵌入系統(tǒng)在雷達(dá)信號(hào)處理中的應(yīng)用

2017-10-26 08:27:50 3

3 近年來,雷達(dá)在軍用和民用領(lǐng)域都獲得了巨大的發(fā)展。雷達(dá)信號(hào)處理系統(tǒng)是雷達(dá)的關(guān)鍵模塊,對(duì)雷達(dá)定位精度起著決定性作用。FPGA 以其眾多的優(yōu)點(diǎn),在雷達(dá)信號(hào)處理系統(tǒng)中被廣泛使用。本文探究FPGA 在雷達(dá)信號(hào)

2017-11-22 07:25:02 4251

4251

現(xiàn)代社會(huì)正向數(shù)字化、信息化方向高速發(fā)展,在這一過程中,往往需要高速信號(hào)的實(shí)時(shí)性數(shù)字化處理。例如,隨著科技的進(jìn)步,現(xiàn)代雷達(dá)等應(yīng)用信號(hào)的數(shù)字化處理上有了長(zhǎng)足的發(fā)展,但也帶來了新的問題,這些

2018-07-17 10:28:00 1982

1982

在處理器、邏輯單元和存儲(chǔ)器等三種硬件中進(jìn)行選擇,而現(xiàn)在這些器件已合并為單一的SoC解決方案。 SoC面臨的挑戰(zhàn)嵌入式系統(tǒng)SoC可采用現(xiàn)場(chǎng)可編程門陣列(FPGA)或?qū)S眉呻娐?ASIC)實(shí)現(xiàn)。

2017-11-24 08:24:01 1080

1080 在運(yùn)行時(shí)進(jìn)行調(diào)整以適應(yīng)環(huán)境和運(yùn)行要求,這使得雷達(dá)系統(tǒng)需要向認(rèn)知化和數(shù)字化發(fā)展。 更多數(shù)字信號(hào)處理的需求推動(dòng)雷達(dá)信號(hào)鏈要盡早向數(shù)字化過渡,使得ADC更靠近天線,這進(jìn)而又會(huì)帶來若干具挑戰(zhàn)性的系統(tǒng)層面難題。

2018-04-22 18:08:00 1138

1138

雷達(dá)目標(biāo)檢測(cè)與信息錄取是雷達(dá)系統(tǒng)與雷達(dá)信號(hào)處理系統(tǒng)的重要組成部分,超大規(guī)模集 成電路的發(fā)展,特別是高性能的信號(hào)處理器(DSP)架構(gòu)的提升和大規(guī)模可編程邏輯器件的 出現(xiàn),為雷達(dá)信號(hào)數(shù)字化處理帶來了新的突破。

2019-04-26 08:09:00 1839

1839

圖像預(yù)處理結(jié)構(gòu),該結(jié)構(gòu)具有良好的擴(kuò)展性,并能克服因級(jí)聯(lián)而產(chǎn)生的時(shí)序問題。基于這種結(jié)構(gòu),在FPGA中實(shí)現(xiàn)了典型的LoG邊緣檢測(cè)算法與中值濾波算法。實(shí)驗(yàn)表明了這種預(yù)處理結(jié)構(gòu)的有效性和算法的可行性, 并能滿足視覺處理的實(shí)時(shí)性要求。

2018-12-13 17:56:52 37

37 AN-807: 多載波WCDMA的可行性

2021-03-21 02:13:27 7

7 數(shù)字接收處理:是指通過對(duì)接收到的信號(hào)進(jìn)行數(shù)字化處理,如濾波、檢測(cè)、跟蹤、識(shí)別等,以提高雷達(dá)的性能和功能。

2023-08-17 10:05:35 2444

2444

——Rd-03和Rd-04,三款模組主打高性能與高性價(jià)比,低成本幫助用戶實(shí)現(xiàn)產(chǎn)品的智能化升級(jí),擁有極具競(jìng)爭(zhēng)力的性能優(yōu)勢(shì)與廣闊的應(yīng)用前景等優(yōu)點(diǎn)。 安信可雷達(dá)模組問題集錦 01無人車應(yīng)用可行性? 我們做的毫米波雷達(dá)模組主要應(yīng)用于室內(nèi)場(chǎng)景,這個(gè)和模組硬件及軟件

2023-09-05 15:42:43 301

301 電子發(fā)燒友網(wǎng)站提供《船載USB系統(tǒng)跟蹤數(shù)傳信號(hào)可行性研究.pdf》資料免費(fèi)下載

2023-10-24 10:51:15 0

0 電子發(fā)燒友網(wǎng)站提供《使用SoC FPGA,實(shí)現(xiàn)汽車雷達(dá)的數(shù)字化處理.pdf》資料免費(fèi)下載

2023-11-10 10:52:45 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論