1.引言

本文針對(duì)紅外圖像處理系統(tǒng)的實(shí)時(shí)性要求,提出了基于DSP+FPGA+ASIC的圖像處理架構(gòu)。

隨著紅外焦

2010-07-22 15:18:50 796

796 由于受到無線傳輸帶寬的限制, 無人機(jī)對(duì)地面目標(biāo)偵察獲得的高分辨率視頻圖像必須經(jīng)過有效壓縮才能實(shí)時(shí)傳輸給地面接收處理系統(tǒng)。現(xiàn)有的視頻壓縮標(biāo)準(zhǔn)有H.261、H. 262、H . 263 及MPEG-

2011-10-11 18:20:42 1170

1170

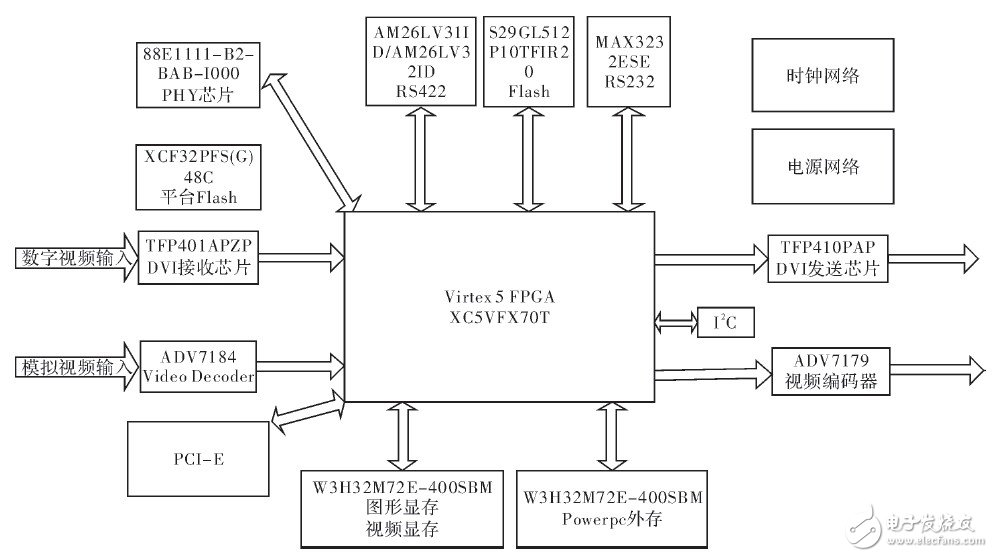

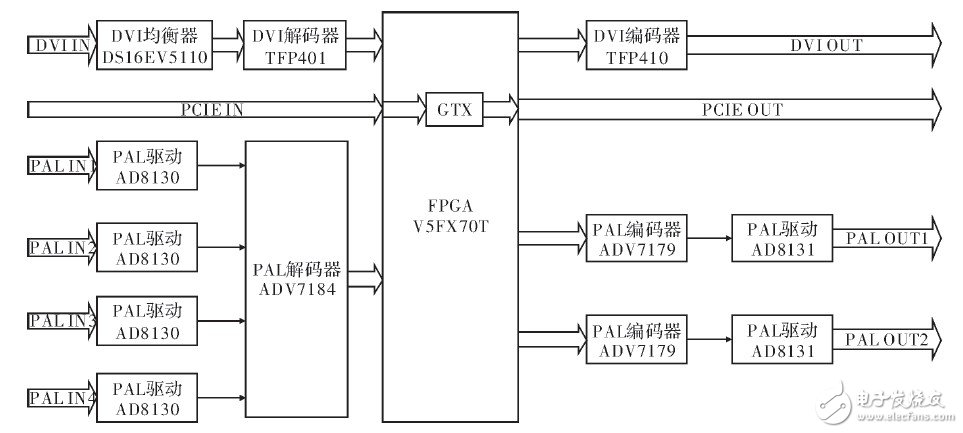

本文以FPGA作為核心處理器,提出了一種基于FPGA多路機(jī)載冗余圖像處理系統(tǒng)的設(shè)計(jì)方案。##整個(gè)系統(tǒng)顯示的分辨率為1600×1200@60 Hz,信號(hào)位為真彩色24b,則一幀圖像所需需要存儲(chǔ)的容量C≈47 Mb。##讀寫操作交替進(jìn)行仿真圖如圖5所示。圖5中包含了兩個(gè)寫入操作,一個(gè)讀取操作。

2014-01-07 10:28:32 2802

2802

設(shè)計(jì)了一種基于FPGA的實(shí)時(shí)視頻圖像采集處理電路系統(tǒng)。采用FPGA作為整個(gè)系統(tǒng)的控制和圖像數(shù)據(jù)處理中心。DDR2 SDRAM為高速儲(chǔ)存模塊核心器件,CMOS 7670為視頻圖像采集器件。

2018-02-10 02:43:55 19311

19311

來說,濾除噪聲、擴(kuò)展對(duì)比度、銳化以及色彩增強(qiáng)等處理能顯著提升視覺效果。這里設(shè)計(jì)一個(gè)基于FPGA的實(shí)時(shí)視頻圖像處理系統(tǒng),包含增強(qiáng)對(duì)比度擴(kuò)展和色飽和度兩種處理方法,相比于DSP和ASIC方案來說,FPGA在性能和靈活性方面具有絕對(duì)優(yōu)勢(shì),應(yīng)用FPGA設(shè)計(jì)視頻通信系統(tǒng)更普遍。

2019-08-22 08:22:29

Vision開發(fā)平臺(tái),它使不熟悉FPGA的機(jī)器視覺專家也能簡(jiǎn)單地操作這個(gè)系統(tǒng)。Silicon Software開發(fā)的Visual Applets為最先進(jìn)的FPGA設(shè)計(jì)工具,經(jīng)由易學(xué)易用的圖形接口,可以開發(fā)

2019-05-05 08:30:00

無法設(shè)計(jì)出具有自主知識(shí)產(chǎn)權(quán)的產(chǎn)品。隨著網(wǎng)絡(luò)技術(shù)、大規(guī)模,超太規(guī)模集成電路(ASIC)以及現(xiàn)場(chǎng)可編程門陣列(FPGA)的發(fā)展,它們?cè)趫D像領(lǐng)域的應(yīng)用越來越廣泛,同時(shí),圖像處理設(shè)計(jì)也正朝著速度快、容量大、體積小、重量輕的方向發(fā)展,這也為圖像處理系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn)提供了新的方法和思路。

2019-07-05 07:05:13

和科研單位尚未見有自主知識(shí)產(chǎn)權(quán)的研究成果或產(chǎn)品出現(xiàn),本文討論了以DSP為核心構(gòu)建數(shù)字音頻處理系統(tǒng)時(shí)需注意的幾個(gè)問題,分析自行研制的以DSP56364為核心的吉他音效處理系統(tǒng).

2011-03-06 22:28:27

為什么要推出DM642型處理器?DM642的EDMA控制器是什么?它有什么功能?EDMA的控制機(jī)制是怎樣的?EDMA是如何進(jìn)行傳輸操作的?EDMA在實(shí)時(shí)圖像處理系統(tǒng)中有哪些應(yīng)用?

2021-04-19 10:27:02

接下來,我會(huì)開一系列學(xué)習(xí)使用MATLAB來設(shè)計(jì)FPGA為DSP的過程實(shí)時(shí)信號(hào)處理系統(tǒng)要求必須具有處理大數(shù)據(jù)量的能力,以保證系統(tǒng)的實(shí)時(shí)性;其次對(duì)系統(tǒng)的體積、功耗、穩(wěn)定性等也有較嚴(yán)格的要求。實(shí)時(shí)信號(hào)處理

2015-06-01 11:47:36

設(shè)計(jì),從而能夠提高算法效率,同時(shí)其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級(jí),適合于實(shí)時(shí)視頻圖像處理。系統(tǒng)采用模塊化的設(shè)計(jì)方法,將整個(gè)系統(tǒng)劃分為三部分:視頻采集單元、視頻處理單元和視頻傳輸單元。整個(gè)系統(tǒng)以FPGA作為

2019-07-01 07:38:06

為解決高速數(shù)字圖像處理系統(tǒng)和實(shí)時(shí)性相沖突的要求,設(shè)計(jì)了以多DSP(數(shù)字信號(hào)處理器TMS320C6416)和現(xiàn)場(chǎng)可編程門陣列(FPGA)相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng)。重點(diǎn)介紹了該系統(tǒng)的硬件資源選擇、基本組

2021-04-28 06:14:48

,并且將處理后的視頻信息按照不同的要求輸出到顯示器上。 高清視頻處理模塊系統(tǒng)結(jié)構(gòu) 高清視頻處理模塊內(nèi)部包含圖形處理器,它接收顯示命令和數(shù)據(jù),加速渲染圖形畫面,輸出為高清視頻信號(hào),在FPGA中運(yùn)算融合外

2018-11-07 10:42:22

。 整個(gè)系統(tǒng)以FPGA作為核心控制單元并完成視頻信號(hào)的中值濾波工作;以DSP作為整個(gè)系統(tǒng)的核心處理單元對(duì)采集的視頻圖像信息進(jìn)行JPEG壓縮;在視頻傳輸單元設(shè)計(jì)了以PDIUSBD12芯片為基礎(chǔ)的USB總線,負(fù)責(zé)視頻信號(hào)的傳輸。

2019-06-28 08:10:26

三維圖像信息處理一直是圖像視頻處理領(lǐng)域的熱點(diǎn)和難點(diǎn),目前國內(nèi)外成熟的三維信息處理系統(tǒng)不多,已有的系統(tǒng)主要依賴高性能通用PC完成圖像采集、預(yù)處理、重建、構(gòu)型等囊括底層和高層的處理工作。三維圖像處理

2019-06-24 06:11:03

圖像數(shù)據(jù)處理的工作原理是什么?基于FPGA+DSP的圖像處理系統(tǒng)待如何去設(shè)計(jì)?

2021-06-02 06:54:28

。 整個(gè)系統(tǒng)以FPGA作為核心控制單元并完成視頻信號(hào)的中值濾波工作;以DSP作為整個(gè)系統(tǒng)的核心處理單元對(duì)采集的視頻圖像信息進(jìn)行JPEG壓縮;在視頻傳輸單元設(shè)計(jì)了以PDIUSBD12芯片為基礎(chǔ)的USB總線,負(fù)責(zé)視頻信號(hào)的傳輸。

2019-06-19 06:12:05

DSP芯片組成并行處理系統(tǒng)。另外,為充分發(fā)揮 DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì)及FPGA在大數(shù)據(jù)量的底層算法上的優(yōu)勢(shì),設(shè)計(jì)了一種基于FPGA控制的多DSP并行處理系統(tǒng)。1 系統(tǒng)設(shè)計(jì)基于FPGA控制的多

2019-05-21 05:00:19

基于FPGA的機(jī)載顯示系統(tǒng)該如何去設(shè)計(jì)?如何對(duì)機(jī)載顯示系統(tǒng)進(jìn)行優(yōu)化?

2021-06-01 06:04:12

吞吐量大、功耗低的需求,因此選擇DDR3 SDRAM作為機(jī)載視頻圖形顯示系統(tǒng)的外部存儲(chǔ)器。本文以Kintex-7系列XC7K410T FPGA芯片和兩片MT41J128M16 DDR3 SDRAM芯片為硬件平臺(tái),設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的視頻圖形顯示系統(tǒng)的DDR3多端口存儲(chǔ)管理。

2019-06-24 06:07:53

本帖最后由 lee_st 于 2017-10-31 08:26 編輯

基于FPGA的視頻圖像處理系統(tǒng)

2017-10-30 17:26:16

基于FPGA的視頻圖像處理系統(tǒng)

2015-05-27 20:34:49

基于FPGA的視頻圖像處理系統(tǒng)。

2015-05-23 12:18:23

基于fpga的實(shí)時(shí)視頻處理系統(tǒng)難點(diǎn)在哪,解決方案,誰能幫下忙

2014-04-08 19:03:45

基于DM643的嵌入式實(shí)時(shí)視頻處理系統(tǒng)的硬件設(shè)計(jì)基于DM643的嵌入式實(shí)時(shí)視頻處理系統(tǒng)的軟件設(shè)計(jì)

2021-06-04 06:54:09

和可編程邏輯器件XC2S300E為核心的圖象處理系統(tǒng)的硬件實(shí)現(xiàn)方案以及通過DSP對(duì)FPGA芯片的動(dòng)態(tài)配置來實(shí)現(xiàn)軟件控制的設(shè)計(jì)思路。 關(guān)鍵詞:可編程邏輯器件;數(shù)宇信號(hào)處理器;數(shù)字圖象處理;動(dòng)態(tài)配置dsp 可編程邏輯器件 數(shù)宇信號(hào)處理器 數(shù)字圖象處理 動(dòng)態(tài)配置

2012-12-19 11:05:08

本文設(shè)計(jì)了一個(gè)具有數(shù)字化、信息化特征的心電信號(hào)處理系統(tǒng)。該系統(tǒng)以 32 位高速 ARM 處理器為硬件平臺(tái),以實(shí)時(shí)操作系統(tǒng)作為軟件平臺(tái),對(duì)硬件系統(tǒng)的資源進(jìn)行了調(diào)度和分配,達(dá)到了對(duì)心電信號(hào)進(jìn)行實(shí)時(shí)處理的效果,并且實(shí)現(xiàn)了對(duì)心電信號(hào)的實(shí)時(shí)顯示、實(shí)時(shí)存儲(chǔ)等功能。

2019-09-16 09:00:13

光電跟蹤系統(tǒng)在實(shí)戰(zhàn)環(huán)境中,針對(duì)復(fù)雜場(chǎng)景下快速運(yùn)動(dòng)目標(biāo)實(shí)施實(shí)時(shí)跟蹤的魯棒性與穩(wěn)定性,筆者提出以雙DSP和FP-GA為核心來構(gòu)建主從式超高速并行處理體系的設(shè)計(jì)思想,并研究開發(fā)了基于雙DSP的新型柔性機(jī)載實(shí)時(shí)

2019-07-02 06:57:27

:給出了以兩片高性能TMS320C6414作為核心處理器,并輔以FPGA來實(shí)現(xiàn)系統(tǒng)邏輯時(shí)序控制,從而組成雙DSP柔性機(jī)載實(shí)時(shí)圖像處理系統(tǒng)的設(shè)計(jì)方案。同時(shí)對(duì)系統(tǒng)的硬件資源選擇及工作流程進(jìn)行了討論。&

2008-09-05 08:40:02

利用可見光成像與紅外成像傳感器實(shí)現(xiàn)實(shí)時(shí)目標(biāo)成像跟蹤是精確制導(dǎo)武器及機(jī)載成像光電系統(tǒng)研究的核心技術(shù)。伴隨著實(shí)戰(zhàn)環(huán)境日益復(fù)雜以及偽裝、隱身等目標(biāo)特性控制技術(shù)的飛速發(fā)展,機(jī)載實(shí)時(shí)圖像跟蹤系統(tǒng)的應(yīng)用也日益廣泛與深入。當(dāng)跟蹤目標(biāo)并非一般地面慢速目標(biāo),而是其它快速運(yùn)動(dòng)目標(biāo)?

2019-09-03 07:06:05

如果圖像處理系統(tǒng)的輸入為復(fù)合模擬視頻,幀頻25 Hz;輸出為XGA格式,幀頻60 Hz;一幅輸入畫面平均產(chǎn)生2.4次輸出畫面,此時(shí)系統(tǒng)處理的就是異步視頻,有3種處理方法:幀內(nèi)不同步方法、幀間不同步方法和準(zhǔn)同步方法。

2020-04-09 07:22:16

如何在嵌入式視頻處理系統(tǒng)領(lǐng)域進(jìn)行FPGA驗(yàn)證?需要滿足什么條件?

2019-08-01 06:42:45

隨著紅外探測(cè)技術(shù)迅猛的發(fā)展,當(dāng)今紅外實(shí)時(shí)圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時(shí),有時(shí)就顯得有些捉襟見肘了

2019-11-08 06:31:26

形式進(jìn)行采集和存儲(chǔ),便于壓縮,分析,處理和顯示,抗干擾能力強(qiáng),適合網(wǎng)絡(luò)傳輸。因此,數(shù)字化是視頻監(jiān)控系統(tǒng)的發(fā)展方向。傳統(tǒng)的視頻處理系統(tǒng)為了滿足實(shí)時(shí)性和靈活的實(shí)際接口需要,多采用FPGA+ DSP或者

2019-08-02 06:18:40

嵌入式視頻處理系統(tǒng)領(lǐng)域的FPGA驗(yàn)證,不看肯定后悔

2021-05-07 06:18:27

隨著紅外探測(cè)技術(shù)迅猛的發(fā)展,當(dāng)今紅外實(shí)時(shí)圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來越大,速度要求也越來越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時(shí),有時(shí)就顯得有些捉襟見肘了

2019-08-23 08:29:27

今天給大俠帶來基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)設(shè)計(jì),由于篇幅較長(zhǎng),分三篇。今天帶來第二篇,中篇,話不多說,上貨。導(dǎo)讀隨著科學(xué)技術(shù)的高速發(fā)展,FPGA在系統(tǒng)結(jié)構(gòu)上為數(shù)字圖像處理帶來了新的契機(jī)。圖像中

2021-07-28 06:06:26

的發(fā)展帶來機(jī)遇的同時(shí)也帶來了挑戰(zhàn)。視頻圖像處理你了解多少?關(guān)注中國電子學(xué)會(huì)2013年度盛會(huì)---圖形圖像處理技術(shù)大會(huì)。 好用的圖像處理軟件 視頻監(jiān)控系統(tǒng)技術(shù) 圖像處理系統(tǒng) 圖像視頻傳感器 最新微處理技術(shù)

2013-09-24 15:22:25

怎么設(shè)計(jì)一個(gè)基于FPGA的實(shí)時(shí)視頻圖像處理系統(tǒng)?

2021-05-06 08:21:45

怎樣去設(shè)計(jì)音/視頻實(shí)時(shí)處理系統(tǒng)的硬件部分?怎樣去設(shè)計(jì)音/視頻實(shí)時(shí)處理系統(tǒng)的軟件部分?

2021-06-02 07:22:23

介紹了一種用單片FPGA實(shí)現(xiàn)的實(shí)時(shí)、多任務(wù)、高速圖像處理系統(tǒng)。該系統(tǒng)承擔(dān)著提高信噪比、壓縮數(shù)據(jù)量、Stokes參數(shù)觀測(cè)和儀器及觀測(cè)模式控制等任務(wù)。針對(duì)一個(gè)星載系統(tǒng),采用了

2008-11-20 11:57:08 15

15 基于FPGA的小型微光視頻圖像增強(qiáng)處理系統(tǒng)Mini Low-level-light Video Image Enhancement Processing System Based on FPGA

摘要:為微光視頻圖像的實(shí)時(shí)增強(qiáng)設(shè)計(jì)了一套可應(yīng)用于空間狹小環(huán)境中

2009-01-11 12:11:18 34

34 設(shè)計(jì)了一種基于FPGA 和DSP 的光纖信號(hào)實(shí)時(shí)處理系統(tǒng),介紹了系統(tǒng)的硬件組成和工作原理。該系統(tǒng)采用FPGA 實(shí)現(xiàn)數(shù)據(jù)的高速采集和邏輯控制,用DSP 實(shí)現(xiàn)傳感信號(hào)的全數(shù)字解調(diào),分析了載

2009-06-19 11:17:43 24

24 以DSP TMS320C6416 為核心處理器, 設(shè)計(jì)了一種通用的MPEG-4實(shí)時(shí)圖象處理系統(tǒng)。文中對(duì)系統(tǒng)的硬件系統(tǒng)及軟件設(shè)計(jì)進(jìn)行了詳細(xì)的介紹。其中視頻采集、運(yùn)動(dòng)估計(jì)算法和軟件的優(yōu)化是保證本

2009-08-21 11:07:29 15

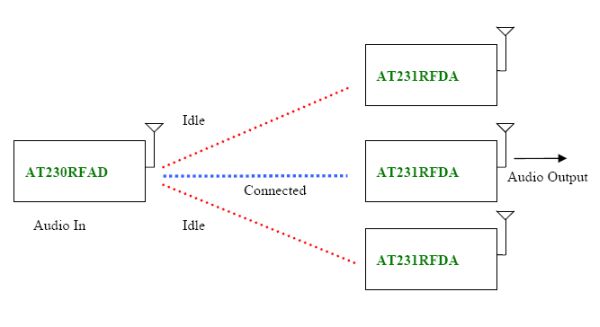

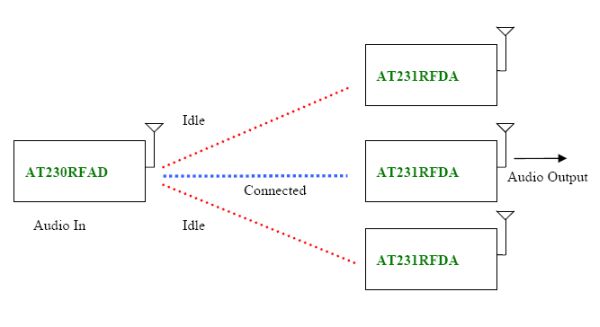

15 采用T I 公司的TM S 3 2 0 D M 6 4 2 型數(shù)字媒體數(shù)字信號(hào)處理器( D S P )設(shè)計(jì)多路音/視頻采集處理系統(tǒng), 實(shí)現(xiàn)實(shí)時(shí)處理4 路模擬視頻和音頻輸入、1 路模擬/數(shù)字視頻和l 路模擬音頻信

2009-11-27 11:17:28 22

22 針對(duì)目前視頻處理系統(tǒng)中應(yīng)用比較廣泛的YCbCr 4:2:0格式的數(shù)據(jù),提出了一種在硬件上實(shí)現(xiàn)顏色空間轉(zhuǎn)換的設(shè)計(jì),解決了色度信號(hào)的插值操作和插值后數(shù)據(jù)流的重組問題,并在FPGA上采用Veril

2010-07-28 17:23:56 38

38 本文設(shè)計(jì)方案仿生眼嵌入式機(jī)載視頻圖像處理系統(tǒng)使用ti公司tms320dm642高性能數(shù)字多媒體處理器作為核心處理器,系統(tǒng)解決方案了實(shí)時(shí)收集圖像,實(shí)時(shí)處理圖像,實(shí)時(shí)輸出目標(biāo)資料,

2010-09-10 10:17:46 33

33 嵌入式視頻處理系統(tǒng)領(lǐng)域的FPGA驗(yàn)證

隨著生活水準(zhǔn)的不斷提升,越來越多的家庭開始在客廳配備5.1聲道或7.1聲道的家庭影院系統(tǒng)。

不過,對(duì)于

2009-11-03 09:53:32 646

646

基于雙DSP的實(shí)時(shí)圖像處理系統(tǒng)

介紹了基于雙DSP的實(shí)時(shí)圖像處理系統(tǒng)。該系統(tǒng)通過兩片TMS320C6201作為系統(tǒng)計(jì)算中心,通過可重構(gòu)成的FPGA計(jì)算系統(tǒng)獲得系

2009-12-08 14:25:35 1009

1009

基于DSP+FPGA+ASIC的實(shí)時(shí)圖像處理系統(tǒng)

1.引言

隨著紅外焦平面陣列技術(shù)的快速發(fā)展,紅外成像系統(tǒng)實(shí)現(xiàn)了高幀頻、高分辨率、高可靠性及微型化,在目標(biāo)跟蹤

2010-01-13 10:39:49 1115

1115

摘要:數(shù)字視頻信號(hào)處理涉及對(duì)高速實(shí)時(shí)視頻信號(hào)的傳輸和處理,要求相關(guān)電路系統(tǒng)具有強(qiáng)大的數(shù)據(jù)處理能力。介紹一種以DSP和FPGA器件為核心構(gòu)建的場(chǎng)發(fā)射平板顯示器視頻信號(hào)處理系統(tǒng)方案,并以,11公司的DSP芯片TMS320C6713和Xilinx公司的FPGA芯片XC3S200一PQ208

2011-02-25 16:39:19 53

53 介紹了一種用于數(shù)字化雙功能多普勒超聲成像儀中以單片FPGA 實(shí)現(xiàn)的實(shí)時(shí)、多任務(wù)、高速信號(hào)處理系統(tǒng),該系統(tǒng)承擔(dān)著動(dòng)態(tài)濾波、多普勒解調(diào)、包絡(luò)檢波、FFT 變換、數(shù)據(jù)壓縮、數(shù)據(jù)選通等

2011-09-14 15:18:43 143

143 在以DSP為核心的視頻處理系統(tǒng)中,視頻采集的方法通常可以分為兩大類:自動(dòng)的視頻采集和基于DSP的視頻采集。前者通常采用CPLD/FPGA控制視頻解碼芯片,通過FIFO或者雙口RAM向DSP傳送數(shù)據(jù)

2011-09-14 17:05:31 2302

2302

文中介紹了系統(tǒng)的硬件整體架構(gòu),論證了視頻編解碼模塊和視頻緩存模塊的硬件設(shè)計(jì)方案。實(shí)際測(cè)試結(jié)果表明,系統(tǒng)能夠流暢地對(duì)1 6001 200分辨率,60幀/s刷新率,24位真彩色的高清視頻進(jìn)行處

2011-11-30 17:14:57 55

55 基于FPGA的雷達(dá)信號(hào)處理系統(tǒng)設(shè)計(jì)的論文

2015-10-30 10:38:12 6

6 基于FPGA的視頻后處理系統(tǒng)--的技術(shù)論文

2015-10-30 10:38:26 0

0 一種基于FPGA和PCI總線的天文圖像實(shí)時(shí)采集與處理系統(tǒng)的設(shè)計(jì),感興趣的小伙伴們可以看一看。

2016-09-14 17:17:07 8

8 基于達(dá)芬奇平臺(tái)的微光視頻實(shí)時(shí)處理系統(tǒng)關(guān)鍵技術(shù)的研究與實(shí)現(xiàn)

2016-09-22 14:08:55 11

11 基于FPGA+DSP實(shí)時(shí)圖像采集處理系統(tǒng)設(shè)計(jì)

2017-01-03 11:41:35 9

9 高效機(jī)載SAR實(shí)時(shí)成像處理系統(tǒng)設(shè)計(jì)_楊磊

2017-01-07 16:00:43 1

1 基于FPGA的視頻圖像處理系統(tǒng)設(shè)計(jì)_李蓮

2017-03-19 11:38:26 21

21 基于雙DSP和雙FPGA的高速圖像處理系統(tǒng)設(shè)計(jì)_吳雷

2017-03-16 09:28:51 2

2 基于FPGA的軟硬件協(xié)同實(shí)時(shí)紙病圖像處理系統(tǒng)_齊璐

2017-03-19 19:07:17 0

0 本文介紹了基于FPGA的機(jī)載視頻圖形顯示系統(tǒng)架構(gòu)的設(shè)計(jì)與優(yōu)化,并介紹了三種系統(tǒng)架構(gòu),對(duì)系統(tǒng)各組成部分進(jìn)行了詳細(xì)的分析與概述。

2017-10-15 10:19:56 2

2 基于FPGA和DSP的高速圖像處理系統(tǒng)

2017-10-19 13:43:31 19

19 基于DSP和FPGA的模塊化實(shí)時(shí)圖像處理系統(tǒng)設(shè)計(jì)

2017-10-23 14:09:42 9

9 本文提出了一種實(shí)時(shí)圖像采集和處理系統(tǒng)的設(shè)計(jì)方法,該系統(tǒng)以TMS320DM642[1-2]為核心,結(jié)合視頻解碼芯片SAA7115H和OSD FPGA構(gòu)成實(shí)時(shí)圖像采集和處理系統(tǒng)電路。 1 系統(tǒng)總體設(shè)計(jì)

2017-10-31 16:56:33 7

7 本文設(shè)計(jì)一種基于FPGA的機(jī)載顯示系統(tǒng)架構(gòu),能夠?qū)崿F(xiàn)2D圖形繪制,構(gòu)成各種飛行參數(shù)畫面,同時(shí)疊加外景視頻圖像。BRAM資源占用方面,視頻旋轉(zhuǎn)算法需要279個(gè)36Kb的BRAM;DDR3吞吐量方面

2017-11-18 03:03:04 1659

1659 本文對(duì)基于FPGA的機(jī)載視頻圖形顯示系統(tǒng)架構(gòu)進(jìn)行設(shè)計(jì)和優(yōu)化。從實(shí)時(shí)性、BRAM資源占用和DDR3吞吐量三方面進(jìn)行分析,改進(jìn)幀速率提升算法來提高實(shí)時(shí)性;改進(jìn)視頻旋轉(zhuǎn)算法來降低BRAM資源占用;改變

2017-11-18 03:42:01 1882

1882 為解決高速數(shù)字圖像處理系統(tǒng)和實(shí)時(shí)性相沖突的要求,設(shè)計(jì)了以多DSP(數(shù)字信號(hào)處理器TMS320C6416)和現(xiàn)場(chǎng)可編程門陣列(FPGA)相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng)。重點(diǎn)介紹了該系統(tǒng)的硬件資源選擇、基本組

2017-11-18 12:34:02 4034

4034

通過研究視頻圖像處理和視頻圖像幀格式以及FIF0緩存技術(shù),提出了基于FPGA的視頻圖像處理系統(tǒng)設(shè)計(jì)。該設(shè)計(jì)運(yùn)用幀間差分法、同步FIF0緩存設(shè)計(jì),有效避免了圖像處理系統(tǒng)設(shè)計(jì)中亞穩(wěn)態(tài)和異步信號(hào)處理等時(shí)序

2017-11-22 09:13:03 4629

4629 微型H.264核結(jié)合賽靈思Zynq SoC在小型快速的視頻流處理系統(tǒng)的應(yīng)用。ASSP架構(gòu)不靈活,而基于FPGA和微處理器組合的系統(tǒng)雖然尺寸大但較為靈活,一直以來設(shè)計(jì)人員為創(chuàng)建PCB占位面積

2017-11-22 15:54:46 4929

4929 高速寬帶、高精度的挑戰(zhàn),而且對(duì)采樣時(shí)機(jī)、采樣點(diǎn)數(shù)、采樣速率的可控性也提出了較高的要求,本文提出了一種實(shí)時(shí)圖像采集和處理系統(tǒng)的設(shè)計(jì)方法,該系統(tǒng)以TMS320DM642[1-2]為核心,結(jié)合視頻解碼芯片SAA7115H和OSD FPGA構(gòu)成實(shí)時(shí)圖像采集和處理系統(tǒng)電路。

2018-07-16 09:42:00 2633

2633

隨著航空電子技術(shù)的不斷發(fā)展,現(xiàn)代機(jī)載視頻圖形顯示系統(tǒng)對(duì)于實(shí)時(shí)性等性能的要求日益提高。常見的系統(tǒng)架構(gòu)主要分為三種: (1)基于 GSP+VRAM+ASIC 的架構(gòu),優(yōu)點(diǎn)是圖形 ASIC 能夠有效提高

2017-11-30 15:10:09 21

21 本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn),DSP-BF561作為主處理器,負(fù)責(zé)整個(gè)算法的調(diào)度和數(shù)據(jù)流的控制,完成圖像數(shù)據(jù)的采集與顯示及核心算法的實(shí)現(xiàn),FPGA作為DSP的協(xié)處理器,依托其高度的并行處理能力,完成圖像預(yù)處理中大量的累乘加運(yùn)算。實(shí)驗(yàn)證明系統(tǒng)達(dá)到了實(shí)時(shí)性要求。

2017-12-25 10:39:47 4504

4504

設(shè)計(jì)了一種基于FPGA的視頻實(shí)時(shí)采集系統(tǒng), 視頻數(shù)據(jù)通過視頻解碼器、雙口RAM、內(nèi)存控制器, 然后存入片外SDRAM中。根據(jù)視頻處理算法的要求和SDRAM的特點(diǎn), 對(duì)視頻數(shù)據(jù)的存儲(chǔ)格式及讀寫時(shí)序進(jìn)行了優(yōu)化, 提高了系統(tǒng)的數(shù)據(jù)傳輸速率, 能夠滿足后續(xù)視頻處理系統(tǒng)的需要。

2018-10-18 17:25:35 7

7 實(shí)時(shí)視頻信號(hào)處理的實(shí)時(shí)性和跟蹤算法的復(fù)雜性是一對(duì)矛盾,為此采用DSP+FPGA 的架構(gòu)設(shè)計(jì),同時(shí)滿足實(shí)時(shí)性和復(fù)雜性的要求,提高了系統(tǒng)的整體性能。DSP 作為主處理器,利用其高速的運(yùn)算能力,快速有效地處理

2018-12-18 19:27:46 15

15 構(gòu)建數(shù)字視頻圖像處理系統(tǒng)的優(yōu)勢(shì):,4、設(shè)計(jì)實(shí)例:基于FPGA的MPEG4AVC/H.264視頻編碼器核心算法;,5、設(shè)計(jì)基于FPGA高速數(shù)字信號(hào)處理系統(tǒng)的技巧

2019-03-29 16:53:50 15

15 提出了一種基于FPGA和PCI總線的天文圖像實(shí)時(shí)采集與處理系統(tǒng)設(shè)計(jì);其包括硬件結(jié)構(gòu)、FPGA數(shù)據(jù)獲取和傳輸邏輯。該系統(tǒng)能夠在FPGA中實(shí)現(xiàn)對(duì)最高峰值是660 MB/s,均值為200 MB/s,幀速率

2021-02-04 16:46:00 16

16 基于FPGA和DSP的機(jī)載圖形顯示系統(tǒng)

2021-06-08 10:48:08 36

36 基于HDMI的全高清實(shí)時(shí)視頻采集與圖像處理系統(tǒng)

2021-06-23 12:00:46 24

24 FPGA在視頻處理方面可能很有用處,但在驗(yàn)證基于FPGA的視頻系統(tǒng)時(shí),則需要仔細(xì)關(guān)注您所用的方法。

2023-10-27 17:34:39 158

158

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論