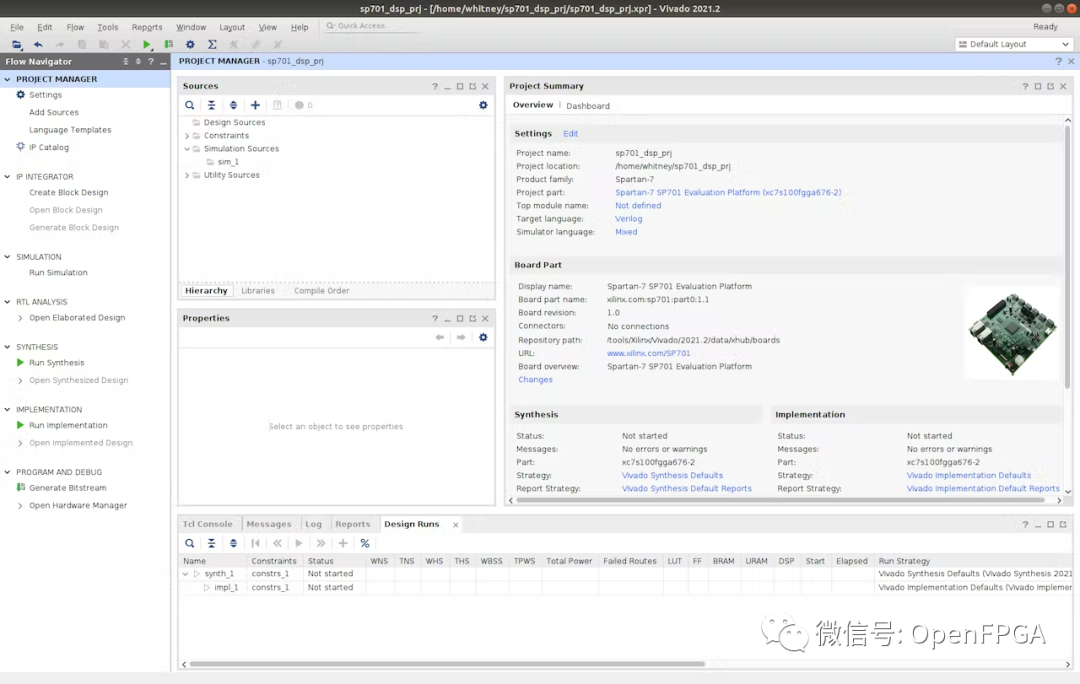

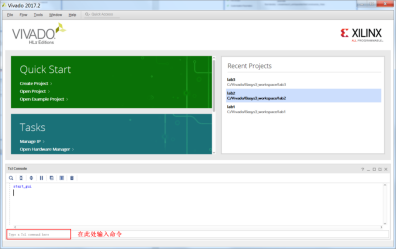

大家好,歡迎Vivado的一個快速演示,它是xilinx新的設計套件,應用到7系列和以上的系列器件。

2012-04-25 08:55:55 2192

2192 基于FPGA vivado 17.2 的數字鐘設計

2018-06-08 09:41:47 10186

10186

51單片機學習74系列單片機封裝

2013-04-14 14:18:51

74系列芯片總匯,

2017-03-11 11:22:56

74系列芯片的型號有哪些區別?74系列芯片的功能有哪些?

2021-08-20 06:08:21

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

FPGA+DA怎么實現調相呢,不是數字調制。就是用一個正弦波的峰值來控制載波的相位,這個要怎么在FPGA中實現呢?希望大神能給個思路,我開始是想調制波直接用DDS IP核生成,然后用起幅值作為地址去查找表,表中存的是載波幅值,然后輸出,但是結果一直不對。

2017-06-29 16:00:24

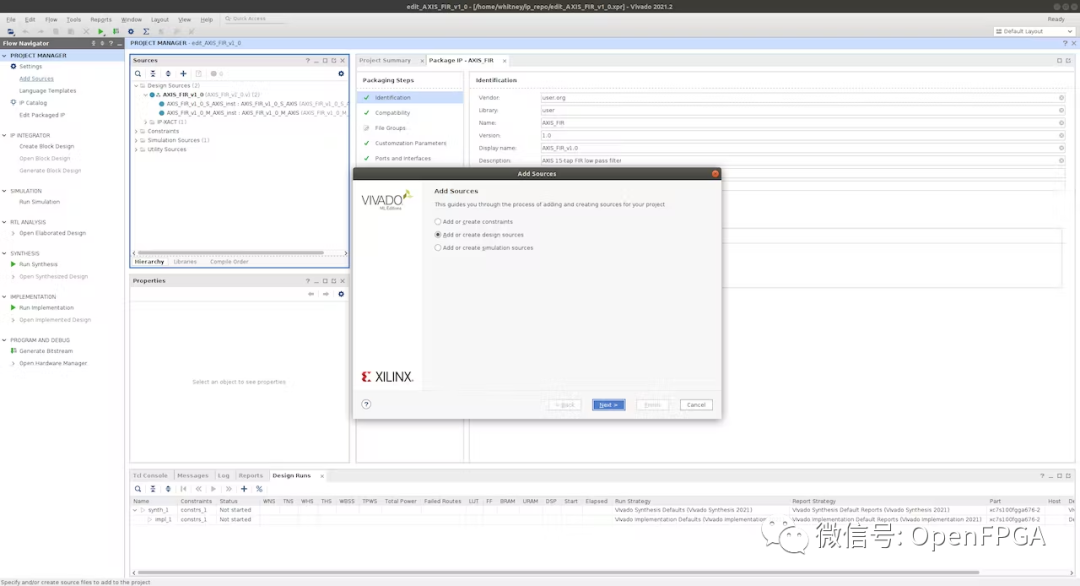

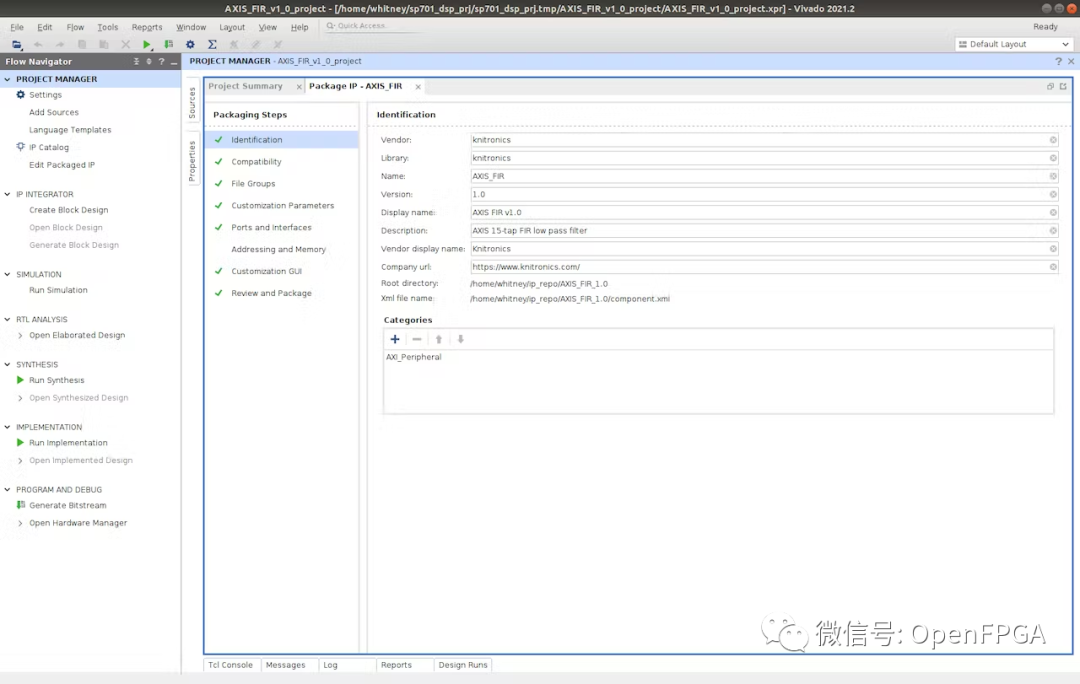

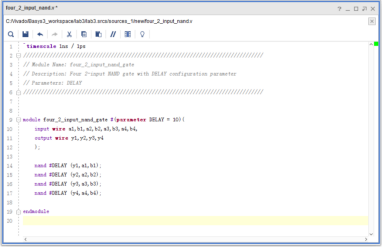

/ 1555.4 IP的屬性與狀態 / 1565.5 IP的約束 / 1595.6 封裝IP / 1645.6.1 通過Vivado工程封裝用戶代碼 / 1645.6.2 通過指定目錄封裝用戶代碼

2020-10-21 18:24:48

嗨,我正在使用Vivado 13.2在Zynq 7000上實現嵌入式設計。這是我的設計流程1)創建了一個新項目my_ip,其中包含1個ngc文件和2個從Xilinx Fifo Generator生成

2020-04-15 10:22:15

關于Zynq的Vivado 2013.1發行說明說:“需要及早訪問Vivado IP集成商”。這是什么意思?它是否真的支持Zynq開箱即用?提前致謝。以上來自于谷歌翻譯以下為原文Vivado

2018-12-04 11:00:58

在模擬模型方面,Vivado提供的IP似乎有一些根本性的變化。在將工作設計從ISE 14.4轉換為Vivado 2013.2之后,然后按照建議的方式升級大部分Xilinx IP,例如基本乘法器,除法

2019-02-26 10:42:23

與字母的組合,首字母不能是數字)后點擊next:5)選擇對應的工程類型6)選擇對應的FPGA,可以通過篩選FGPA系列,封裝,速度等級,溫度等級,即可快速篩選出實際用到的芯片(我們的套件選用

2019-07-18 15:40:33

與字母的組合,首字母不能是數字)后點擊next:5)選擇對應的工程類型6)選擇對應的FPGA,可以通過篩選FGPA系列,封裝,速度等級,溫度等級,即可快速篩選出實際用到的芯片(我們的套件選用

2023-09-06 17:55:44

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

剛剛接觸FPGA,通過視頻學習發現使用VIVADO編寫FPGA程序可以通過調用IP核連線和編寫.v文件,實際做過程什么時候該調用IP,怎么知道有該功能的IP,先調用IP連線還是先寫.V文件呢?

2022-08-29 08:44:03

請教一下,vivado怎么把帶ip核的工程進行封裝,保證代碼不可見,可以通過端口調用。我嘗試了以下方法,ippackage,如果要在另一個程序里調用,也要提供源代碼;另一個方法是將網表文件edf文件與端口聲明結合,這種方法只能實現不帶ip核的封裝

2017-07-14 09:18:30

本實驗通過調用PLL IP core來學習PLL的使用、vivado的IP core使用方法。

2021-03-02 07:22:13

嗨, 我正在嘗試在Vivado 2018.1中實現Kintex-7設計,它似乎工作了一段時間,但突然間我在嘗試運行實現時遇到了一個奇怪的錯誤。日志顯示以下錯誤。如果我嘗試轉到路徑,則

2018-11-13 14:18:54

`Xilinx系列FPGA芯片IP核詳解(完整高清書簽版)`

2017-06-06 13:15:16

為什么vivado2016調用MIG ip核會收到嚴重警告呢?這個critical warning會有影響嗎,要怎么解決呢?

2021-10-18 09:41:21

我對Vivado內部的IP檢查點有疑問。當我在Vivado中啟用IP內核的檢查點時,我可以在Design Runs窗口中看到此IP的“synth”和“impl”。對于IP的“合成”,我可以理解這是

2019-03-08 13:30:52

請問有哪位大神,可以幫忙破解一個vivado的IP核。不勝感激,聯系QQ397679468

2017-11-24 09:30:30

嗨,在Vivado 2015.4和ISE 14.7中實現的相同設計之間的資源利用率是否會有任何差異?考慮到這樣的事實,IP在Artix-7 FPGA中重新生成FIFO(版本9.3到13.1)時鐘向導

2019-04-24 09:12:08

今天給大俠帶來基于 FPGA Vivado 信號發生器設計,開發板實現使用的是Digilent basys 3。話不多說,上貨。

需要源工程可以在以下資料獲取里獲取。

資料匯總|FPGA軟件安裝包

2023-08-15 19:57:56

,能實現計時的功能。由于數碼管只有4位,因此本數字鐘只能計分和秒。本系統的邏輯部分主要由74系列的IP構成。

獲取本篇相關源工程代碼,可在公眾號內回復“數字鐘設計源工程”,本篇涉及到兩個操作軟件

2023-08-18 21:18:47

今天給大俠帶來基于 FPGA Vivado 示波器設計,開發板實現使用的是Digilent basys 3,話不多說,上貨。

需要源工程可以在以下資料獲取里獲取。

資料匯總|FPGA軟件安裝包

2023-08-17 19:31:54

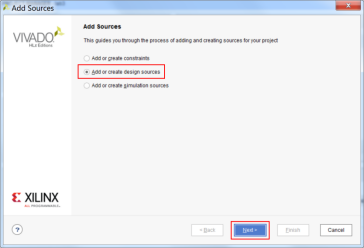

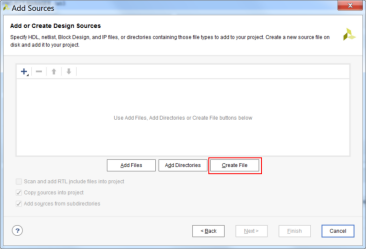

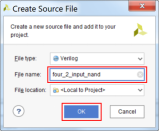

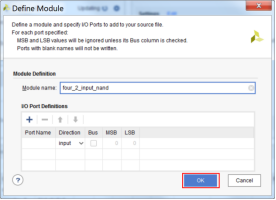

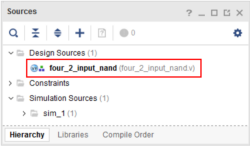

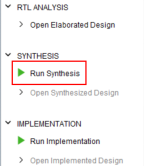

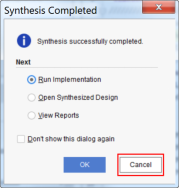

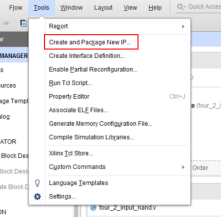

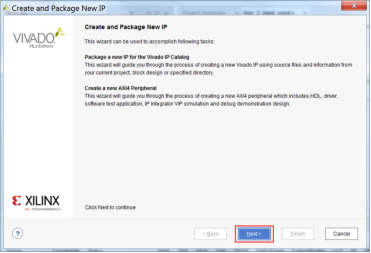

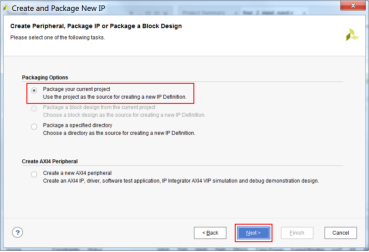

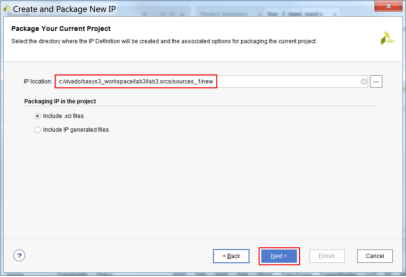

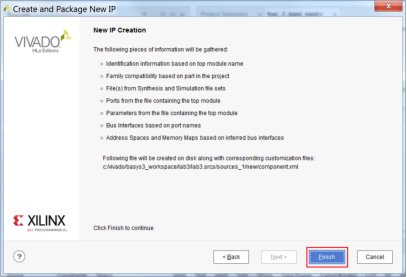

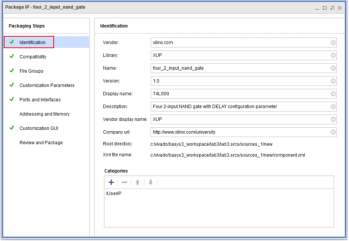

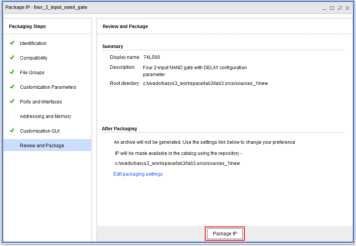

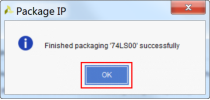

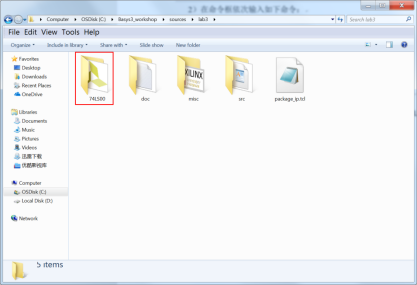

基于 FPGA vivado 2017.2 的74系列IP封裝實驗指導一、實驗目的掌握封裝IP的兩種方式:GUI方式以及Tcl方式二、實驗內容 本實驗指導以74LS00 IP封裝為例,介紹了兩種封裝

2017-12-20 10:23:11

基于FPGA vivado 17.2 的數字鐘設計目的:熟悉vivado 的開發流程以及設計方法附件:

2017-12-13 10:16:06

基于FPGA的IP核8051上實現TCPIP的設計

2012-08-06 12:18:28

飛舞,這里就不贅述了,以免有湊字數的嫌疑。下面我們就Matlab和FPGA兩個工具雙管齊下,比對Vivado的FFT IP核生成的數據。2 Matlab產生測試數據,繪制cos時域和頻域波形

2019-08-10 14:30:03

你好我是Xilinx FPGA板的初學者。我有一個帶有Artix-7的Nexys 4,我想實現MICROBLAZE Softcore并添加它的伺服電機IP并且我被阻止了。我必須使用這種配置的ISE設計套件或Vivado設計套件嗎?有人可以幫我。謝謝

2020-07-19 18:17:05

如何使用FPGA和IP Core實現定制緩沖管理?

2021-04-29 06:01:33

的是如何使用它或將其轉移到普通的Vivado項目,這樣我就可以應用測試平臺并對其進行測試。從我的角度來看,IP塊設計是加載IP和進行互連的好方法。但是,使用它還需要其他步驟。我錯了嗎?我花了幾個星期的時間嘗試將

2020-03-20 08:52:30

的端口號呢?我最后想實現的目標是:WIFI模塊分別分配給FPGA和手機IP地址,然后手機通過無線局域***縱FPGA.

2014-10-29 16:03:59

(IntellectualProperty)核。IP核由相應領域的專業人員設計,并經反復驗證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設計者只需做很少設計就可實現所需系統。基于IP核的模塊化設計可縮短設計周期,提高設計質量。現場

2019-09-03 07:44:22

是對的,請糾正我,但我認為這一步只需按一個按鈕)3 - 將IP內核導入Vivado并: a-生成塊設計(這是我最不舒服的步驟,我會很高興獲得一些好的建議,因為算法很復雜且IP核不是基本的) b-合成,實現

2020-03-24 08:37:03

紫光的FPGA哪些系列支持高速接口?相關接口有哪些免費的IP可以使用呢?性能怎么樣?

2024-03-20 16:58:29

萊迪思半導體公司日前發布了即可獲取的五款新的全面的知識產權(IP)套件,用于加速在各行業使用屢獲殊榮的LatticeECP3™ FPGA系列的電子系統設計。這五款IP套件分別是PCI Express

2011-02-19 08:57:25 767

767 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 利用FPGA的IP核設計和實現FFT算法

2016-05-24 14:14:47 36

36 testbench來驗證設計。 Integrate帶有Xilinx IP Block的 HLS IP 這里展示了在IP Integrator中,如何將兩個HLS IP blocks跟Xilinx IP FFT結合在一起 ,并且在Vivado中驗證設計。

2017-02-07 17:59:29 4179

4179

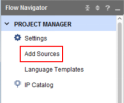

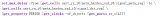

本文基于xilinx 的IP核設計,源于音頻下采樣這一需求。 創建vivado工程 1. 首先打開vivado,創建一個新的project(勾選create project subdirectory

2017-02-08 02:25:09 3716

3716

隨著xilinx公司進入20nm工藝,以堆疊的方式在可編程領域一路高歌猛進,與其配套的EDA工具——新一代高端FPGA設計軟件VIVADO也備受關注和飽受爭議。

2017-02-11 19:08:00 4986

4986 有關FPGA——VIVADO15.4開發中IP 的建立

2017-02-28 21:04:35 15

15 Xilinx的Vivado采用原理圖的設計方式,比較直觀適合大型項目,我們自己的code都需要封裝成user IP。這里主要介紹怎么把多個關聯管腳合并成類似bus的大端口。

2017-09-15 16:54:34 42

42 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-15 11:19:14 8390

8390 使用Xilinx Vivado HLS(Vivado 高層次綜合)工具實現浮點復數QRD矩陣分解并提升開發效率。使用VivadoHLS可以快速、高效地基于FPGA實現各種矩陣分解算法,降低開發者

2017-11-17 17:47:43 3293

3293

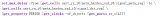

其實Tcl在Vivado中還有很多延展應用,接下來我們就來討論如何利用Tcl語言的靈活性和可擴展性,在Vivado中實現定制化的FPGA設計流程。 基本的FPGA設計實現流程 FPGA的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟IC設計流程類似,可以分為前端設計和后端設計。

2017-11-18 01:48:01 3295

3295

資源、速度和功耗是FPGA設計中的三大關鍵因素。隨著工藝水平的發展和系統性能的提升,低功耗成為一些產品的目標之一。功耗也隨之受到越來越多的系統工程師和FPGA工程師的關注。Xilinx新一代開發工具Vivado針對功耗方面有一套完備的方法和策略,本文將介紹如何利用Vivado進行功耗分析和優化。

2017-11-18 03:11:50 4873

4873 在Vivado下,有兩種方式管理IP。一種是創建FPGA工程之后,在當前工程中選中IP Catalog,生成所需IP,這時相應的IP會被自動添加到當前工程中;另一種是利用Manage IP,創建獨立

2017-11-18 04:22:58 5473

5473 關于Tcl在Vivado中的應用文章從Tcl的基本語法和在Vivado中的應用展開,介紹了如何擴展甚至是定制FPGA設計實現流程后,引出了一個更細節的應用場景:如何利用Tcl在已完成布局布線

2017-11-18 18:26:46 4987

4987

在給別人用自己的工程時可以封裝IP,Vivado用封裝IP的工具,可以得到像xilinx的ip一樣的可以配置參數的IP核,但是用其他工程調用后發現還是能看到源文件,如何將工程源文件加密,暫時沒有找到方法,如果知道還請賜教。

2018-06-26 11:33:00 7425

7425 大家好,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 36233

36233 子系統以及完整的 Vivado 實現工具套件,使主流用戶能夠方便地采用生產力最高、最先進的C 語言和 IP設計流程。結合最新 UltraFast 高級生產力設計方法指南,相比采用傳統方法而言,用戶可將生產力提升 10-15 倍。全新HLx 版本將作為 Vivado 設計套件的免費升級版提供。

2018-08-17 11:43:00 2677

2677 不同市場領域的連接需求。全新的 Spartan-7 FPGA 將得到免費 Vivado 設計套件 WebPACK 版本以及 Vivado 設計版本和系統版本的支持,能夠快速集成和實現。

2018-08-20 10:48:00 1464

1464 Vivado不僅是xlinx公司的FPGA設計工具,用它還可以學習Verilog描述,你造嗎?

2018-09-20 09:29:22 9427

9427 FPGA器件中創建高度集成的、復雜的設計,賽靈思推出了Vivado IP Integrator(IPI)早期試用版本。Vivado IPI可加速RTL、

2018-09-25 09:18:01 275

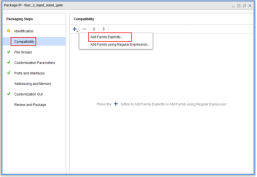

275 第二項是器件添加,只有選擇了相應的器件,你的IP核才能在那個器件里被使用。單擊器件,右鍵——Add——Add Family Explicitiy,于是便可以選擇要適用的器件系列了。

2018-11-12 14:31:16 10034

10034 觀看視頻,學習如何將 Vivado IP 和第三方綜合工具配合使用。 此視頻將通過一個設計實例引導您完成創建自定義 IP 的步驟;用第三方綜合工具IP黑盒子來審查所需 IP 輸出;整合 Vivado IP 網表和第三方綜合工具網表的兩個方法,即 “網表項目模式” 和 “非項目 Tcl 腳本模式”。

2018-11-21 06:34:00 4811

4811 此視頻概述了Vivado Design Suite中的IP加密。

它涵蓋了IP加密工具流程,如何準備加密IP以及如何在Vivado中運行加密工具。

2018-11-20 06:34:00 5948

5948 了解Vivado中的Logic Debug功能,如何將邏輯調試IP添加到設計中,以及如何使用Vivado Logic Analyzer與邏輯調試IP進行交互。

2018-11-30 06:22:00 3107

3107 了解如何使用Vivado的創建和封裝IP功能創建可添加自定義邏輯的AXI外設,以創建自定義IP。

2018-11-29 06:48:00 6801

6801

該視頻演示了如何使用Vivado IP Integrator組裝具有多個時鐘域的設計。

它顯示了Vivado中的設計規則檢查和功能如何幫助用戶自動執行此流程。

2018-11-27 07:40:00 3539

3539 在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,下面就介紹一下在vivado2017.3中進行PL開發時調用IP的方法。

2018-12-22 14:26:38 4468

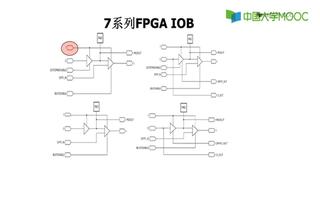

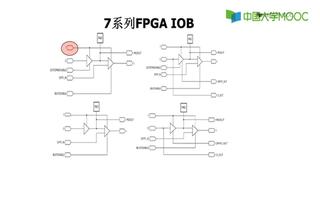

4468 本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-05 07:06:00 2166

2166

VIVADO是一個基于AMBA AXI4 互聯規范、IP-XACT IP封裝元數據、工具命令語言(TCL)、Synopsys 系統約束(SDC) 以及其它有助于根據客戶需求量身定制設計流程并符合業界

2019-12-03 07:09:00 1896

1896 本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-02 07:09:00 3602

3602

Tcl介紹 Vivado是Xilinx最新的FPGA設計工具,支持7系列以后的FPGA及Zynq 7000的開發。與之前的ISE設計套件相比,Vivado可以說是全新設計的。無論從界面、設置、算法

2020-11-17 17:32:26 2112

2112 ? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP

2020-12-29 15:59:39 9496

9496 本文接續上一篇《FPGA雜記基礎篇》,繼續為大家分享IP例化和幾個基于FPGA芯片實現的Demo工程。IP例化IP即是一個封裝好的模塊,集成在相應的開發環境里面,以安路的TD軟件為例,不同系列的芯片集成了不同的IP模塊,可以通過軟件例化調用

2020-12-24 12:58:51 1048

1048 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有

2021-03-22 10:31:16 3409

3409 本次使用Vivado調用DDS的IP進行仿真,并嘗試多種配置方式的區別,設計單通道信號發生器(固定頻率)、Verilog查表法實現DDS、AM調制解調、DSB調制解調、可編程控制的信號發生器(調頻調相)。

2021-04-27 16:33:06 5595

5595

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。

2021-04-27 15:45:12 22634

22634

基于FPGA的TCP/IP協議的實現說明。

2021-04-28 11:19:47 49

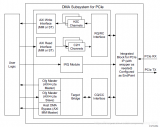

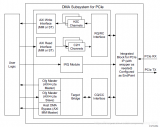

49 基于VIVADO的PCIE IP的使用 項目簡述 上一篇內容我們已經對PCIE協議進行了粗略的講解。那么不明白具體的PCIE協議,我們就不能在FPGA中使用PCIE來進行高速數據傳輸了嗎?答案是否

2021-08-09 16:22:10 10199

10199

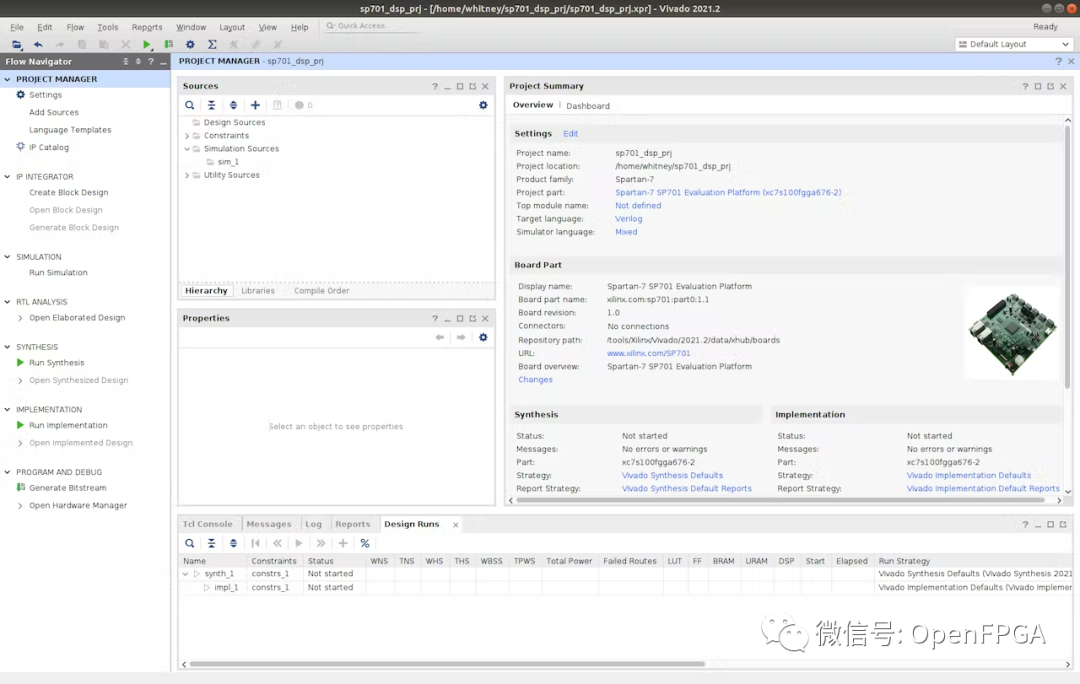

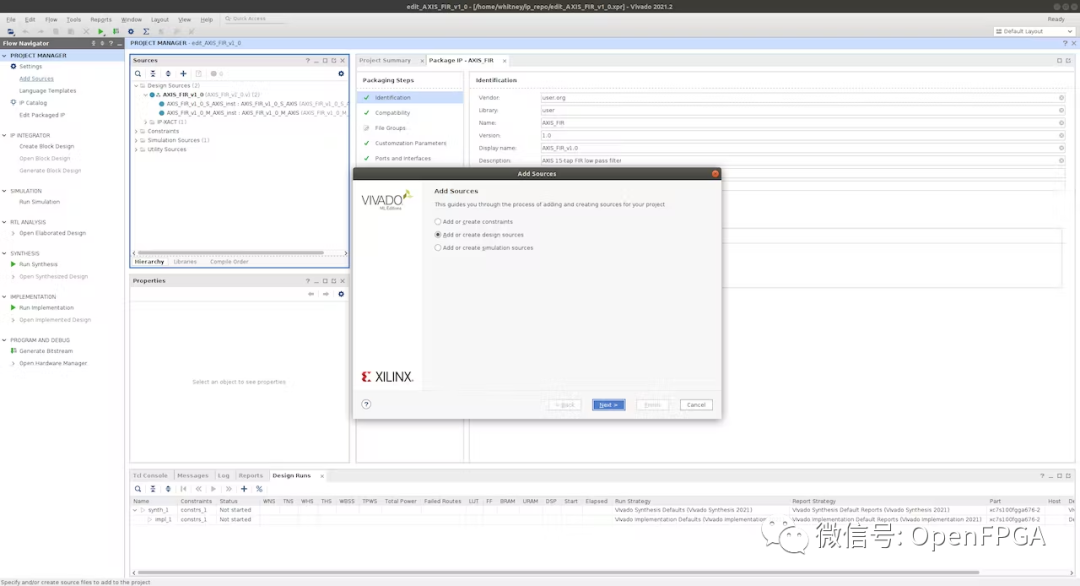

Vivado提供了三種封裝IP的方式:(1)將當前工程封裝為IP;(2)將當前工程中的BD(IPI 設計)封裝為IP;(3)將指定的文件目錄封裝為IP。 IP Packager支持的輸入文件HDL

2021-08-10 18:09:29 5567

5567

【流水燈樣例】基于 FPGA Vivado 的數字鐘設計前言模擬前言Vivado 設計流程指導手冊——2013.4密碼:5txi模擬

2021-12-04 13:21:08 26

26 在FPGA實際的開發中,官方提供的IP并不是適用于所有的情況,需要根據實際修改,或者是在自己設計的IP時,需要再次調用時,我們可以將之前的設計封裝成自定義IP,然后在之后的設計中繼續使用此IP。因此本次詳細介紹使用VIvado來封裝自己的IP,并使用IP創建工程。

2022-04-21 08:58:05 4579

4579 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有些許改進,所以寫這篇文章補充下。

2022-08-29 14:41:55 1549

1549 今天介紹的是vivado的三種常用IP核:時鐘倍頻(Clocking Wizard),實時仿真(ILA),ROM調用(Block Memory)。

2023-02-02 10:14:01 2529

2529 AMD-Xilinx 的 Vivado 開發工具具有很多方便FPGA開發功能,我最喜歡的功能之一是block design的設計流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:50:57 747

747

AMD-Xilinx 的 Vivado 開發工具具有很多方便FPGA開發功能,我最喜歡的功能之一是block design的設計流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:51:14 1581

1581

AMD-Xilinx 的 Vivado 開發工具具有很多方便FPGA開發功能,我最喜歡的功能之一是block design的設計流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:51:19 735

735

今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

2023-05-05 09:44:46 674

674

關于 Tcl 在 Vivado中的應用文章從 Tcl 的基本語法和在 Vivado 中的 應用展開,繼上篇《用 Tcl 定制 Vivado 設計實現流程》介紹了如何擴展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 1240

1240

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-20 14:23:57 622

622

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1628

1628

FPGA開發中使用頻率非常高的兩個IP就是FIFO和BRAM,上一篇文章中已經詳細介紹了Vivado FIFO IP,今天我們來聊一聊BRAM IP。

2023-08-29 16:41:49 2605

2605

在給Vivado中的一些IP核進行配置的時候,發現有Shared Logic這一項,這里以Tri Mode Ethernet MAC IP核為例,如圖1所示。

2023-09-06 17:05:12 529

529

Vivado是Xilinx公司2012年推出的新一代集成開發環境,它強調系統級的設計思想及以IP為核心的設計理念,突出IP核在數字系統設計中的作用。

2023-09-17 15:37:31 1060

1060

本文開源一個FPGA高速串行通信項目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收發器,本工程主要是圍繞該IP核采用Vivado提供的例程創建。

2023-10-01 09:48:00 2604

2604

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317

電子發燒友App

電子發燒友App

評論