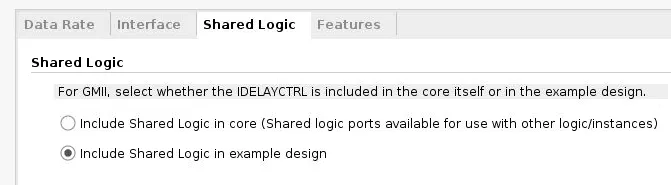

在給Vivado中的一些IP核進行配置的時候,發現有Shared Logic這一項,這里以Tri Mode Ethernet MAC IP核為例,如圖1所示。

圖1 IP核Shared Logic選項配置

之前都是默認選擇“Include Shared Logic in Core”,一直都沒考慮過“Include Shared Logic in Example Design”和“Include Shared Logic in Core”在使用上有什么區別。

從字面意思來看,“Include Shared Logic in Example Design”就是在IP核中不包括共享資源,而“Include Shared Logic in Core”則相反。Shared Logic就是共享邏輯,主要包括時鐘、復位等。當選擇Shared Logic in core時,這些共享的邏輯就會被集成到IP的內部。當選擇Shared Logic in example design時,這些共享邏輯信號作為輸入信號被IP調用。至于為什么叫in example design,是因為Vivado的IP都會提供一個例程,shared logic在example中是對外開放的,可由用戶修改。

圖2 例化多個IP核時shared logic信號共享連接

如圖2所示,左側的 IP 核選擇了將共享資源包含在 IP 核內部,右側的 IP 核則選擇了將共享資源從 IP 核內部去除, 移至 example desgin 中。兩種選項應用場景的區別主要在于:如果工程中只需要例化1個該IP核,就選擇“Include Shared Logic in Core”。若需要例化多個此IP核,就可以令第一個IP選擇“Include Shared Logic in Core”,將共享資源包含在 IP 核內部;其它例化的IP核選擇“Include Shared Logic in Example Design”,將共享資源從 IP 核內部去除,并與第一個IP核信號共享。

-

Mac

+關注

關注

0文章

1116瀏覽量

52576 -

IP核

+關注

關注

4文章

338瀏覽量

50423 -

Vivado

+關注

關注

19文章

828瀏覽量

68166 -

邏輯信號

+關注

關注

0文章

13瀏覽量

3439

發布評論請先 登錄

Vivado IP中的Shared Logic到底是干嘛的

Vivado IP核鎖定的解決辦法分享

Xilinx Vivado的使用詳細介紹(3):使用IP核

Vivado IP核Shared Logic選項配置

Vivado IP核Shared Logic選項配置

評論