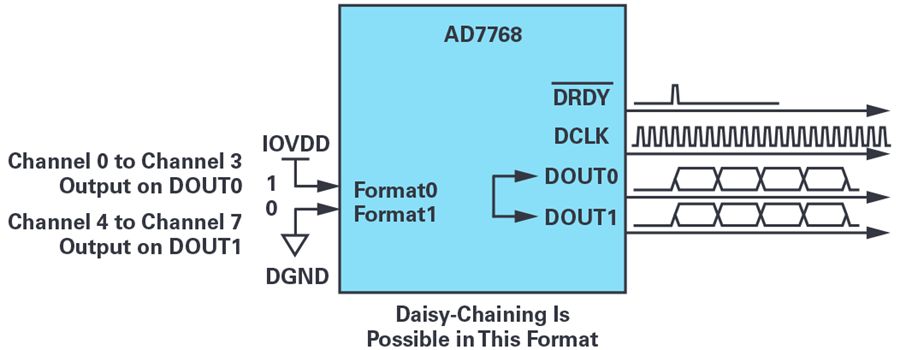

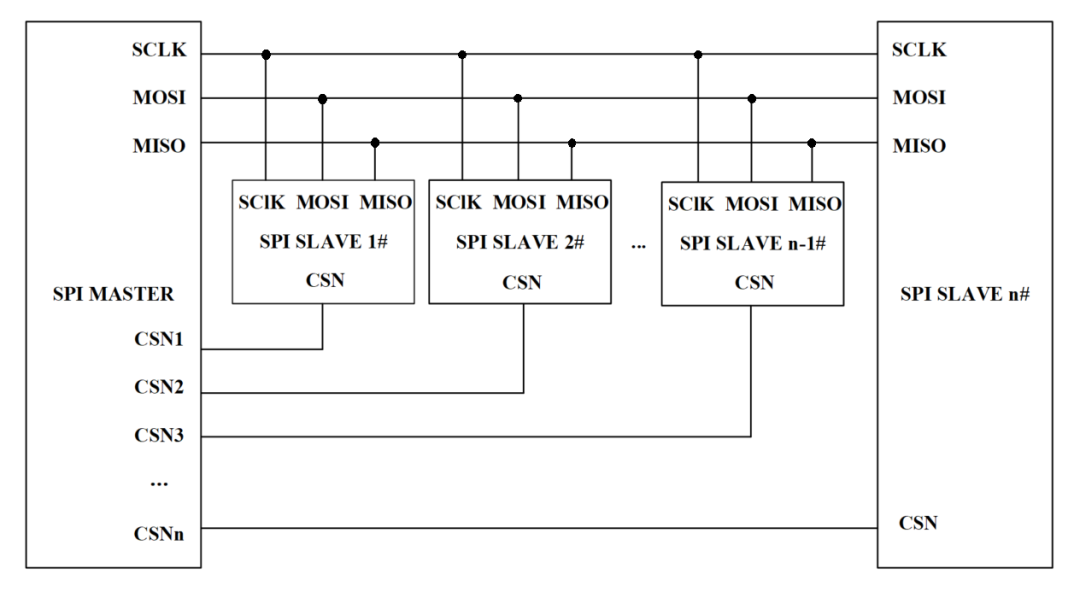

的印刷電路板(PCB)布線(xiàn)簡(jiǎn)單,并且有比并行接口更快的時(shí)鐘速率,因而越來(lái)越受歡迎。而且,使用標(biāo)準(zhǔn)SPI很容易將ADC連接到控制器 。 一些新型ADC具有SPI,但有些ADC具有非標(biāo)準(zhǔn)的3線(xiàn)或4線(xiàn)SPI

2023-12-23 12:25:02 487

487

電子發(fā)燒友網(wǎng)站提供《具有串行I2C接口的實(shí)時(shí)時(shí)鐘1339 數(shù)據(jù)表.pdf》資料免費(fèi)下載

2023-12-21 10:45:31 0

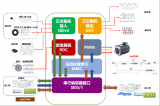

0 01.串行編碼器接口SEI的應(yīng)用場(chǎng)景SEI串行編碼器接口是HPM單片機(jī)獨(dú)創(chuàng)的通信接口外設(shè),可以在同一個(gè)硬件接口上實(shí)現(xiàn)不同類(lèi)型的串行通信協(xié)議的數(shù)據(jù)收發(fā)。是5300精確位置系統(tǒng)的一部分,可以與系統(tǒng)中的其它外設(shè)協(xié)同工作。主要應(yīng)用場(chǎng)景:作為主機(jī),從外

2023-12-20 08:17:33 786

786

是HPM單片機(jī)獨(dú)創(chuàng)的通信接口外設(shè),可以在同一個(gè)硬件接口上實(shí)現(xiàn)不同類(lèi)型的串行通信協(xié)議的數(shù)據(jù)收發(fā)。

2023-12-19 16:54:16 650

650

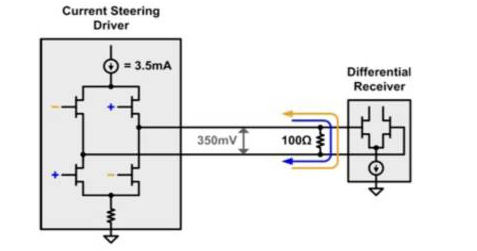

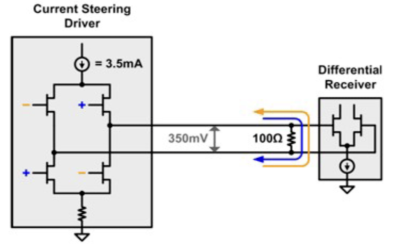

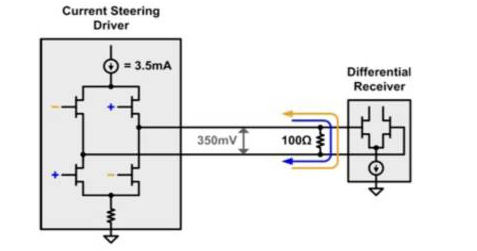

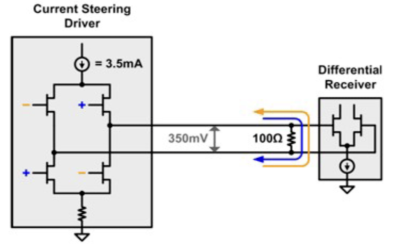

Network)是一種用于汽車(chē)和其他工業(yè)應(yīng)用中的通信協(xié)議。它是一種多主總線(xiàn),允許多個(gè)節(jié)點(diǎn)同時(shí)發(fā)送數(shù)據(jù),具有高可靠性和實(shí)時(shí)性。 RS-485接口:RS-485是一種常見(jiàn)的串行通信協(xié)議,廣泛應(yīng)用于工業(yè)自動(dòng)化、樓宇自動(dòng)化等領(lǐng)域。它采用差分信號(hào)傳輸方式,具有較高的抗干擾能力和可靠性。 二、物理層

2023-12-13 10:50:31 2445

2445 請(qǐng)問(wèn)一下AD7760的并行IO接口和控制IO接口能不能與MCU的IO直接連接呢?MCU的IO電平是3.3V。AD7760看了是差分信號(hào)輸入,有沒(méi)有大神做過(guò)單端輸入呢?誤差這方面怎樣呢?能不能達(dá)到0.001%呢?

2023-12-08 07:06:54

并行總線(xiàn)和串行總線(xiàn)的區(qū)別? 并行總線(xiàn)和串行總線(xiàn)是計(jì)算機(jī)系統(tǒng)中常見(jiàn)的兩種數(shù)據(jù)傳輸方式,它們有著不同的工作原理和應(yīng)用場(chǎng)景。在這篇文章中,我將詳細(xì)介紹并行總線(xiàn)和串行總線(xiàn)的區(qū)別,并探討它們各自的優(yōu)勢(shì)和劣勢(shì)

2023-12-07 16:45:27 1505

1505 上的連接錯(cuò)誤。它使用了一個(gè)標(biāo)準(zhǔn)的 20 針或 14 針接口,并且可以支持多個(gè)設(shè)備之間的串行和并行通信。JTAG 接口廣泛應(yīng)用于電路板級(jí)

2023-12-07 15:29:41 2768

2768 AD2S1210數(shù)據(jù)手冊(cè)中顯示

為什么我采用SPI通信方式,不用的并行輸出接口浮空,實(shí)際DVDD采用5V時(shí),電流竟然有120mA?

請(qǐng)問(wèn)下這個(gè)是為什么?

2023-12-01 08:00:21

應(yīng)用進(jìn)行解析,以便讀者在選擇和使用時(shí)更加得心應(yīng)手。 一、條形液晶屏的主要接口類(lèi)型 1、TTL接口:TTL(Transistor-Transistor Logic)接口是一種并行接口,具有傳輸速度快、控制簡(jiǎn)單等優(yōu)點(diǎn)。它通常用于傳輸數(shù)字信號(hào),適用于要求高速傳輸?shù)膽?yīng)

2023-11-24 16:35:49 504

504 如何同時(shí)實(shí)現(xiàn)串行和并行模式下的數(shù)字接口,完成對(duì)外設(shè)LTC6915的訪(fǎng)問(wèn)

2023-11-14 06:12:01

能好壞。SATA接口介紹SATA(SerialATA)是串行ATA的縮寫(xiě),是一種完全不同于并行ATA的新型硬盤(pán)接口類(lèi)型。SATA接口使用嵌入式時(shí)鐘信號(hào),具備了更強(qiáng)的糾錯(cuò)

2023-11-10 08:07:41 311

311

前的準(zhǔn)備工作。 一、并行接口的工作原理 并行接口是一種數(shù)據(jù)傳輸接口,它能夠同時(shí)傳輸多位的數(shù)據(jù),與串行接口相比具有高速傳輸和處理大量數(shù)據(jù)的優(yōu)勢(shì)。并行接口的數(shù)據(jù)傳輸主要通過(guò)的是多根數(shù)據(jù)線(xiàn)進(jìn)行,每根數(shù)據(jù)線(xiàn)對(duì)應(yīng)一個(gè)數(shù)據(jù)位。 ADC(模數(shù)轉(zhuǎn)換器)將模擬信號(hào)轉(zhuǎn)換

2023-11-07 10:21:45 857

857 計(jì)算機(jī)和單片機(jī)通訊可以采用并行通訊或串行通訊。什么是并行通訊?什么是串行通訊?各有什么特點(diǎn)?

2023-10-27 07:57:06

SerDes(Serialization/Deserialization)是一種在數(shù)字通信系統(tǒng)中提供重要優(yōu)勢(shì)的串行/并行轉(zhuǎn)換電路。

2023-10-20 15:31:24 828

828

RS-485接口是在RS-422基礎(chǔ)上發(fā)展起來(lái)的一種RIA標(biāo)準(zhǔn)串行接口,采用“平衡纏粉驅(qū)動(dòng)”方式

2023-10-16 09:16:01 2595

2595

端高速串行信號(hào)重新轉(zhuǎn)換成低速并行信號(hào)。 ? 采用SerDes技術(shù)的高速串行接口增加了帶寬,減少了信號(hào)數(shù)量,同時(shí)帶來(lái)了諸如減少布線(xiàn)沖突、降低開(kāi)關(guān)噪聲、更低的功耗和封裝成本等許多好處,相比傳統(tǒng)并行總線(xiàn)架構(gòu)有不少的提升。 ? 并行接口與SerDes ? 串行接口和并行接口的發(fā)展

2023-10-12 09:02:14 1623

1623 SWD的接口對(duì)比JTAG接口有什么優(yōu)勢(shì)

2023-10-09 07:09:03

串行數(shù)據(jù)傳輸:因?yàn)樵谛酒瑑?nèi)部數(shù)據(jù)都是并行傳輸?shù)模皇窃谛酒l(fā)送器一端轉(zhuǎn)換為串行形式

2023-10-08 16:15:26 4993

4993

LogiCORE?IPAXI IIC總線(xiàn)接口連接到AMBA?AXI規(guī)范,提供低速、兩線(xiàn)串行總線(xiàn)接口,可連接大量流行的設(shè)備。

2023-09-28 15:56:16 4483

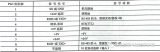

4483 串口是

串行接口的簡(jiǎn)稱(chēng),

串行接口是采用

串行通信方式的

接口。

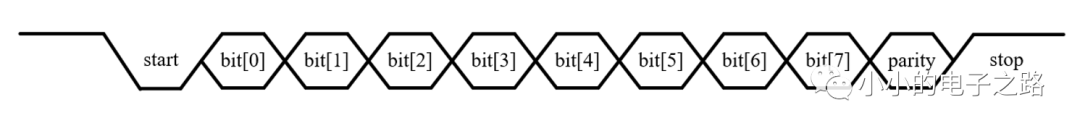

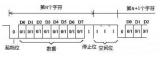

串行通信是一種將需要傳輸?shù)臄?shù)據(jù)由低位到高位一位一位地在一條傳輸線(xiàn)上逐個(gè)傳輸?shù)耐ㄐ欧绞健?/div>

2023-09-26 14:46:49 1510

1510

本書(shū)以Pentium系列微機(jī)為主要背景機(jī),系統(tǒng)全面地介紹了微型計(jì)算機(jī)的硬件技術(shù)及應(yīng)用基礎(chǔ)。本書(shū)為下冊(cè)——微機(jī)接口部分,分為微機(jī)接口技術(shù)概述、并行接口、串行接口、I/O接口中的中斷技術(shù)、I/O接口

2023-09-20 07:10:57

電子發(fā)燒友網(wǎng)站提供《LAN9253和LAN9254的并行接口.pdf》資料免費(fèi)下載

2023-09-19 17:08:06 6

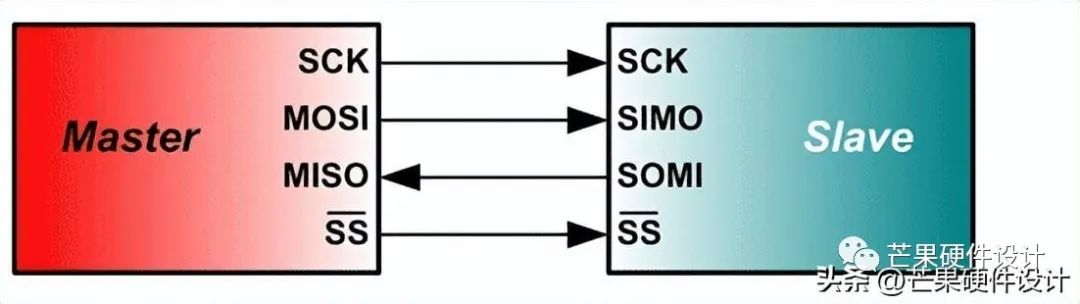

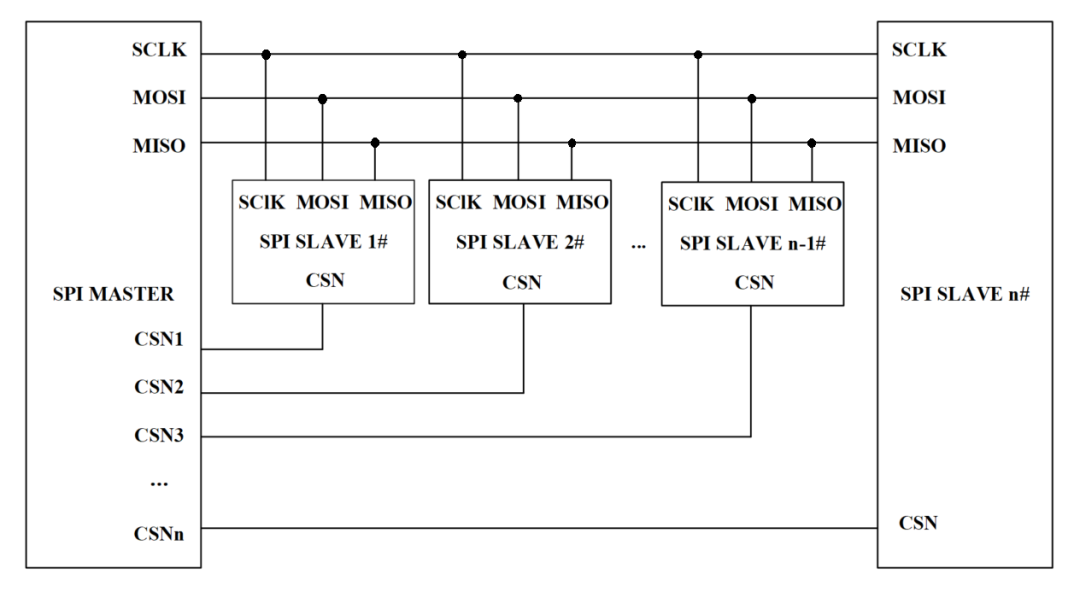

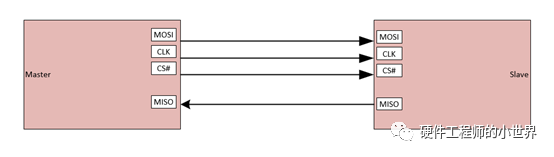

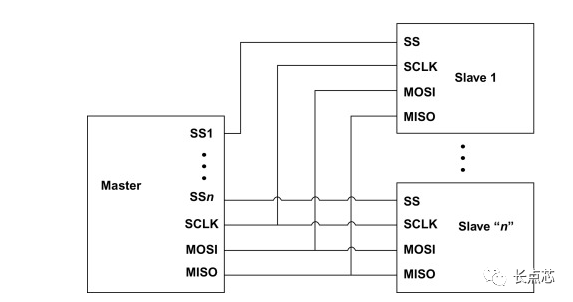

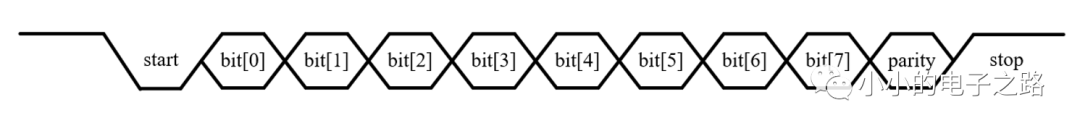

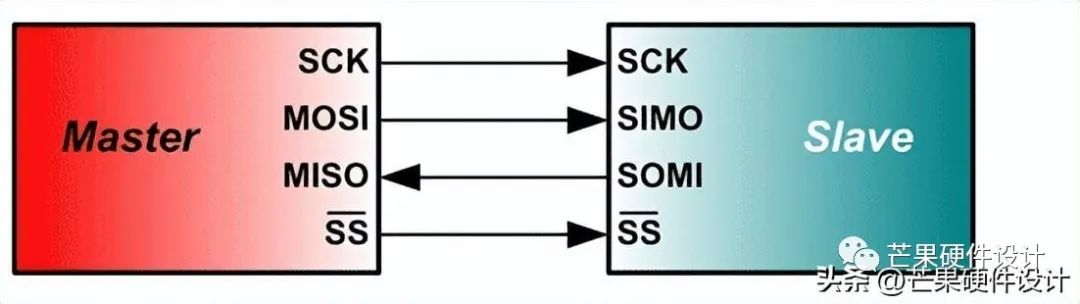

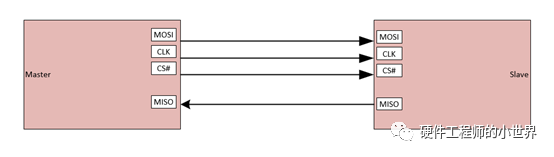

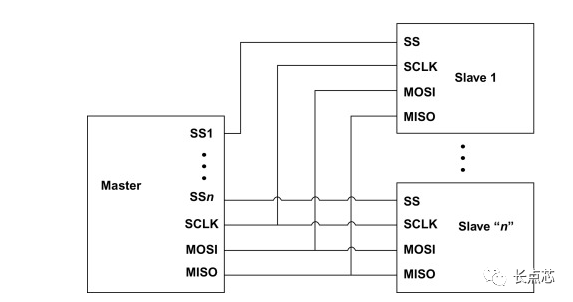

6 SPI(Serial Peripheral interface)串行外圍設(shè)備接口。是微控制器和外圍IC(如傳感器、 ADC、 DAC、移位寄存器、 SRAM等)之間使用最廣泛的接口之一。SPI是一種同步、全雙工、串行接口。來(lái)自主機(jī)或從機(jī)的數(shù)據(jù)在時(shí)鐘上升沿或下降沿同步。

2023-09-15 15:45:56 557

557

本應(yīng)用筆記提供關(guān)于如何連接 STM32MP1 系列產(chǎn)品與 MIPI CSI-2 攝像頭的信息。STM32MP1 系列產(chǎn)品(如 STM32 高性能MCU)可通過(guò)其 DCMI(數(shù)碼相機(jī)模塊接口)并行接口

2023-09-07 08:16:41

【技術(shù)特輯】新唐自有專(zhuān)利 可程序化串行接口PSIO

2023-08-11 15:12:14 448

448

? 串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨(dú)立

2023-07-27 16:10:01 1565

1565

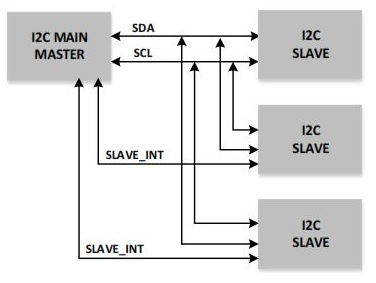

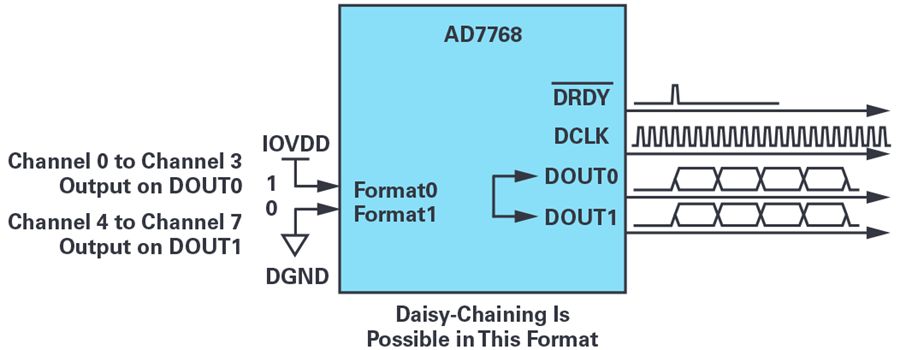

多種串行和并行接口(如SPI、I 2 C 和LVDS)訪(fǎng)問(wèn)或控制ADC。本文將討論打造可靠、完整數(shù)字接口的設(shè)計(jì)技術(shù),包括數(shù)字電源電平和序列、啟動(dòng)期間的I/O 狀態(tài)、接口時(shí)序、信號(hào)質(zhì)量以及數(shù)字活動(dòng)導(dǎo)致的誤差。 數(shù)字I/O 電源電平和序列 多數(shù)SAR ADC 都提供獨(dú)立的數(shù)字I/

2023-07-20 18:05:08 875

875

串口是串行接口(serial port)的簡(jiǎn)稱(chēng),也稱(chēng)為串行通信接口或COM接口。

2023-07-19 14:13:54 6860

6860

USB接口指的是通用串行總線(xiàn)(Universal Serial Bus)接口,而Type-C接口是USB規(guī)范中一種特定的連接器類(lèi)型。

2023-07-13 14:25:39 7743

7743 串行通信適合長(zhǎng)距離、抗干擾要求高的場(chǎng)景,而并行通信則適合高速、實(shí)時(shí)性要求高的場(chǎng)景。

2023-06-29 17:50:10 1073

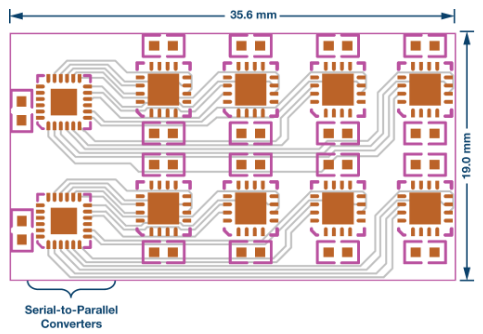

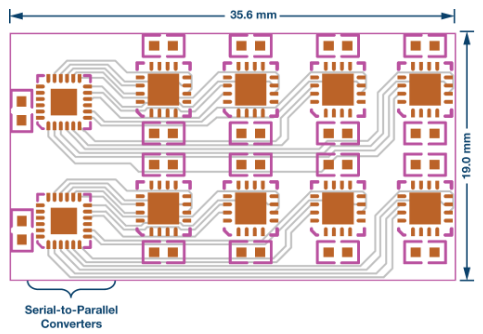

1073 設(shè)計(jì)一個(gè)要求高通道密度的系統(tǒng)時(shí),例如在測(cè)試儀器儀表中,電路板上通常需要包括大量開(kāi)關(guān)。當(dāng)使用并行接口控制的開(kāi)關(guān)時(shí),控制開(kāi)關(guān)所需的邏輯線(xiàn)路以及用于生成GPIO控制信號(hào)的串行轉(zhuǎn)并行轉(zhuǎn)換器會(huì)占用很大

2023-06-16 17:48:51 578

578

新唐M480系列提供的EBI并行數(shù)據(jù)接口的傳輸速率能達(dá)到多少(數(shù)據(jù)手冊(cè)好像沒(méi)有說(shuō)明)?

2023-06-14 07:09:43

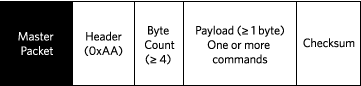

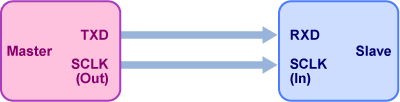

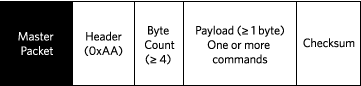

簡(jiǎn)單串行接口(SSI)是一種二進(jìn)制協(xié)議,用于與模擬嵌入式測(cè)量設(shè)備(78M6610+LMU、78M6610+PSU和MAX78630+PPM)通信。

2023-06-13 15:37:43 502

502

以PCIE和SATA為例,時(shí)鐘信息通過(guò)8b/10b編碼已經(jīng)集成在數(shù)據(jù)流里面,數(shù)據(jù)本身經(jīng)過(guò)加擾,不可能有多于5個(gè)0或者5個(gè)1的長(zhǎng)串(利于時(shí)鐘恢復(fù)),也不存在周期性(避免頻譜集中)。這樣,通過(guò)數(shù)據(jù)流的沿變可以直接用PLL恢復(fù)出時(shí)鐘,再用恢復(fù)的時(shí)鐘采集數(shù)據(jù)流。

2023-06-06 10:20:52 909

909

現(xiàn)代社會(huì)很多電子產(chǎn)品都有接口,接口的設(shè)計(jì)規(guī)格是怎么樣的,接口有串行接口和并行接口,下面我們將圍繞串行接口和并行接口的區(qū)別這一中心進(jìn)行討論。 串行接口和并行接口的區(qū)別: 串行接口 串行接口,簡(jiǎn)稱(chēng)串口

2023-06-05 11:36:03 1336

1336 RT,看介紹,基本常用串型接口資源很豐富,在并口上的支持怎么樣?

2023-06-02 10:20:52

串行接口的速率會(huì)比并行快,可以從下面四個(gè)方面考慮: ①高速串口不需要時(shí)鐘信號(hào)來(lái)同步數(shù)據(jù)流,也就沒(méi)有時(shí)鐘周期性的邊沿,頻譜不會(huì)集中,所以噪聲干擾少很多。 以PCIE和SATA為例,時(shí)鐘信息通過(guò)8b

2023-05-31 14:19:18 1228

1228

SPI 全稱(chēng)為 Serial Peripheral Interface,譯為串行外設(shè)接口。它是 Motorola 公司推出的一種相對(duì)高速的同步、全雙工的通信總線(xiàn)協(xié)議。

2023-05-29 15:40:23 784

784

。

微型計(jì)算機(jī)系統(tǒng)中最基本的信息交換方式。

并行傳遞的信息不要求固定的格式。按位走,不需要格式的。

并行接口的數(shù)據(jù)傳輸率比串行接口快8倍,標(biāo)準(zhǔn)并行接口的數(shù)據(jù)傳輸率理論值為1Mbps(兆比特/秒)。現(xiàn)在更高

2023-05-12 16:31:18

基于ATmega8單片機(jī)同步串行接口SPI的C語(yǔ)言編程源程序

2023-05-05 09:17:37 1

1 并行接口,稱(chēng)為并口。并行端口使用25針D型連接頭。所謂“并行”是指通過(guò)并行線(xiàn)路同時(shí)傳輸8位數(shù)據(jù),從而大大提高了數(shù)據(jù)傳輸速度,但是并行傳輸線(xiàn)路的長(zhǎng)度受到限制,因?yàn)殚L(zhǎng)度增加,干擾會(huì)增加,并且數(shù)據(jù)容易出錯(cuò)。目前,并行接口主要用作打印機(jī)端口等。

2023-04-27 10:38:10 3127

3127 SPI是Serial Peripheral interface的縮寫(xiě),是一種串行外設(shè)接口。全雙工通信,有4根信號(hào)線(xiàn),在MCU、SOC、FLASH、DSP等芯片上常見(jiàn)。

2023-04-24 17:29:44 1169

1169

串口的全程為串行接口,也稱(chēng)為串行通信接口,是采用串行通信方式的擴(kuò)展接口。與串口對(duì)應(yīng)的并行接口,例如高速AD和DA,

2023-04-21 11:18:31 555

555 電機(jī)驅(qū)動(dòng)芯片 電源電壓8V~52V 輸出電流2.8A 并行接口

2023-04-06 10:20:43

今天討論的SPI接口是一種十分常用的片外通信接口,經(jīng)常作為芯片與片外存儲(chǔ)器(多為 serial nand flash )的通信接口。同時(shí),硬件物理接口也是應(yīng)屆生面試時(shí)被提問(wèn)最多的問(wèn)題之一。有意在畢業(yè)后從事計(jì)算機(jī)硬件行業(yè)的朋友們可以在準(zhǔn)備應(yīng)聘的時(shí)候多多儲(chǔ)備這方面的知識(shí)。

2023-04-04 15:15:26 4640

4640

MADR-011007用于 GaAs FETS 的 40 位串行到并行驅(qū)動(dòng)器MADR-011007 是一款 40 位串行到并行驅(qū)動(dòng)器,采用低成本 6 mm 48 引腳 PQFN 塑料封裝。它被設(shè)計(jì)為

2023-03-31 13:41:08

一、SSMII接口 ??SSMII即Serial Sync MII,叫串行同步接口,跟SMII接口很類(lèi)似,只是收發(fā)使用獨(dú)立的參考時(shí)鐘和同步時(shí)鐘,不再像SMII那樣收發(fā)共用參考時(shí)鐘和同步時(shí)鐘,傳輸距離

2023-03-29 15:18:11 982

982 3.3 V并行接口收發(fā)器/緩沖器

2023-03-28 18:41:49

2.5 V至5.5 V, 500 uA,并行接口equad電壓輸出8 /10 /12位dac

2023-03-28 18:29:05

3.3 V并行接口收發(fā)器/緩沖器

2023-03-28 15:03:50

32M BIT 串行接口閃存

2023-03-28 13:02:29

32M BIT 串行接口閃存

2023-03-28 13:02:29

8M BIT 串行接口閃存

2023-03-28 13:02:29

128M BIT 串行接口閃存

2023-03-28 13:02:28

由于其相對(duì)簡(jiǎn)單和低硬件開(kāi)銷(xiāo)(與并行接口相比),串行通信在電子行業(yè)中被廣泛使用。今天,最流行的串行通信標(biāo)準(zhǔn)當(dāng)然是EIA/TIA-232-E規(guī)范。該標(biāo)準(zhǔn)由電子工業(yè)協(xié)會(huì)和電信工業(yè)協(xié)會(huì)(EIA/TIA)制定

2023-03-28 11:11:05 4792

4792

16位,2msps,單極輸入,微功率采樣模數(shù)轉(zhuǎn)換器,具有并行接口和參考

2023-03-24 15:06:30

16位,2msps,單極性差分輸入,微功率采樣模數(shù)轉(zhuǎn)換器,具有并行接口和參考

2023-03-24 15:06:30

16位,2msps,單極性差分輸入,微功率采樣模數(shù)轉(zhuǎn)換器,具有并行接口和參考

2023-03-24 15:06:24

16位,4msps,偽雙極,全差分輸入,微功耗具有并行接口的模數(shù)轉(zhuǎn)換器采樣,參考

2023-03-23 07:47:21

USB通用串行接口芯片

2023-03-23 04:59:11

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論