2021 年,JEDEC 宣布發(fā)布 JESD79-5 DDR5 SDRAM 標(biāo)準(zhǔn),標(biāo)志著行業(yè)向 DDR5 dual-inline memory modules (DIMM) 的過(guò)渡。

2024-03-17 09:50:37 431

431

DDR 代表雙倍數(shù)據(jù)速率double data rate,GDDR 代表圖形雙倍數(shù)據(jù)速率graphics double data rate。

2024-03-17 09:24:53 236

236

288 位置 DIMM DDR5 SDRAM 個(gè)插口 表面貼裝型

2024-03-14 20:41:22

電子發(fā)燒友網(wǎng)站提供《完整的DDR2、DDR3和DDR3L內(nèi)存電源解決方案同步降壓控制器TPS51216數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-13 13:58:12 0

0 電子發(fā)燒友網(wǎng)站提供《適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準(zhǔn)的TPS51206 2A峰值灌電流/拉電流DDR終端穩(wěn)壓器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-13 13:53:03 0

0 電子發(fā)燒友網(wǎng)站提供《具有同步降壓控制器、2A LDO和緩沖基準(zhǔn)的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲(chǔ)器電源解決方案數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-13 11:24:34 0

0 電子發(fā)燒友網(wǎng)站提供《具有同步降壓控制器、2A LDO和緩沖基準(zhǔn)的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內(nèi)存電源解決方案數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-13 11:13:44 0

0 電子發(fā)燒友網(wǎng)站提供《完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-13 10:16:45 0

0 DDR一致性測(cè)試的操作步驟? DDR(雙數(shù)據(jù)率)一致性測(cè)試是對(duì)DDR內(nèi)存模塊進(jìn)行測(cè)試以確保其性能和可靠性。在進(jìn)行DDR一致性測(cè)試時(shí),需要遵循一系列的操作步驟,以保證測(cè)試的準(zhǔn)確性和完整性。下面將詳細(xì)

2024-02-01 16:24:52 209

209 DDR6和DDR5內(nèi)存的區(qū)別有多大?怎么選擇更好? DDR6和DDR5是兩種不同的內(nèi)存技術(shù),它們各自在性能、功耗、帶寬等方面都有不同的特點(diǎn)。下面將詳細(xì)比較這兩種內(nèi)存技術(shù),以幫助你選擇更適合

2024-01-12 16:43:05 2863

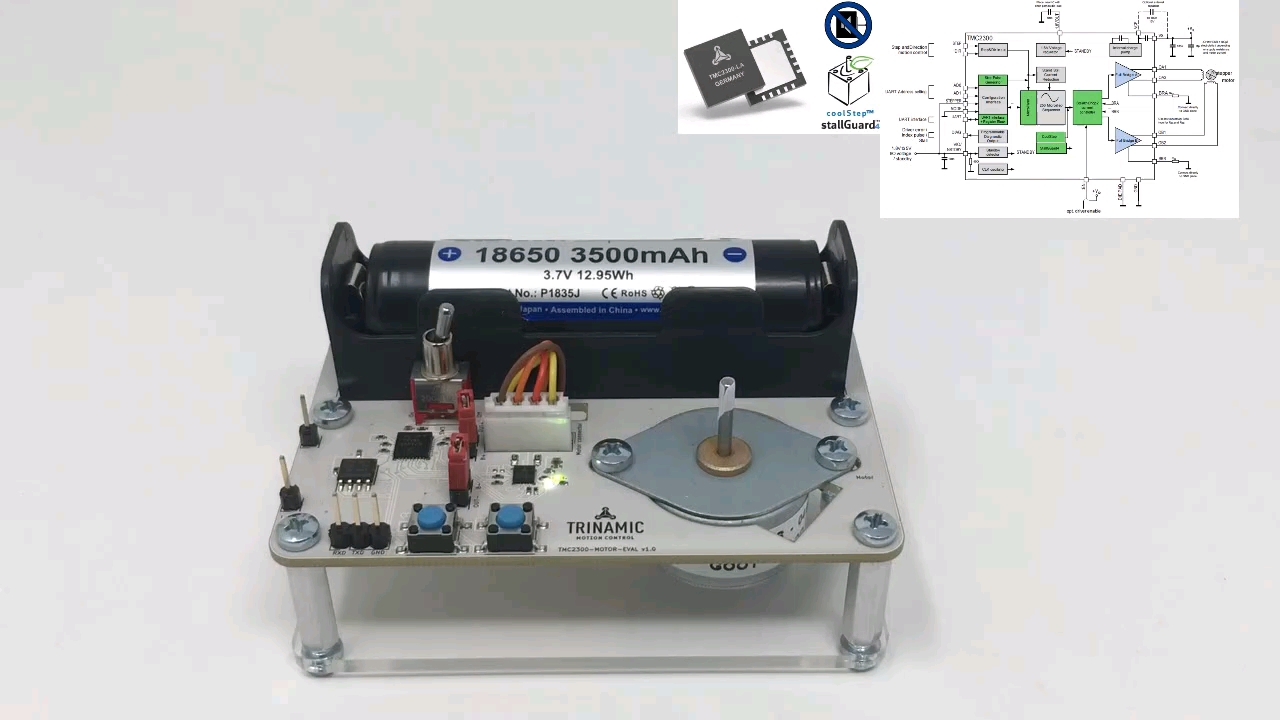

2863 深圳市港禾科技有限公司產(chǎn)品描述NSD8306 – Q1是一款多通道半橋驅(qū)動(dòng)芯片,內(nèi)部集成6通道半橋,通過(guò)靈活配置,芯片可以支持多種不同的負(fù)載類型包括直流有刷電機(jī),步進(jìn)電機(jī),繼電器和LED等。該芯片

2024-01-09 13:42:53

深圳市港禾科技有限公司產(chǎn)品描述NSD8306 – Q1是一款多通道半橋驅(qū)動(dòng)芯片,內(nèi)部集成6通道半橋,通過(guò)靈活配置,芯片可以支持多種不同的負(fù)載類型包括直流有刷電機(jī),步進(jìn)電機(jī),繼電器和LED等。該芯片

2024-01-09 13:39:33

深圳市港禾科技有限公司產(chǎn)品描述NSD8308 – Q1是一款多通道半橋驅(qū)動(dòng)芯片,內(nèi)部集成8通道半橋,通過(guò)靈活配置,芯片可以支持多種不同的負(fù)載類型包括直流有刷電機(jī),步進(jìn)電機(jī),繼電器和LED等。該芯片

2024-01-08 14:08:07

深圳市港禾科技有限公司產(chǎn)品描述NSD7312A是一款直流有刷電機(jī)驅(qū)動(dòng)芯片,芯片內(nèi)置功率N-MOSFET并為功率級(jí)提供全方位保護(hù)包括供電欠壓保護(hù),過(guò)流保護(hù),過(guò)溫保護(hù),當(dāng)保護(hù)功能觸發(fā)后,芯片

2024-01-08 14:03:50

深圳市港禾科技有限公司產(chǎn)品描述NSD7312-Q1是一款直流有刷電機(jī)驅(qū)動(dòng)芯片,芯片內(nèi)置功率N-MOSFET并為功率級(jí)提供全方位保護(hù)包括供電欠壓保護(hù),過(guò)流保護(hù),過(guò)溫保護(hù),當(dāng)保護(hù)功能觸發(fā)后,芯片

2024-01-08 13:59:18

深圳市港禾科技有限公司產(chǎn)品描述NSD7312A是一款直流有刷電機(jī)驅(qū)動(dòng)芯片,芯片內(nèi)置功率N-MOSFET并為功率級(jí)提供全方位保護(hù)包括供電欠壓保護(hù),過(guò)流保護(hù),過(guò)溫保護(hù),當(dāng)保護(hù)功能觸發(fā)后,芯片

2024-01-08 13:56:04

深圳市港禾科技有限公司產(chǎn)品描述NSD7312是一款直流有刷電機(jī)驅(qū)動(dòng)芯片,芯片內(nèi)置功率N-MOSFET并為功率級(jí)提供全方位保護(hù)包括供電欠壓保護(hù),過(guò)流保護(hù),過(guò)溫保護(hù),當(dāng)保護(hù)功能觸發(fā)后,芯片

2024-01-08 13:44:52

深圳市港禾科技有限公司產(chǎn)品描述NSD7310A是一款直流有刷電機(jī)驅(qū)動(dòng)芯片,芯片內(nèi)置功率N-MOSFET并為功率級(jí)提供全方位保護(hù)包括供電欠壓保護(hù),過(guò)流保護(hù),過(guò)溫保護(hù)。該產(chǎn)品可提供3.6A峰值電流,支持

2024-01-08 13:35:41

深圳市港禾科技有限公司產(chǎn)品描述NSD7310是一款直流有刷電機(jī)驅(qū)動(dòng)芯片,芯片內(nèi)置功率N-MOSFET并為功率級(jí)提供全方位保護(hù)包括供電欠壓保護(hù),過(guò)流保護(hù),過(guò)溫保護(hù)。該產(chǎn)品可提供3.6A峰值電流,支持

2024-01-08 11:59:13

深圳市港禾科技有限公司產(chǎn)品描述NSD7310是一款直流有刷電機(jī)驅(qū)動(dòng)芯片,芯片內(nèi)置功率N-MOSFET并為功率級(jí)提供全方位保護(hù)包括供電欠壓保護(hù),過(guò)流保護(hù),過(guò)溫保護(hù)。該產(chǎn)品可提供3.6A峰值電流,支持

2024-01-08 11:54:56

DDR5已經(jīng)開(kāi)始商用,但是有的產(chǎn)品還才開(kāi)始使用DDR4。本文分享一些DDR4的測(cè)試內(nèi)容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以達(dá)到 3200Mb/s,這樣高速的信號(hào),對(duì)信號(hào)完整性的要求就更加嚴(yán)格,JESD79‐4 規(guī)范也對(duì) DDR4 信號(hào)的測(cè)量提出了一些要求。

2024-01-08 09:18:24 463

463

DDR接口速率越來(lái)越高,每一代產(chǎn)品都在挑戰(zhàn)工藝的極限,對(duì)DDR PHY的訓(xùn)練要求也越來(lái)越嚴(yán)格。本文從新銳IP企業(yè)芯耀輝的角度,談?wù)?b class="flag-6" style="color: red">DDR PHY訓(xùn)練所面臨的挑戰(zhàn),介紹芯耀輝DDR PHY訓(xùn)練的主要過(guò)程和優(yōu)勢(shì),解釋了芯耀輝如何解決DDR PHY訓(xùn)練中的問(wèn)題。

2024-01-05 10:27:34 519

519

LPDDR5和DDR5是兩種不同類型的內(nèi)存,它們?cè)跁r(shí)序和性能方面有一些差異。盡管它們都是最新一代的內(nèi)存標(biāo)準(zhǔn),但它們面向不同的應(yīng)用場(chǎng)景,并且在設(shè)計(jì)上有一些不同。 首先,讓我們來(lái)了解一下LPDDR5

2024-01-04 10:22:06 1162

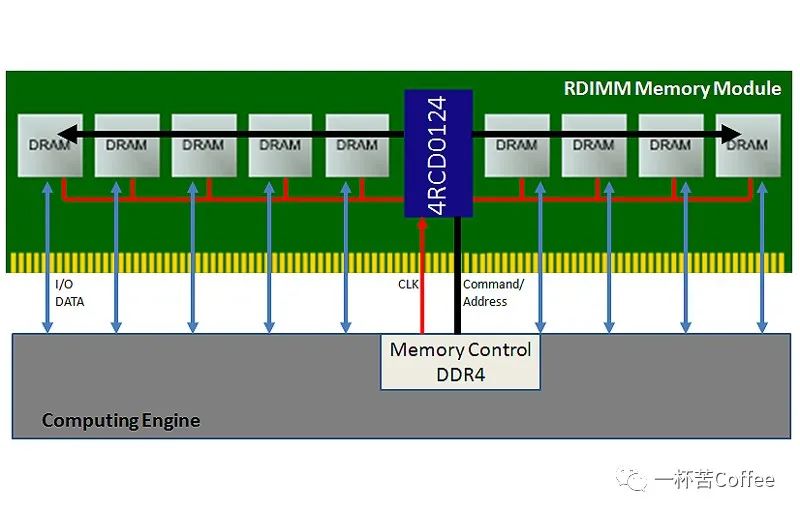

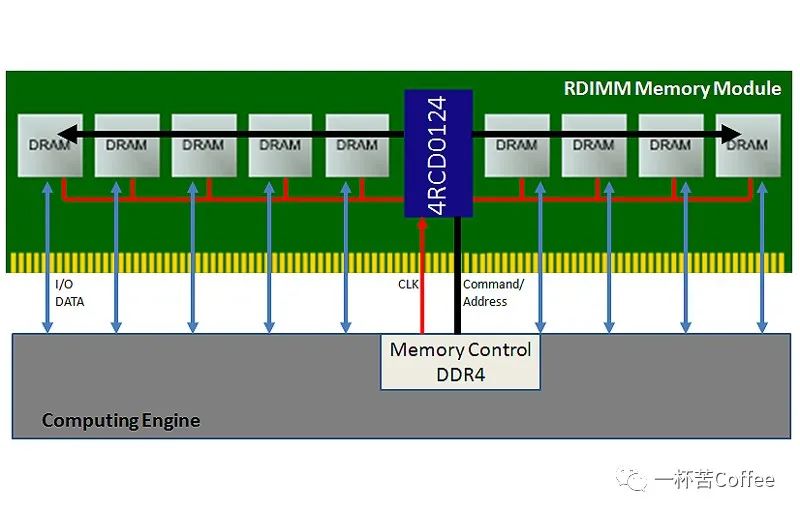

1162 近日,瀾起科技宣布推出DDR5第四子代寄存時(shí)鐘驅(qū)動(dòng)器芯片(DDR5 RCD04),該芯片支持高達(dá)7200 MT/s的數(shù)據(jù)速率,較DDR5第一子代RCD速率提升50%,

2024-01-04 09:26:58 289

289 DDR加終端匹配電阻和不加信號(hào)質(zhì)量的區(qū)別? DDR(雙倍數(shù)據(jù)傳輸速率)是一種常用于計(jì)算機(jī)內(nèi)存的高速數(shù)據(jù)傳輸技術(shù)。在DDR中,終端匹配電阻和信號(hào)質(zhì)量是對(duì)于數(shù)據(jù)傳輸穩(wěn)定性至關(guān)重要的兩個(gè)方面。下面將詳細(xì)

2023-12-29 13:54:22 316

316 上次我們對(duì)不加端接電阻和加端接電阻之后的仿真結(jié)果做了分析之后我們得出在DDR采用菊花鏈拓?fù)浣Y(jié)構(gòu)的時(shí)候是需要加端接電阻的,這次我們看看DDR末端的端接電阻距離最后一片DDR遠(yuǎn)一點(diǎn)效果好一些還是近一點(diǎn)效果好一些。

2023-12-28 16:55:13 598

598

請(qǐng)問(wèn)SR電機(jī)和無(wú)刷電機(jī)有什么區(qū)別?

2023-12-26 06:30:12

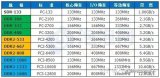

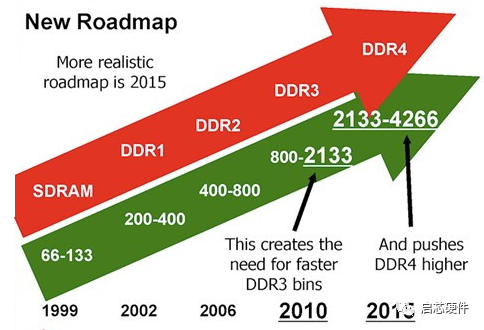

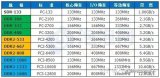

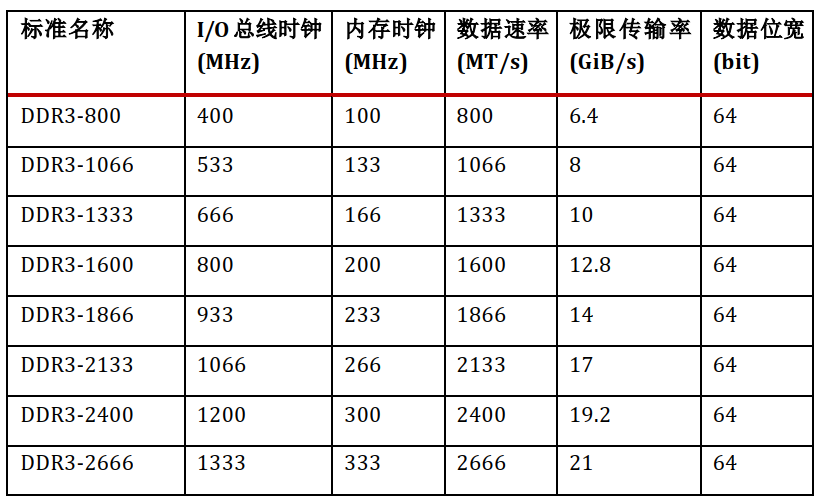

時(shí)鐘頻率:可通過(guò)倍頻技術(shù)升級(jí)的核心頻率。時(shí)鐘頻率可以理解為IO Buffer的實(shí)際工作頻率,DDR2中時(shí)鐘頻率為核心頻率的2倍,DDR3 DDR4中時(shí)鐘頻率為核心頻率的4倍。

2023-12-25 18:18:47 1188

1188

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2 LTP5070是一款H橋有刷直流電機(jī)驅(qū)動(dòng)器,內(nèi)部具有集成的H橋驅(qū)動(dòng)電路和控制電路,能夠控制電機(jī)高達(dá)3.5 A的雙向峰值電流,其最大工作電壓為36V。可通過(guò)輸入端口IN1和IN2輸入PWM信號(hào),控制

2023-12-13 16:27:35

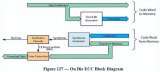

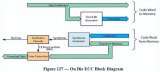

隨著DDR5信號(hào)速率的增加和芯片生產(chǎn)工藝難度的加大,DRAM內(nèi)存出現(xiàn)單位錯(cuò)誤的風(fēng)險(xiǎn)也隨之增加,為進(jìn)一步改善內(nèi)存信道,糾正DRAM芯片中可能出現(xiàn)的位錯(cuò)誤,DDR5引入了片上ECC技術(shù),將ECC集成到DDR5芯片內(nèi)部,提高可靠性并降低風(fēng)險(xiǎn),同時(shí)還能降低缺陷率。

2023-11-30 14:49:31 106

106

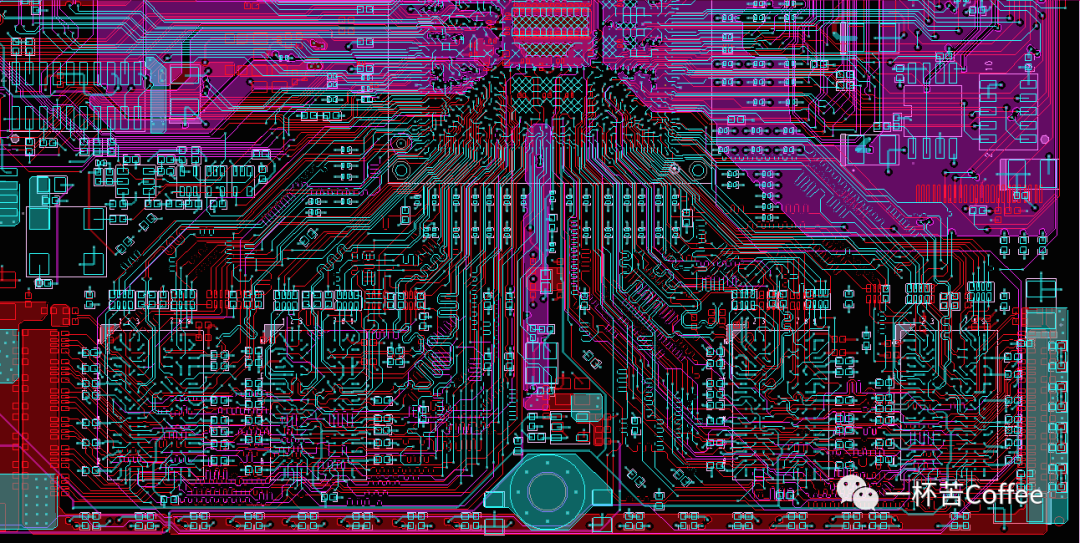

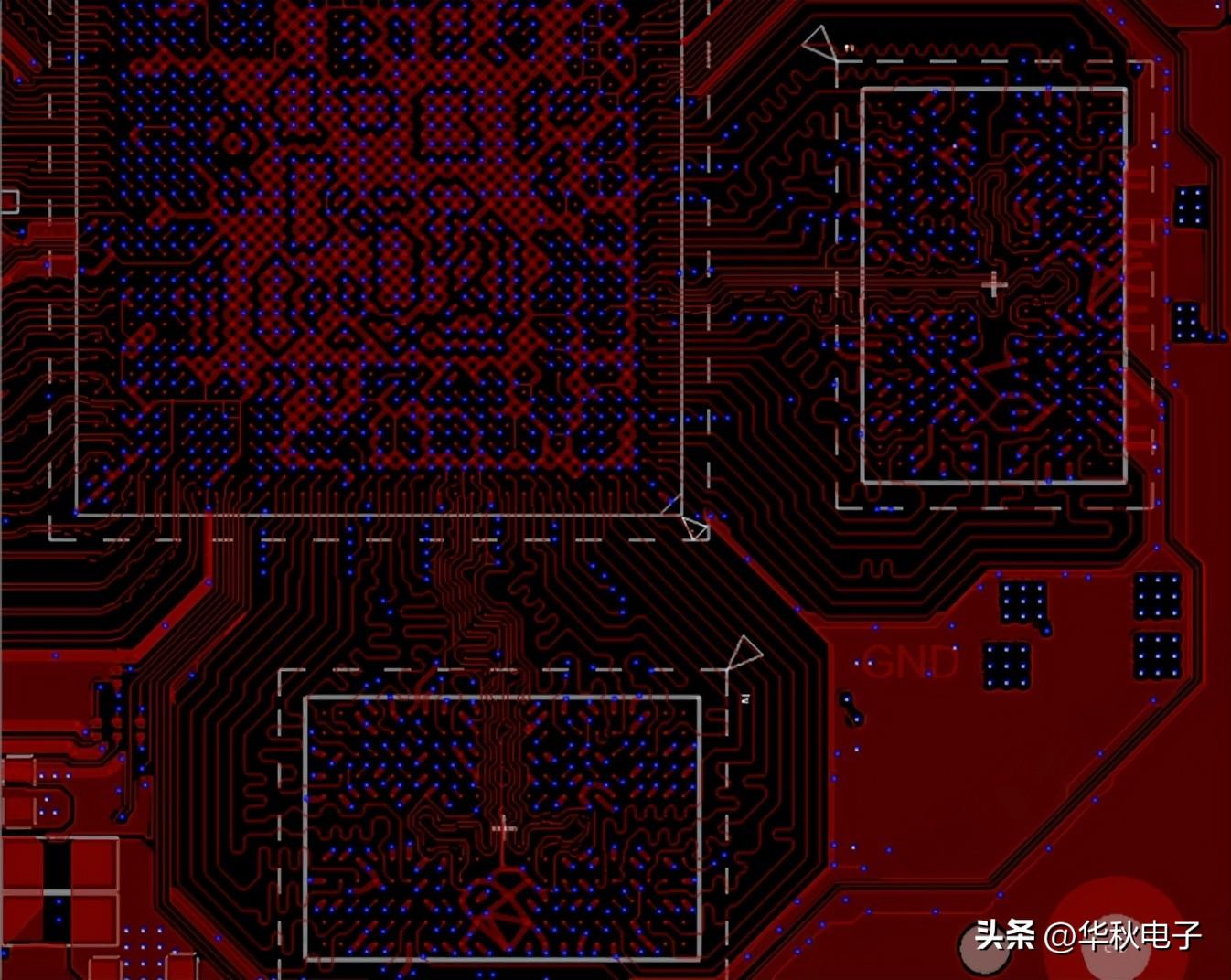

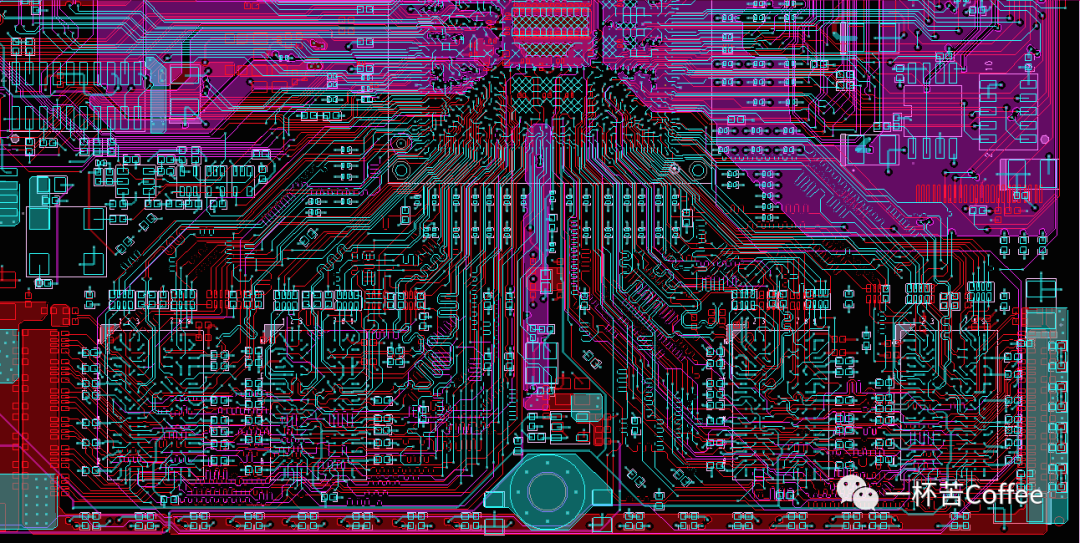

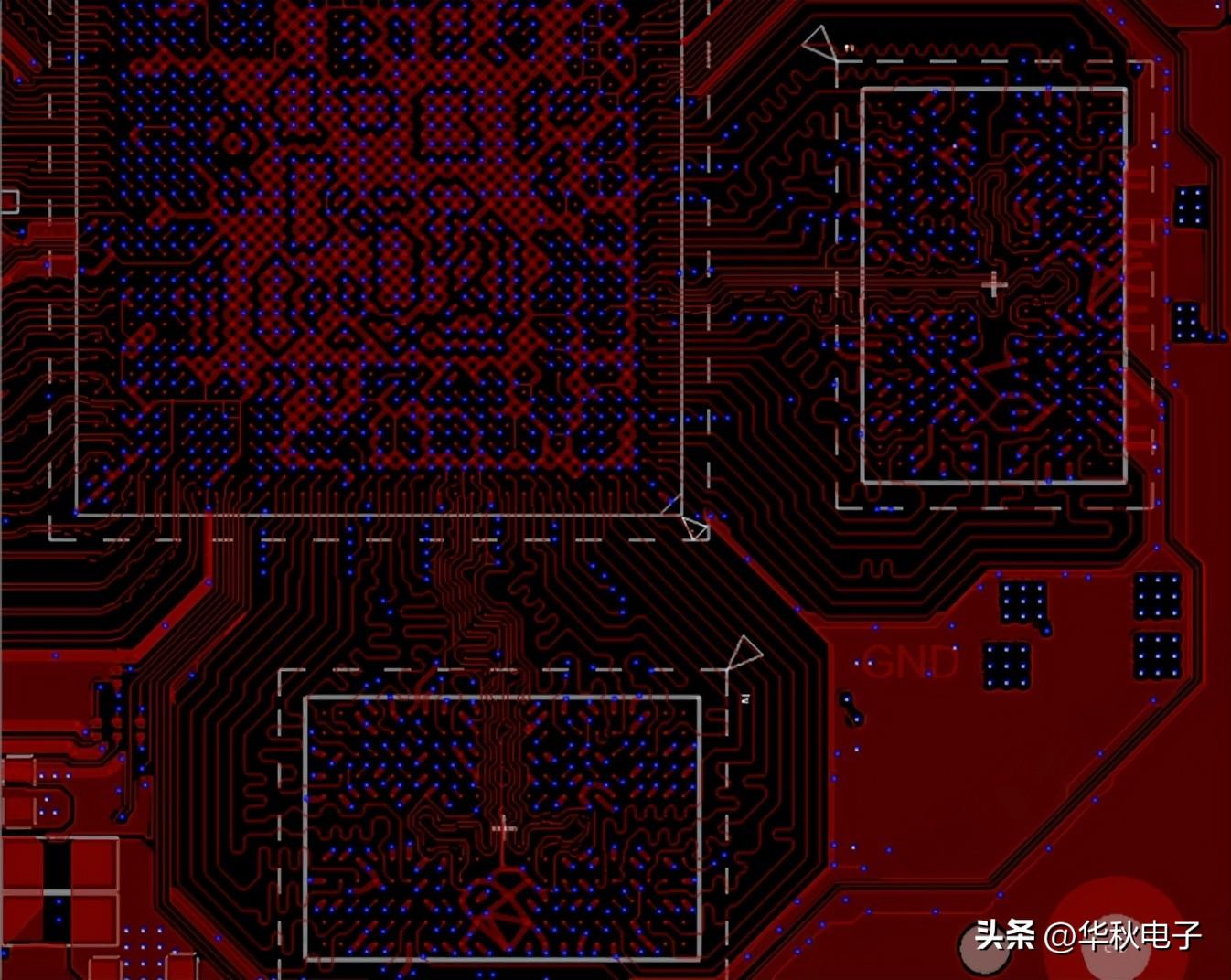

DDR4(第四代雙倍數(shù)據(jù)速率同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器)是一種高帶寬的存儲(chǔ)器,今天主要講述一下DDR4在Layout過(guò)程中的一些細(xì)節(jié)。在DDR的設(shè)計(jì)過(guò)程中,DDR的Layout是十分重要的環(huán)節(jié)。

2023-11-29 15:39:10 1476

1476

本文主要講述一下DDR從0到1設(shè)計(jì)的整個(gè)設(shè)計(jì)的全過(guò)程。

2023-11-27 16:28:11 3715

3715

VTT電源對(duì)DDR有什么作用?

2023-11-27 16:20:14 579

579

對(duì)于ddr5市場(chǎng)的發(fā)展,威剛表示,現(xiàn)階段觀察到需求端春燕來(lái)臨,主要來(lái)自pc,隨著顧客需求的明顯好轉(zhuǎn)和pc內(nèi)存內(nèi)容的提高,明年上半年ddr5將超過(guò)ddr4,形成黃金交叉。目前在現(xiàn)貨市場(chǎng)上,ddr5的單價(jià)比ddr4高4-50%,從威強(qiáng)的情況來(lái)看,ddr5比重的上升有助于總利潤(rùn)率。

2023-11-24 10:38:38 217

217 法人方面解釋說(shuō):“標(biāo)準(zhǔn)型dram和nand目前由三星、sk hynix、美光等跨國(guó)企業(yè)主導(dǎo),因此,中臺(tái)灣企業(yè)在半導(dǎo)體制造方面無(wú)法與之抗衡。”在ddr3 ddr3的情況下,臺(tái)灣制造企業(yè)表現(xiàn)出強(qiáng)勢(shì)。ddr3的價(jià)格也隨之上漲,給臺(tái)灣半導(dǎo)體企業(yè)帶來(lái)了很大的幫助。

2023-11-14 11:29:36 405

405 目前有微型四軸,也有像小米、大疆的四軸飛行器。

今天無(wú)刷的先不談,只談有刷的空心杯電機(jī)。

1、目前用在四軸飛行器上的空心杯電機(jī)電機(jī)有哪些型號(hào)?

2、每種型號(hào)空心杯電機(jī)的最大升力好多、消耗電流多少?

電機(jī)與槳葉怎么選型,有什么關(guān)系,升力應(yīng)當(dāng)怎么計(jì)算?

2023-11-06 06:54:53

DDR4和DDR3內(nèi)存都有哪些區(qū)別? 隨著計(jì)算機(jī)的日益發(fā)展,內(nèi)存也越來(lái)越重要。DDR3和DDR4是兩種用于計(jì)算機(jī)內(nèi)存的標(biāo)準(zhǔn)。隨著DDR4內(nèi)存的逐漸普及,更多的人開(kāi)始對(duì)兩者有了更多的關(guān)注。 DDR

2023-10-30 09:22:00 3893

3893 DDR3是2007年推出的,預(yù)計(jì)2022年DDR3的市場(chǎng)份額將降至8%或以下。但原理都是一樣的,DDR3的讀寫(xiě)分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫(xiě)分離的方法。

2023-10-18 16:03:56 516

516

異步電機(jī)對(duì)比同步電機(jī)有什么優(yōu)點(diǎn)

2023-10-11 06:21:14

內(nèi)轉(zhuǎn)子電機(jī)對(duì)比外轉(zhuǎn)子電機(jī)有什么優(yōu)勢(shì)

2023-10-09 07:53:20

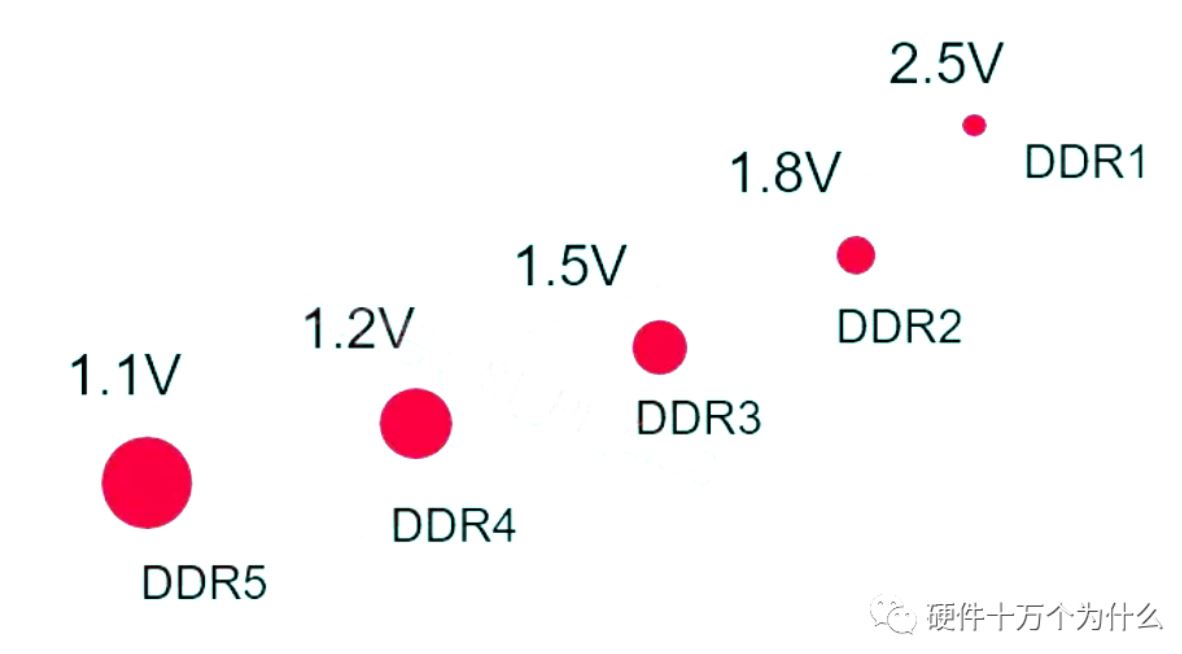

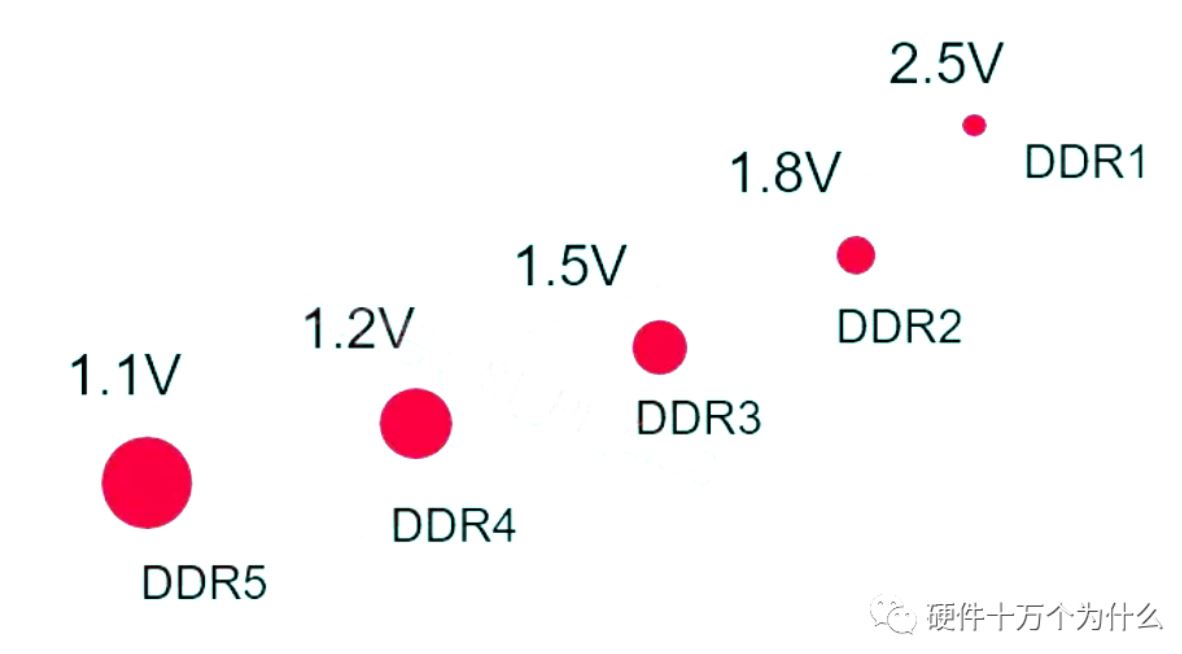

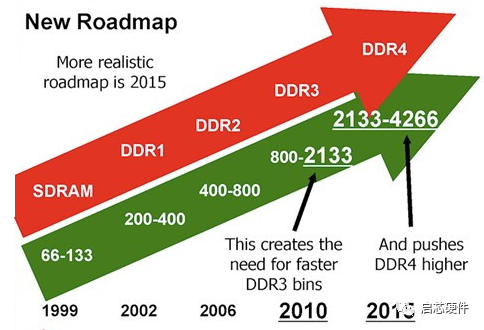

DDR存儲(chǔ)器發(fā)展的主要方向一言以蔽之,是更高速率,更低電壓,更密的存儲(chǔ)密度,從而實(shí)現(xiàn)更好的性能。

2023-10-01 14:03:00 488

488

摘要:本文將對(duì)DDR3和DDR4兩種內(nèi)存技術(shù)進(jìn)行詳細(xì)的比較,分析它們的技術(shù)特性、性能差異以及適用場(chǎng)景。通過(guò)對(duì)比這兩種內(nèi)存技術(shù),為讀者在購(gòu)買和使用內(nèi)存產(chǎn)品時(shí)提供參考依據(jù)。

2023-09-27 17:42:10 1088

1088 DDR4 3200和3600是內(nèi)存模塊的頻率標(biāo)準(zhǔn),表示其頻率值,具有以下差異

2023-09-26 15:24:18 8986

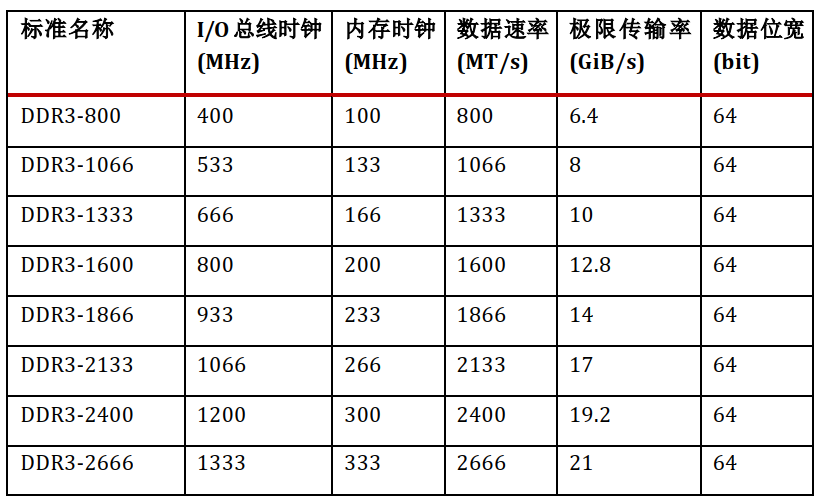

8986 我們?cè)谫IDDR內(nèi)存條的時(shí)候,經(jīng)常會(huì)看到這樣的標(biāo)簽DDR3-1066、DDR3-2400等,這些名稱都有什么含義嗎?請(qǐng)看下表。

2023-09-26 11:35:33 1923

1923

相對(duì)于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內(nèi)存下部設(shè)計(jì)為中間稍微突出,邊緣變矮的形狀,在中央的高點(diǎn)和兩端的低點(diǎn)以平滑曲線過(guò)渡,這樣的設(shè)計(jì)可以保證金手指和內(nèi)存插槽有足夠的接觸面

2023-09-19 14:49:44 1484

1484

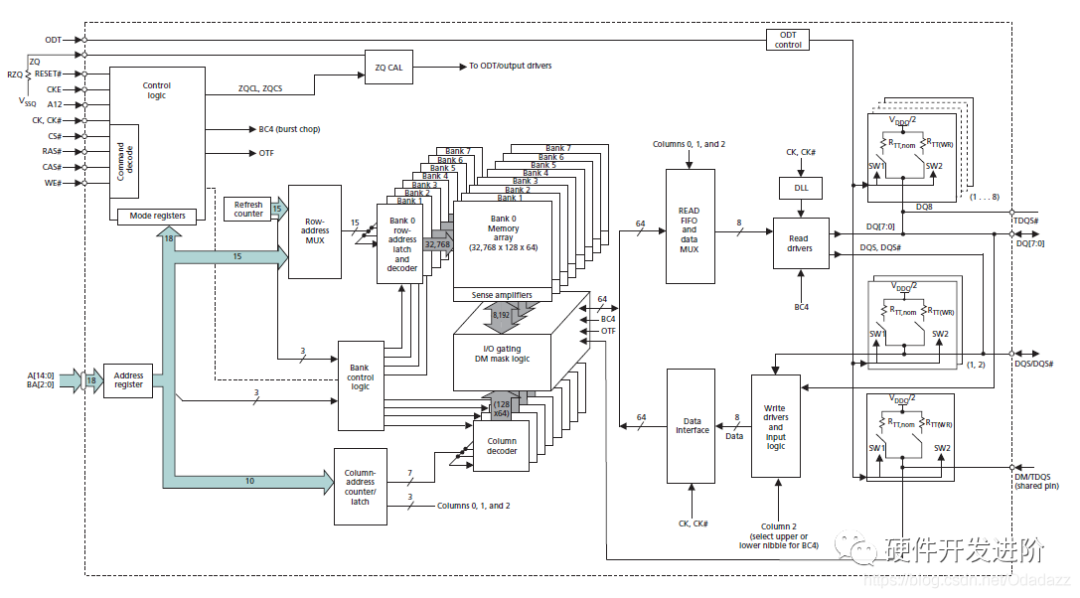

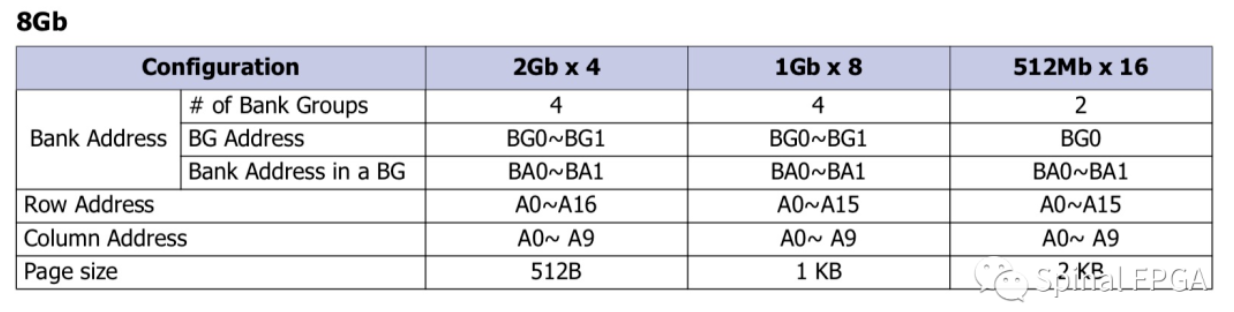

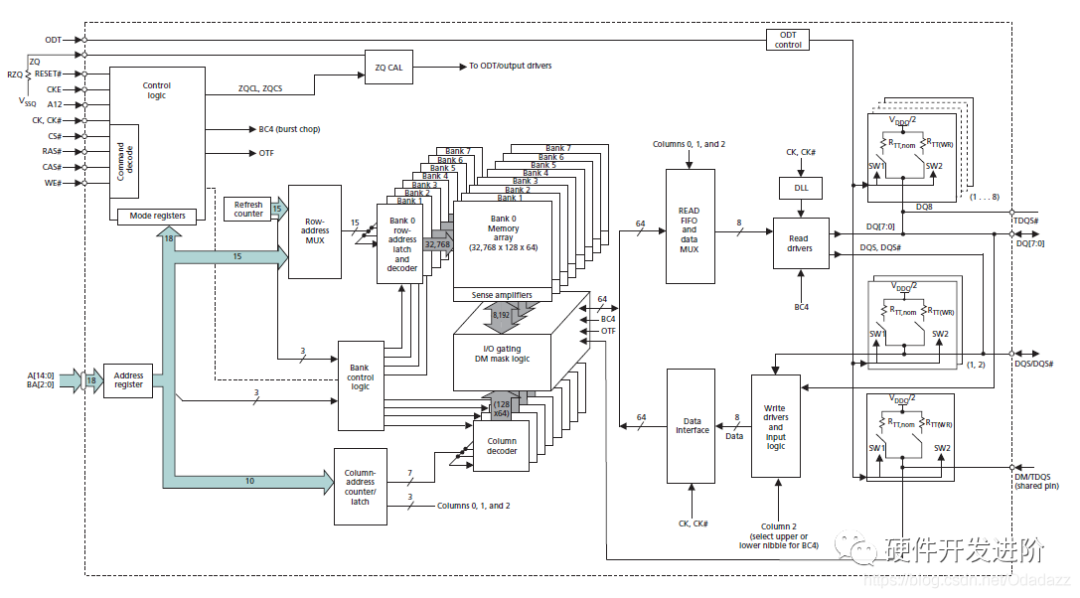

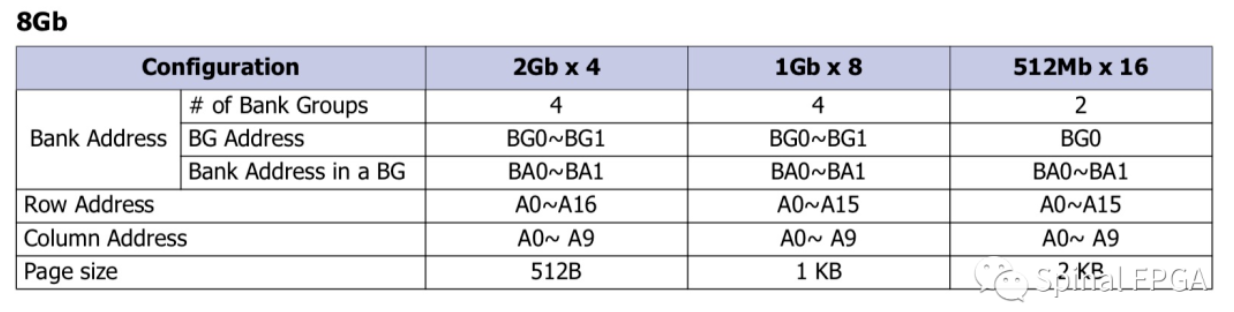

以MT41J128M型號(hào)為舉例:128Mbit=16Mbit*8banks 該DDR是個(gè)8bit的DDR3,每個(gè)bank的大小為16Mbit,一共有8個(gè)bank。

2023-09-15 15:30:09 629

629

一看到DDR,聯(lián)想到的就是高速,一涉及到高速板有些人就比較茫然。高速板主要考慮兩個(gè)問(wèn)題點(diǎn),當(dāng)然其它3W,2H是基本點(diǎn)。

2023-09-15 11:42:37 757

757

在全默認(rèn)設(shè)置的情況下,影馳HOF OC Lab幻跡S DDR5 8000內(nèi)存的工作速率為DDR5 4800,延遲設(shè)定為40-40-40-76,因此在這個(gè)設(shè)置下它的內(nèi)存性能并不突出,與普通的DDR5 4800內(nèi)存相當(dāng)。

2023-09-15 10:40:42 750

750

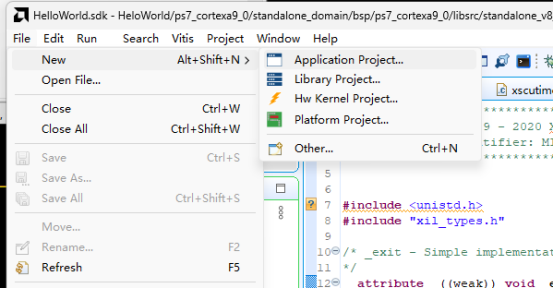

本文介紹一個(gè)FPGA開(kāi)源項(xiàng)目:DDR3讀寫(xiě)。該工程基于MIG控制器IP核對(duì)FPGA DDR3實(shí)現(xiàn)讀寫(xiě)操作。

2023-09-01 16:23:19 743

743

本文開(kāi)源一個(gè)FPGA項(xiàng)目:基于AXI總線的DDR3讀寫(xiě)。之前的一篇文章介紹了DDR3簡(jiǎn)單用戶接口的讀寫(xiě)方式:《DDR3讀寫(xiě)測(cè)試》,如果在某些項(xiàng)目中,我們需要把DDR掛載到AXI總線上,那就要通過(guò)MIG IP核提供的AXI接口來(lái)讀寫(xiě)DDR。

2023-09-01 16:20:37 1888

1888

上期和大家聊的電源PCB設(shè)計(jì)的重要性,那本篇內(nèi)容小編則給大家講講存儲(chǔ)器的PCB設(shè)計(jì)建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計(jì)要如何布局布線。 由于

2023-08-24 08:40:05 899

899

DDR4 3200和DDR4 3600是兩種常見(jiàn)的內(nèi)存頻率規(guī)格,它們?cè)谛阅苌蠒?huì)有一定的差別,但差別大小取決于具體的應(yīng)用場(chǎng)景和系統(tǒng)配置。

2023-08-22 14:45:05 28293

28293 上期和大家聊的電源PCB設(shè)計(jì)的重要性,那本篇內(nèi)容小編則給大家講講存儲(chǔ)器的PCB設(shè)計(jì)建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計(jì)要如何布局布線。 由于

2023-08-21 17:16:50 563

563

由于RK3588 DDR接口速率最高達(dá)4266Mbps,PCB設(shè)計(jì)難度大,所以強(qiáng)烈建議使用瑞芯微原廠提供的DDR模板和對(duì)應(yīng)的DDR固件,DDR模板是經(jīng)過(guò)嚴(yán)格的仿真和測(cè)試驗(yàn)證后發(fā)布的。 在單板

2023-08-18 10:55:43 556

556

上期和大家聊的電源PCB設(shè)計(jì)的重要性,那本篇內(nèi)容小編則給大家講講存儲(chǔ)器的PCB設(shè)計(jì)建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計(jì)要如何布局布線。由于

2023-08-18 08:09:43 384

384

上期和大家聊的電源PCB設(shè)計(jì)的重要性,那本篇內(nèi)容小編則給大家講講存儲(chǔ)器的PCB設(shè)計(jì)建議,同樣還是以大家最為熟悉的RK3588為例,詳細(xì)介紹一下DDR模塊電路的PCB設(shè)計(jì)要如何布局布線。 由于

2023-08-17 18:15:02 325

325

ddr200t開(kāi)發(fā)板是否有HDMI接口用于視頻輸出,或者有沒(méi)有其他有HDMI接口的開(kāi)發(fā)板能夠接到ddr200t上呢

2023-08-12 06:48:26

DDR5的主板不支持使用DDR4內(nèi)存。DDR5(第五代雙倍數(shù)據(jù)率)和DDR4(第四代雙倍數(shù)據(jù)率)是兩種不同規(guī)格的內(nèi)存技術(shù),它們?cè)陔姎馓匦院鸵_布局上存在明顯差異。因此,DDR5內(nèi)存模塊無(wú)法插入DDR4主板插槽中,也不兼容DDR4內(nèi)存控制器。

2023-08-09 15:36:25 12806

12806 DDR是運(yùn)行內(nèi)存芯片,其運(yùn)行頻率主要有100MHz、133MHz、166MHz三種,由于DDR內(nèi)存具有雙倍速率傳輸數(shù)據(jù)的特性,因此在DDR內(nèi)存的標(biāo)識(shí)上采用了工作頻率×2的方法。 ? DDR芯片

2023-07-28 13:12:06 1884

1884

電子發(fā)燒友網(wǎng)站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中應(yīng)用.pdf》資料免費(fèi)下載

2023-07-24 09:50:47 0

0 《基于“礦板”低成本學(xué)習(xí)Zynq系列》之六-DDR測(cè)試

2023-07-19 19:19:44 1742

1742

DDR是Double Data Rate的縮寫(xiě),即“雙倍速率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器”。DDR是一種技術(shù),中國(guó)大陸工程師習(xí)慣用DDR稱呼用了DDR技術(shù)的SDRAM,而在中國(guó)臺(tái)灣以及歐美,工程師習(xí)慣用DRAM來(lái)稱呼。

2023-07-16 15:27:10 3370

3370

DDR3的速度較高,如果控制芯片封裝較大,則不同pin腳對(duì)應(yīng)的時(shí)延差異較大,必須進(jìn)行pin delay時(shí)序補(bǔ)償。

2023-07-04 09:25:38 312

312

對(duì)于DDR的理解,最初簡(jiǎn)單的以為無(wú)非一個(gè)大的數(shù)組,我會(huì)接口使用就OK了。

2023-06-28 15:36:06 406

406

DDR是DDR SDRAM的簡(jiǎn)稱,只是人們習(xí)慣了稱之為DDR,全稱為Double Data Rate Synchronous Dynamic Random Access Memory,中文名為:雙倍速率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,同步是指需要時(shí)鐘。

2023-06-25 15:06:40 4907

4907

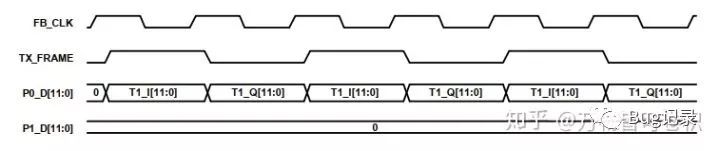

注意,這里的DDR指的是Double Data Rate,雙倍數(shù)據(jù)速率。這篇文章并不是講DDR存儲(chǔ)器系列的東西。

2023-06-16 10:22:06 781

781

DDR 驗(yàn)證是任何 SoC 中最關(guān)鍵和最復(fù)雜的任務(wù)之一,因?yàn)樗婕拔挥?DUT 內(nèi)部的控制器和位于板載 DUT 外部的外部 DDR 存儲(chǔ)器。在這里,我們將討論 DDR VIP 模型的快速初始化。

2023-05-29 09:10:46 772

772

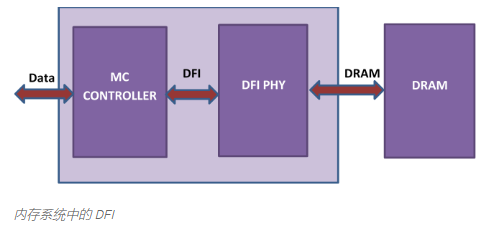

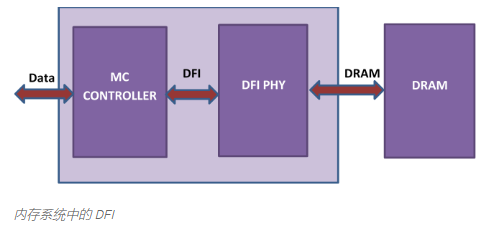

DDR PHY 接口 (DFI) 用于包括智能手機(jī)在內(nèi)的多種消費(fèi)電子設(shè)備。DFI 是一種接口協(xié)議,用于定義在 DRAM 設(shè)備之間以及 MC(微控制器)和 PHY 之間傳輸控制信息和數(shù)據(jù)所需的信號(hào)

2023-05-26 15:27:31 4574

4574

DDR4內(nèi)存模塊支持單個(gè)64位通道(如果考慮ECC,則為72位通道)。相比之下,DDR5內(nèi)存模塊配備了兩個(gè)獨(dú)立的32位通道(40位ECC)。

2023-05-08 10:27:44 1331

1331 內(nèi)存是數(shù)據(jù)中心、服務(wù)器以及個(gè)人計(jì)算機(jī)等技術(shù)發(fā)展的重要組成。目前內(nèi)存的發(fā)展是由DDR技術(shù)路線引導(dǎo),TE Connectivity(以下簡(jiǎn)稱“TE”)經(jīng)歷了DDR1、DDR2、DDR3、DDR4的迭代

2023-05-06 17:33:42 1392

1392

我們有一個(gè)帶有連接到 LS1046A 的 DDR4 內(nèi)存 (DDR4T04G72) 的定制板,目前正在為 DDR 控制器進(jìn)行配置。目前我們對(duì)為什么我們甚至沒(méi)有啟動(dòng)和運(yùn)行 DDR 時(shí)鐘 (MCK0

2023-05-06 08:20:49

對(duì)于i.MX 8M Mini處理器,使用mscale ddr工具生成DDR校準(zhǔn)值的目的是什么?

我有一個(gè)運(yùn)行 u-boot 的 i.MX 8M Mini 處理器。查看 u-boot 源代碼,我相信

2023-05-05 09:09:34

DDR5 已占據(jù)整個(gè) DRAM 市場(chǎng)份額的 10%,2024年則將進(jìn)一步擴(kuò)大至 43%。服務(wù)器市場(chǎng)可能最先推廣DDR5,服務(wù)器市場(chǎng)對(duì)高性能有著絕對(duì)的需求。

2023-04-18 11:36:47 1604

1604 IC DDR SWITCH/MUX 48NFBGA

2023-04-06 19:18:57

ICMUX/DEMUX2:1DDR48TFBGA

2023-04-06 15:33:34

ICMUX/DEMUX2:1DDR48TFBGA

2023-04-06 15:33:19

DDR內(nèi)存1代已經(jīng)淡出市場(chǎng),直接學(xué)習(xí)DDR3 SDRAM感覺(jué)有點(diǎn)跳躍;如下是DDR1、DDR2以及DDR3之間的對(duì)比。

2023-04-04 17:08:47 2871

2871

\lx2160ardb\ddr_init.c中,我們應(yīng)該定義 CONFIG_STATIC_DDR 還是CONFIG_DDR_NODIMM?他們有什么區(qū)別。

2023-04-03 07:24:21

IP CORE DDR2 SDRAM XO2

2023-03-30 12:02:09

SITE LICENSE IP CORE DDR3 ECP3

2023-03-30 12:02:09

SITE LICENSE DDR2 SDRAM ECP3

2023-03-30 12:01:46

SITE LICENSE DDR2 SDRAM ECP2

2023-03-30 12:01:46

SITE LICENSE DDR2 SDRAM ECP2M

2023-03-30 12:01:46

SITE LICENSE DDR3 SDRAM ECP3

2023-03-30 12:01:46

IP CORE DDR2 SDRAM XO2

2023-03-30 12:01:19

IP CORE DDR3 PHY ECP3 USER CONF

2023-03-30 12:01:19

IP CORE DDR2 SDRAM CTLR ECP2M

2023-03-30 12:01:17

IP CORE DDR2 SDRAM CTLR ECP3

2023-03-30 12:01:16

IP CORE DDR2 SDRAM CTLR ECP2

2023-03-30 12:01:16

IP CORE DDR2 SDRAM CTLR SC/SCM

2023-03-30 12:01:16

IP CORE DDR3 SDRAM CTLR ECP3

2023-03-30 12:01:16

EVALMODULEFORTS3DDR32611

2023-03-30 11:56:12

DDR-240C-48

2023-03-29 22:43:23

NCP4305DDR2G

2023-03-29 18:04:27

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論