上期和大家聊的電源PCB設計的重要性,那本篇內容小編則給大家講講存儲器的PCB設計建議,同樣還是以大家最為熟悉的RK3588為例,詳細介紹一下DDR模塊電路的PCB設計要如何布局布線。

由于RK3588 DDR接口速率最高達4266Mbps,PCB設計難度大,所以強烈建議使用瑞芯微原廠提供的DDR模板和對應的DDR固件,DDR模板是經過嚴格的仿真和測試驗證后發布的。

在單板PCB設計空間足夠的情況下,優先考慮留出DDR電路模塊所需要的布局布線空間,拷貝瑞芯微原廠提供的DDR模板,包含芯片與DDR顆粒相對位置、電源濾波電容位置、鋪銅間距等完全保持一致。

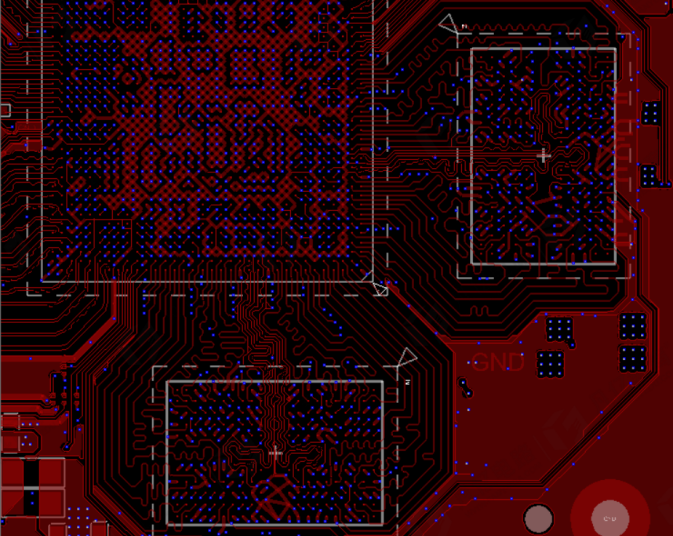

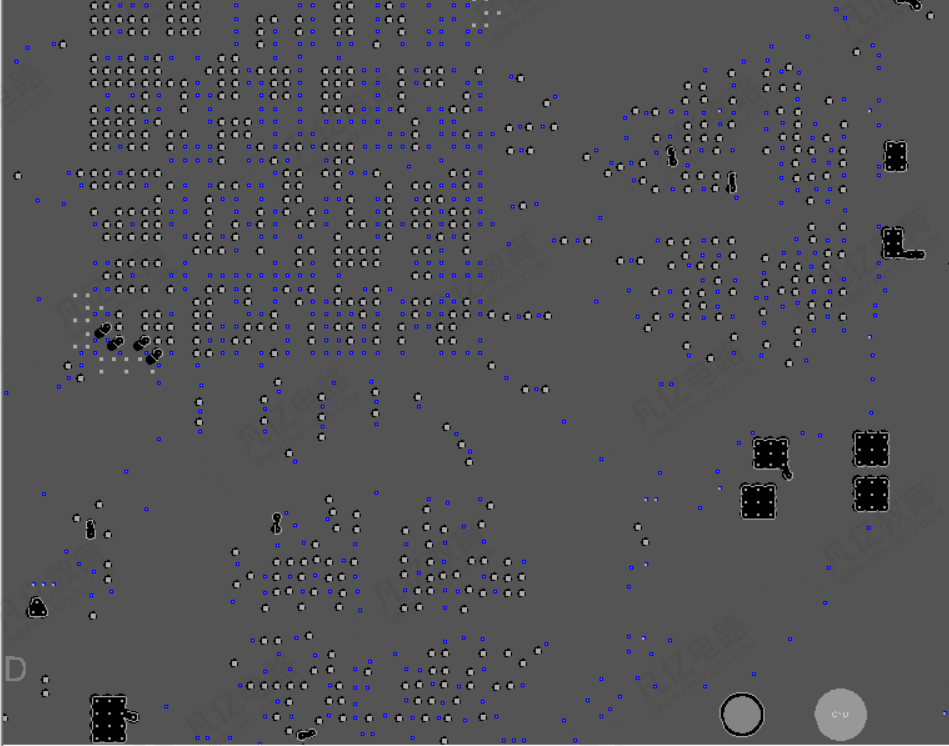

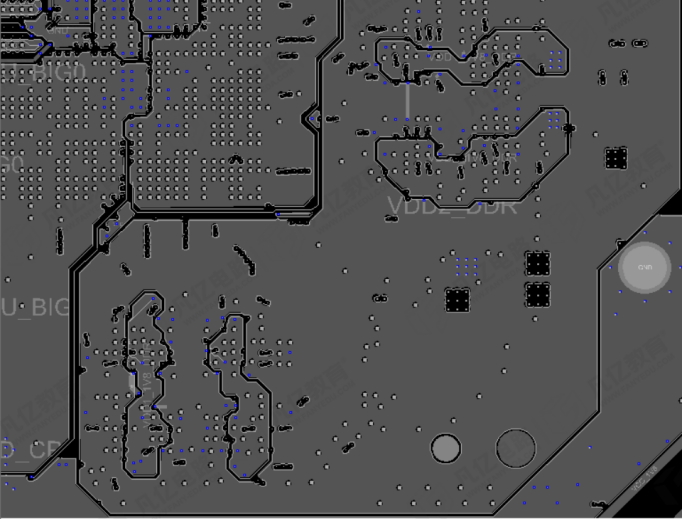

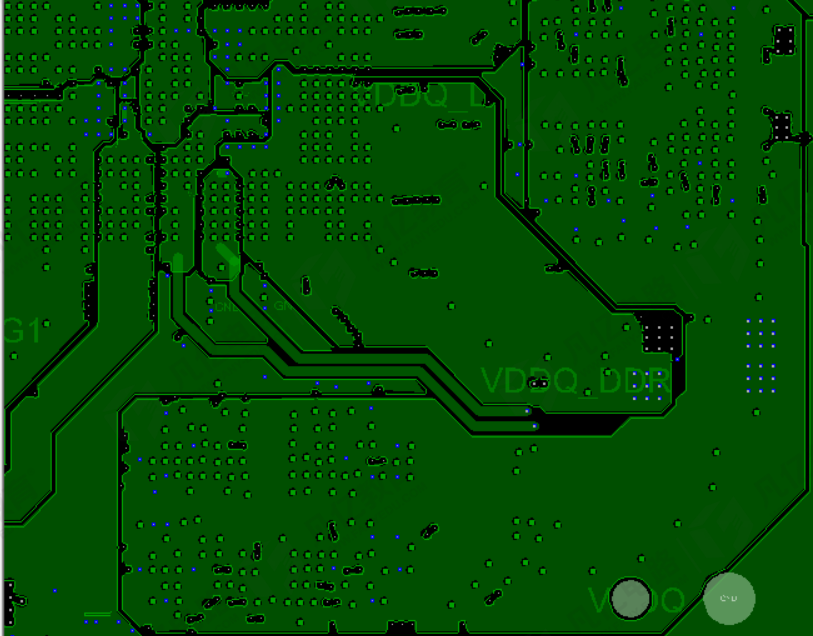

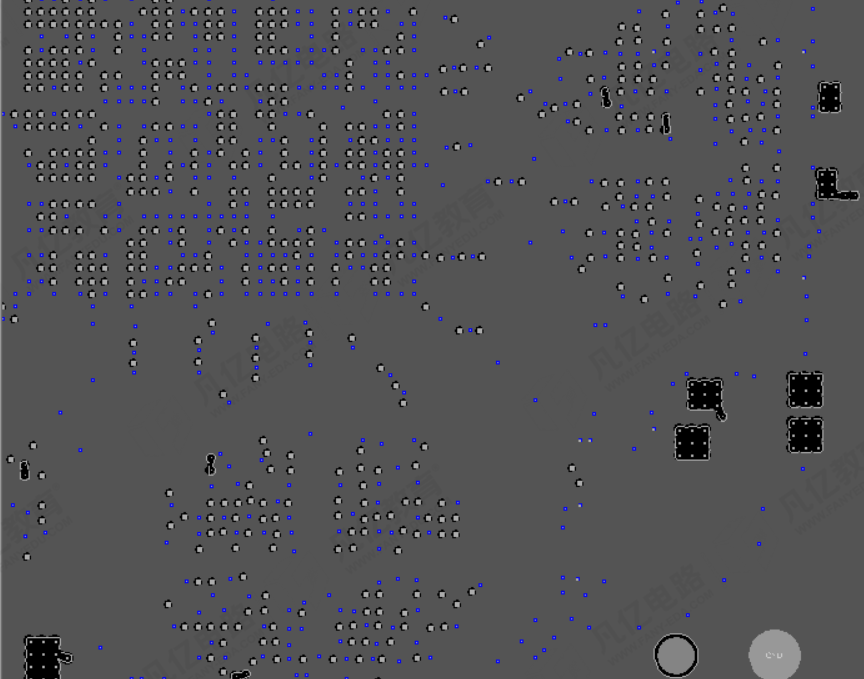

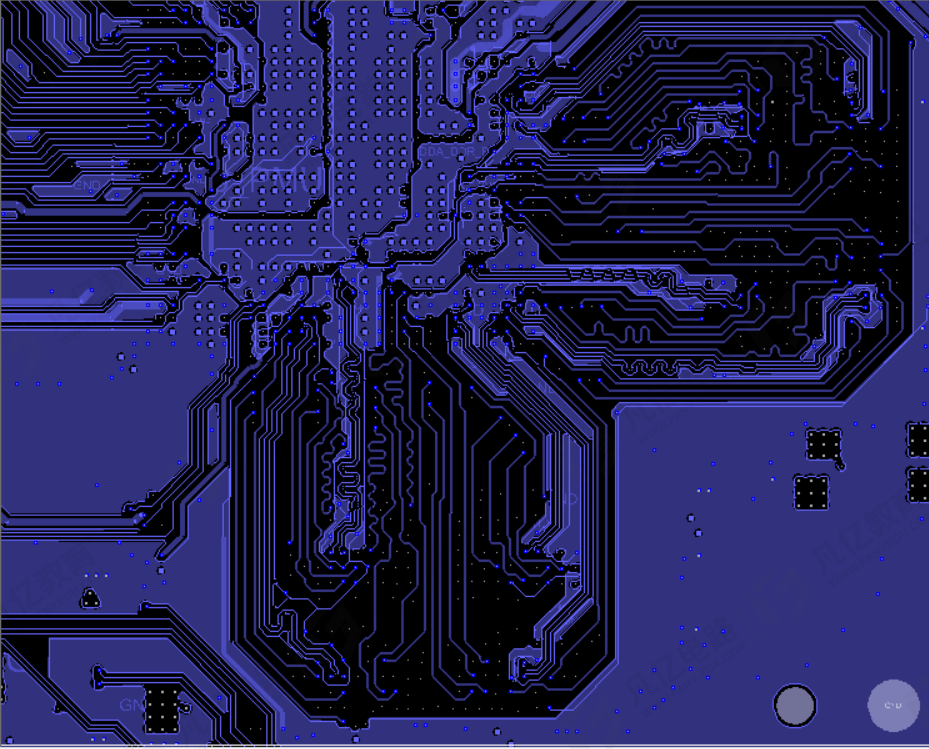

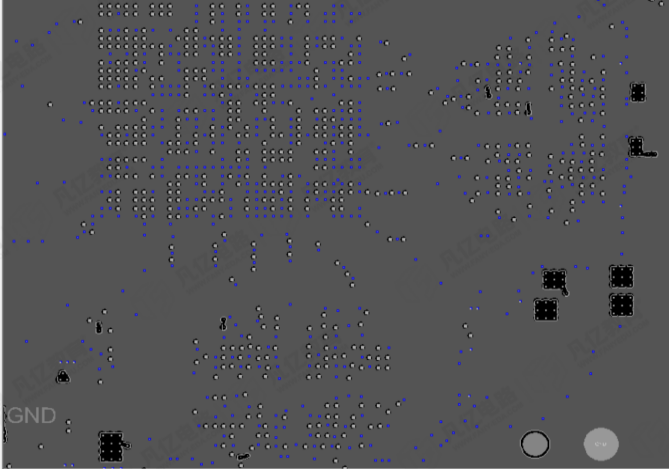

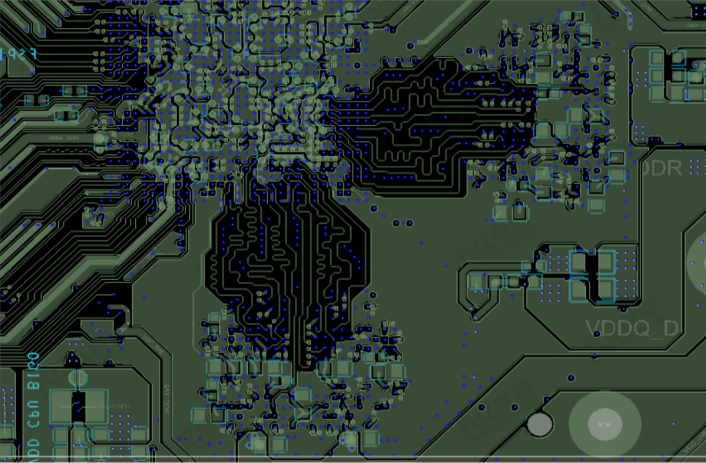

如下8張圖(從左至右),分別為:L1-L8層DDR電路走線示意圖。

More

如果自己設計PCB,請參考以下PCB設計建議,強烈建議進行仿真優化,然后與瑞芯微原廠FAE進行確認,確認沒問題以后再進行打樣調試。

Part.

1

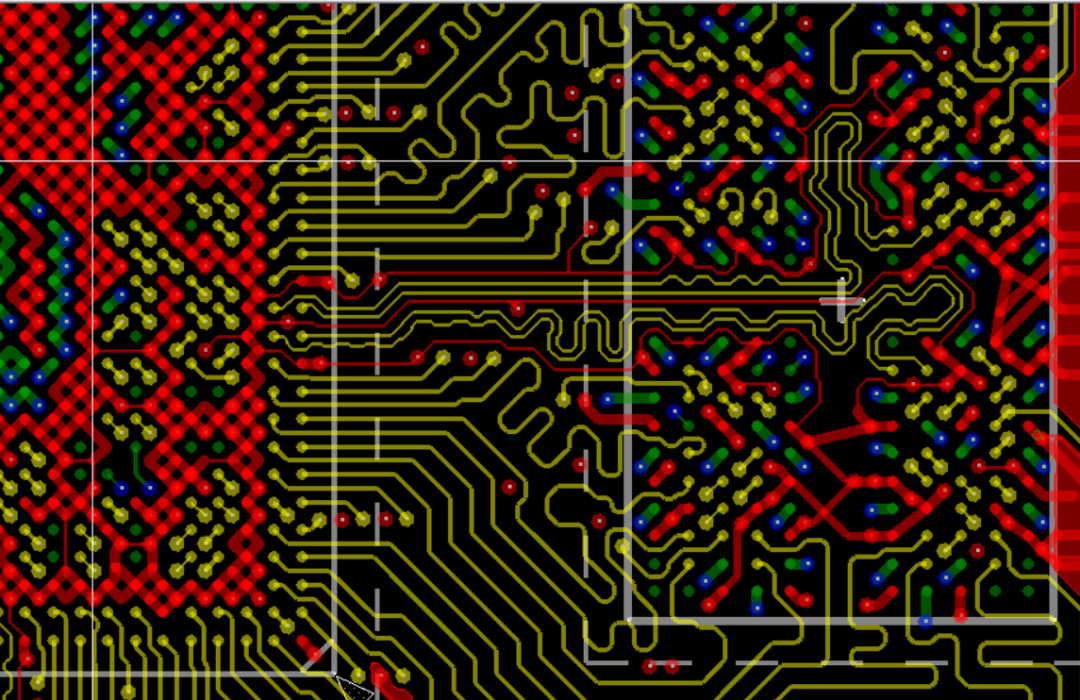

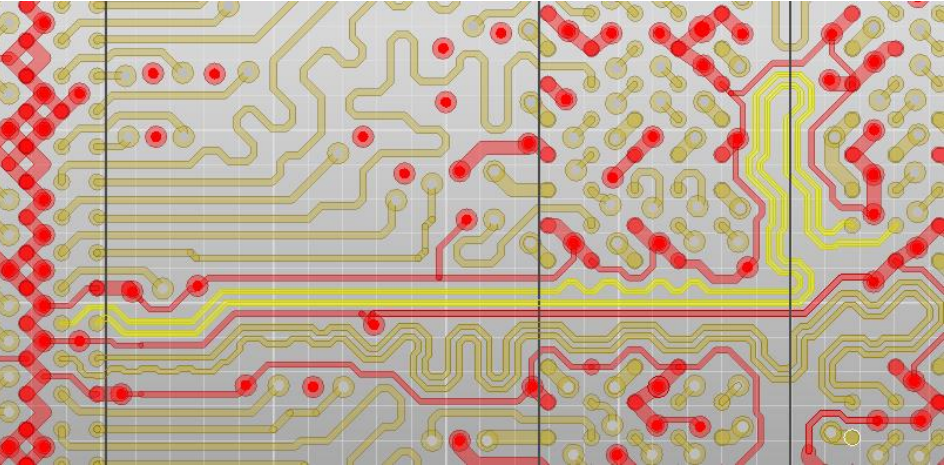

CPU管腳,對應的GND過孔數量,建議嚴格參考模板設計,不能刪減GND過孔。8層通孔的PCB模板,CPU管腳GND過孔設計如下圖所示,黃色為DDR管腳信號,地管腳為紅色。

Part.

2

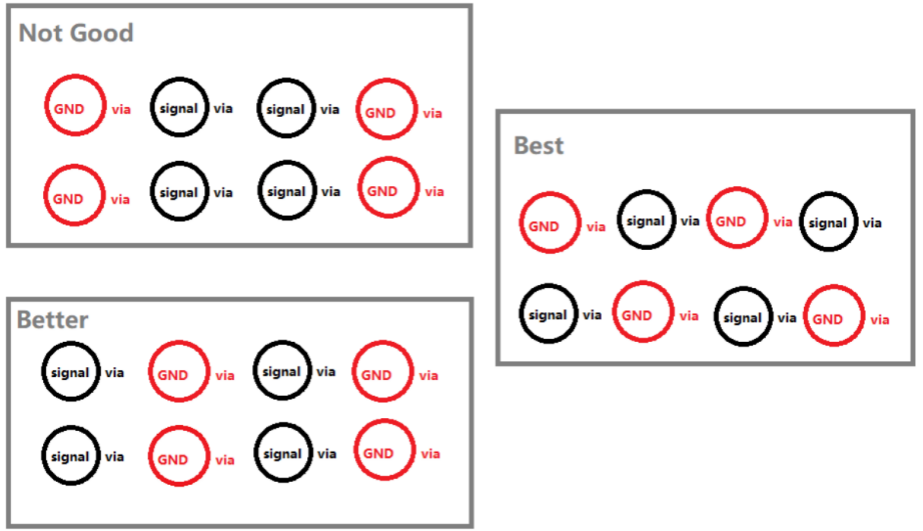

信號換層前后,參考層都為GND平面時,在信號過孔25mil(過孔和過孔的中心間距)范圍內需要添加GND回流過孔(黃色為DDR信號,紅色為GND信號),改善信號回流路徑,GND過孔需要把信號換層前后GND參考平面連接起來。

一個信號過孔,至少要有一個GND回流過孔,盡可能增加GND回流過孔數量,可以進一步改善信號質量,如下圖所示。

Part.

3

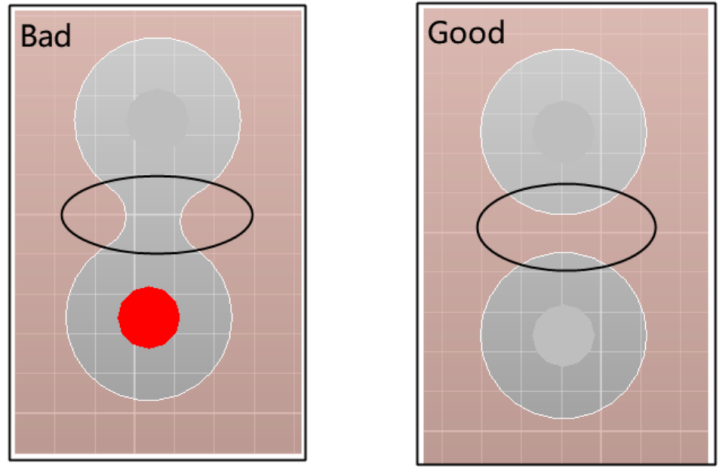

GND過孔和信號過孔的位置會影響信號質量,建議GND過孔和信號過孔交叉放置,如下圖所示,雖然同樣是4個GND回流過孔,4個信號過孔在一起的情況要避免,這種情況下過孔的串擾最大。

Part.

4

8層板建議DDR信號走第一層、第六層、第八層,DQ、DQS、地址和控制信號、CLK信號都參考完整的GND平面,如果GND平面不完整,將會對信號質量造成很大的影響。

Part.

5

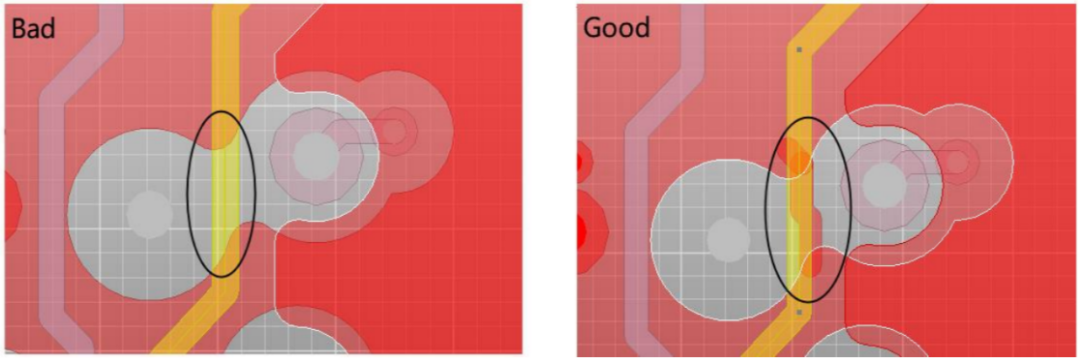

如下圖所示,當過孔導致信號參考層破裂時,可以考慮用GND走線優化下參考層,改善信號質量。

Part.

6

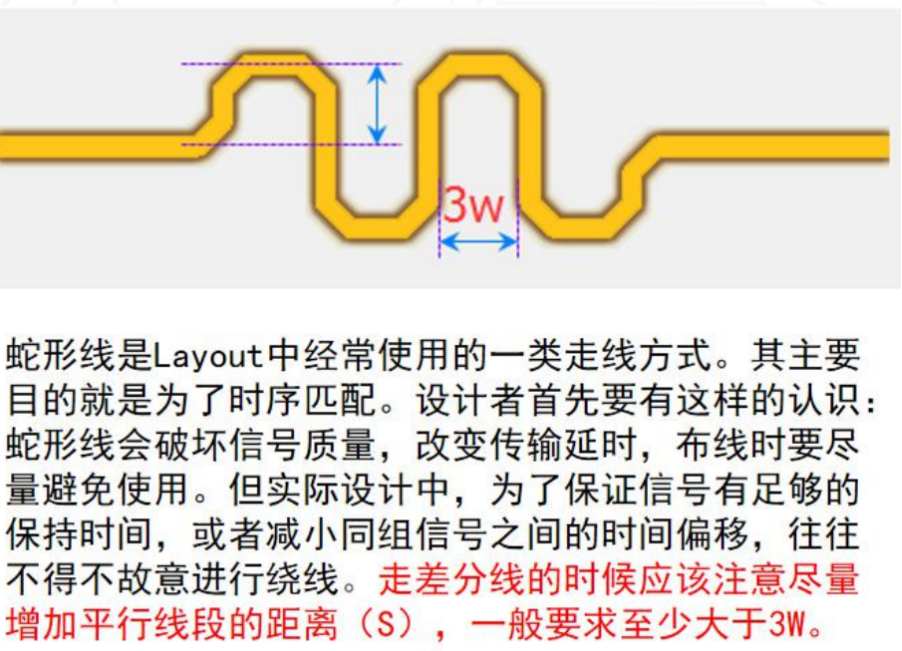

繞線自身的串擾會影響信號延時,走線繞等長時,注意按下圖所示。

Part.

7

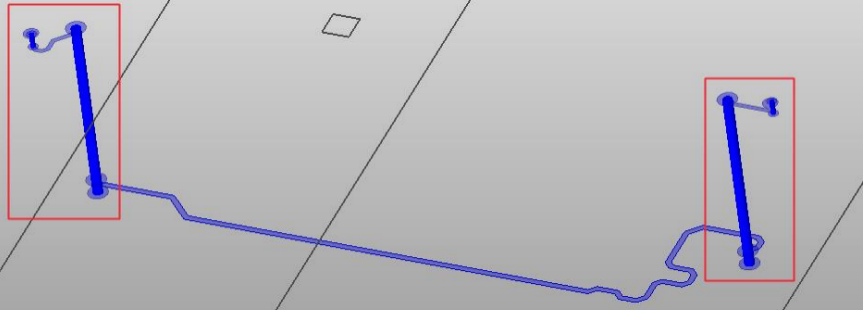

在做等長時,需要考慮過孔的延時,如下圖所示。

Part.

8

非功能焊盤會破壞銅皮,以及增大過孔的寄生電容,需要刪除過孔的非功能焊盤,做無盤設計。

Part.

9

走線距離過孔越近,參考平面越差,走線距離過孔鉆孔距離建議≧8mil,有空間的地方增大間距。

Part.

10

調整過孔位置,優化平面的裂縫,不要造成平面割裂,起到改善回流路徑的作用,如下圖所示。

Part.

11

DQS、CLK、WCLK信號需要做包地處理,包地線或銅皮建議間隔≦400mil,打一個GND過孔,如下圖所示。

Part.

12

對于VDD_DDR電源,DCDC區域電源換層時,建議打≧6個0503過孔。

Part.

13

對于VDDQ_DDR電源,DCDC區域電源換層時,建議打≧6個0503過孔。

Part.

14

對于VDD2_DDR電源,DCDC區域電源換層時,建議打≧6個0503過孔。

Part.

15

對于VDD1_1V8_DDR電源,電源平面換層時,建議至少打≧2個0402過孔。

Part.

16

每個電容焊盤建議至少一個過孔,對于0603或者0805封裝的電容建議一個焊盤對應兩個過孔,過孔的位置要靠近管腳放置,減小回路電感。

設計完PCB后,一定要做分析檢查,才能讓生產更順利,這里推薦一款可以一鍵智能檢測PCB布線布局最優方案的工具:華秋DFM軟件,只需上傳PCB/Gerber文件后,點擊一鍵DFM分析,即可根據生產的工藝參數對設計的PCB板進行可制造性分析。

華秋DFM軟件是國內首款免費PCB可制造性和裝配分析軟件,擁有300萬+元件庫,可輕松高效完成裝配分析。其PCB裸板的分析功能,開發了19大項,52細項檢查規則,PCBA組裝的分析功能,開發了10大項,234細項檢查規則。

基本可涵蓋所有可能發生的制造性問題,能幫助設計工程師在生產前檢查出可制造性問題,且能夠滿足工程師需要的多種場景,將產品研制的迭代次數降到最低,減少成本。

華秋DFM軟件下載地址(復制到電腦瀏覽器打開):

https://dfm.elecfans.com/uploads/software/promoter/HQDFM%20V3.7.0_DFMGZH.zip

專屬福利

上方鏈接下載還可享多層板首單立減50元

每月1次4層板免費打樣

并領取多張無門檻“元器件+打板+貼片”優惠券

華秋電子是一家致力于以信息化技術改善傳統電子產業鏈服務模式的產業數智化服務平臺,目前已全面打通產業上、中、下游,形成了電子產業鏈閉環生態,致力于為行業帶來“高品質,短交期,高性價比”的一站式服務平臺,可向廣大客戶提供媒體社區平臺服務、元器件采購服務、PCB制造服務及可靠性制造分析服務、SMT貼片/PCBA加工服務,如有相關業務需求,請掃碼填寫以下表單,我們將為您對接專屬服務。

點擊上方圖片關注我們

原文標題:【華秋干貨鋪】DDR電路的PCB布局布線要求

文章出處:【微信公眾號:華秋電子】歡迎添加關注!文章轉載請注明出處。

-

華秋電子

+關注

關注

19文章

485瀏覽量

13920

原文標題:【華秋干貨鋪】DDR電路的PCB布局布線要求

文章出處:【微信號:huaqiu-cn,微信公眾號:華秋電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高速PCB板的電源布線設計

解決噪聲問題試試從PCB布局布線入手

PCB設計整板鋪銅說明

在TMS320DM643x DMSoC上實現DDR2 PCB布局

在TMS320DM644x DMSoC上實現DDR2 PCB布局

高頻電路布線有什么要求嗎

求助,關于雙面板運放PCB鋪銅遇到的疑問求解

高速ADC PCB布局布線技巧分享

【華秋干貨鋪】DDR電路的PCB布局布線要求

【華秋干貨鋪】DDR電路的PCB布局布線要求

評論