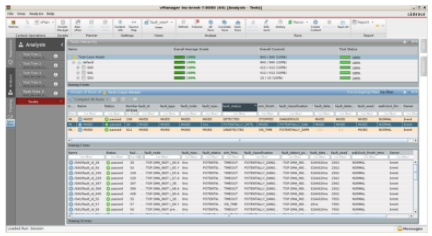

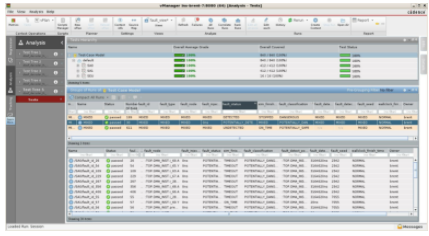

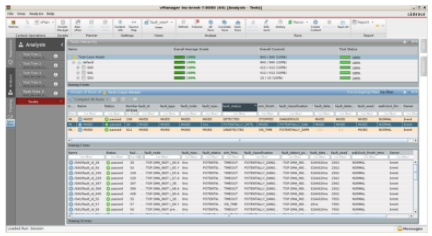

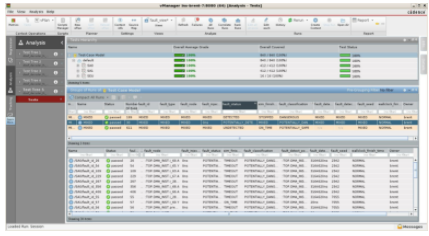

Cadence設計系統(tǒng)公司公布一個新版的尖端功能驗證平臺與方法學,擁有全套最新增強功能,與之前發(fā)布的版本相比,可將SoC驗證效率提高一倍。 Incisive ?12.2提供了兩倍性能,全新Incisive調(diào)試分析器產(chǎn)品,全新低功耗建模,以及當今復雜IP與SoC高效驗證所需的數(shù)百種其他功能。

2013-01-27 10:44:38 1437

1437

確保汽車 SoC 在功能上安全還可以讓駕駛員和乘客對他們的車輛充滿信心。將安全驗證集成到功能驗證流程中可以是加快流程和管理符合 ISO 26262 等標準的工作的有效方法。

2022-06-15 16:09:40 3256

3256

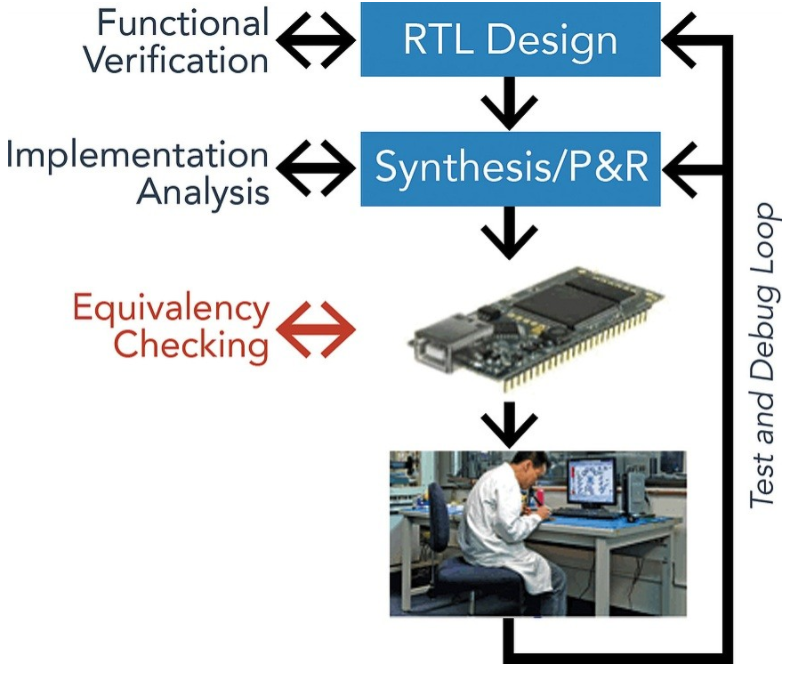

什么是FPGA原型?? FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能

2022-07-19 16:27:29 1735

1735 我們都知道,在調(diào)試FPGA代碼時,大多會使用Signaltap 或者 modelsim作為調(diào)試工具,(或者XILINX用chipScope)但是這些調(diào)試要不是只能滿足單純的邏輯驗證,要不只能抓取很短的一段時間,都無法滿足,在大數(shù)據(jù)量的情況下,怎么查看是否出現(xiàn)錯誤不知道大家有什么好的解決方法沒

2018-01-04 17:17:57

FPGA原型驗證已是當前原型驗證的主流且成熟的芯片驗證方法——它通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證ASIC的功能,并在芯片的基本功能驗證通過后就可以開始驅(qū)動的開發(fā),一直到芯片

2020-08-21 05:00:12

FPGA基本原理及設計思想和驗證方法看完你就懂了

2021-09-18 07:08:52

設計驗證周期過程中使用的工具及技術,并逐一審視各項優(yōu)缺點。 有效驗證降低設計風險FPGA設計驗證的規(guī)畫和預算安排的失敗,可能瓦解整個產(chǎn)品開發(fā)計畫;時程的延誤會和光罩技術的再修正(respin)一樣嚴重

2010-05-21 20:32:24

時序仿真的重要性是什么傳統(tǒng)的FPGA驗證方法是什么FPGA設計的驗證技術及應用原則是什么

2021-05-08 09:05:32

仿真驗證概述本文節(jié)選自特權同學的圖書《FPGA設計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 仿真測試是FPGA設計流程中必不可少的步驟

2019-04-10 06:35:34

先進的設計與仿真驗證方法成為SoC設計成功的關鍵。一個簡單可行的SoC驗證平臺,可以加快SoC系統(tǒng)的開發(fā)與驗證過程。FPGA器件的主要開發(fā)供應商都針對自己的產(chǎn)品推出了SoC系統(tǒng)的開發(fā)驗證平臺,如

2019-10-11 07:07:07

SoC驗證超越了常規(guī)邏輯仿真,但用于加速SoC驗證的廣泛應用的三種備選方法不但面臨可靠性問題,而且難以進行權衡。而且,最重要的問題還在于硬件加速訪問權限、時機及其穩(wěn)定性。

2019-11-11 06:37:11

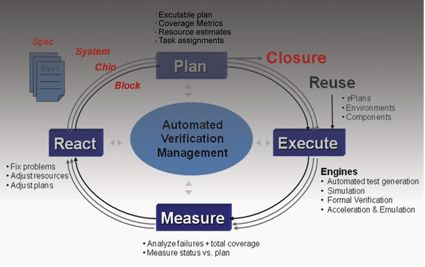

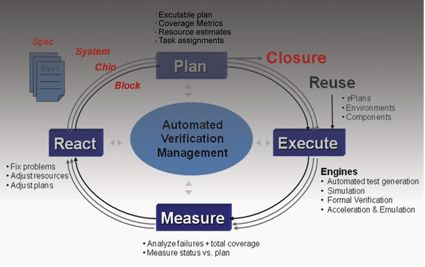

由于片上系統(tǒng)(SoC)設計變得越來越復雜,驗證面臨著巨大的挑戰(zhàn)。大型團隊不斷利用更多資源來尋求最高效的方法,從而將新的方法學與驗證整合在一起,并最終將設計與驗證整合在一起。雖然我們知道實現(xiàn)驗證計劃

2019-07-11 07:35:58

)是一種免費的開源方法和庫,用于非常有效地對 FPGA 和 ASIC 進行 VHDL驗證 - 還可以顯著提高質(zhì)量。 UVVM(通用 VHDL 驗證方法)是增長最快的 FPGA 驗證方法——獨立于語言

2022-02-13 17:03:49

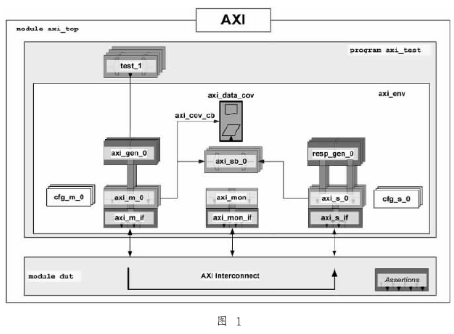

驗證用于找出DUT中的bug,這個過程通常是把DUT放入一個驗證平臺中來實現(xiàn)的。一個驗證平臺要實現(xiàn)如下基本功能:驗證平臺要模擬DUT的各種真實使用情況,這意味著要給DUT施加各種激勵,有正常的激勵

2020-12-02 15:21:34

Graphics公司Veloce驗證平臺在超大規(guī)模IC系統(tǒng)中仿真驗證的應用。借助Veloce的高速和大容量的特性,極大的提高功能驗證的效率,解決由于芯片規(guī)模大FPGA無法驗證的問題,保證芯片的按時投片

2010-05-28 13:41:35

項目名稱:基于FPGA的數(shù)字電路實驗驗證平臺應用領域:高校的數(shù)字電路實驗課程中實驗結(jié)果驗證與分析參賽計劃:一、設計思路:在高校的數(shù)字電路課程中,要通過在FPGA器件上通過設計一些簡單的時序或者組合

2021-05-12 18:13:29

隨著系統(tǒng)芯片(SoC)設計的體積與復雜度持續(xù)升高,驗證作業(yè)變成了瓶頸:占了整個SoC研發(fā)過程中70%的時間。因此,任何能夠降低驗證成本并能更早實現(xiàn)驗證sign-off的方法都是眾人的注目焦點。

2019-08-26 07:06:04

制化FPGA原型板驗證效率的創(chuàng)新方法,自動化現(xiàn)有的電路仿真(in-circuit emulation)偵錯功能,并提供更高的FPGA能見度。這個以FPGA為基礎的SoC驗證平臺對工研院而言是前景看好

2011-07-24 09:47:50

設計的驗證平臺,以此來提高工作效率。論文介紹了FF-DX地址計算部件的時序建模和靜態(tài)時序分析方法。在靜態(tài)時序分析之后,將SDF文件中的延時信息反標到邏輯網(wǎng)表中,通過動態(tài)時序驗證進一步保證設計的時序收斂

2011-12-07 17:40:14

SoC原型的Handel-C描述及其實現(xiàn)流程是怎樣的?利用RC1000和SoC設計展示評估平臺RC200搭建一個原型驗證系統(tǒng)的樣機?

2021-05-28 06:15:18

產(chǎn)生的。 有了此層級的抽出,針對混合信號FPGA所提供的基本驗證方法和沿著標準處理的數(shù)字FPGA基本上是相同的。 典型的PSC設計者會在設計過程中執(zhí)行以下步驟:在Libero中產(chǎn)生并整合系統(tǒng)功能區(qū)塊

2011-10-16 22:55:10

FPGA在視頻處理方面可能很有用處,但在驗證基于FPGA的視頻系統(tǒng)時,則需要仔細關注您所用的方法。

2019-07-23 06:36:45

但是,如果FPGA通過接口與DSP核心連接,并且高速視頻數(shù)據(jù)是通過它來傳輸,那么它根本不是簡單的系統(tǒng)。這種更高的設計復雜度導致了額外的驗證難題,并且如果您在設計階段晚期發(fā)現(xiàn)一處重大錯誤,那么這還會導致高成本的系統(tǒng)板重制。為了消除這一隱患,您必須仔細考慮自己采用的驗證方法,以便降低重制風險。

2019-09-19 06:00:59

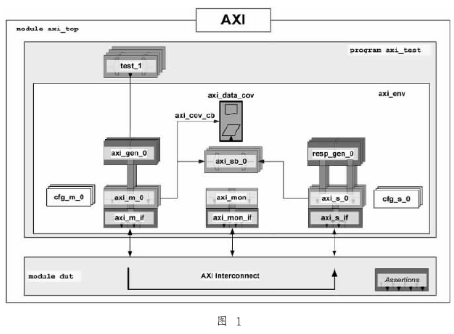

Systemverilog [1]和 UVM [2]為驗證團隊提供結(jié)構和規(guī)則。它使得在許多測試中能獲得一致的結(jié)果,并可以在團隊之間共享驗證。許多驗證團隊都在使用由C代碼編寫的驗證套件。本文將討論將基于C的測試和驗證套件集成到常規(guī)UVM測試平臺的各種方法。

2020-12-15 07:38:34

1 簡介隨著設計的復雜程度不斷增加,要求把更多的資源放到驗證上,不但要求驗證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應異常的處理狀態(tài),這在傳統(tǒng)測試方法下往往是難以實現(xiàn)的。此外

2019-07-03 07:40:26

從RTL驗證到軟件開發(fā)和操作系統(tǒng)移植的一系列過程。這意味著創(chuàng)造一個可輕松衡量性能和優(yōu)化平臺的環(huán)境。但事有先后。雖然有朝一日此類驗證環(huán)境會幫助說服ST Microelectronics客戶訂購大量

2017-04-05 14:17:46

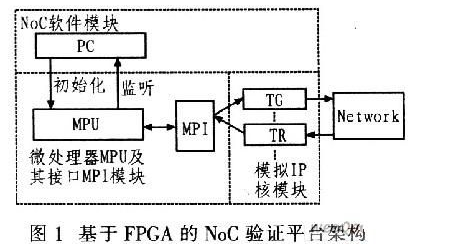

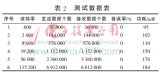

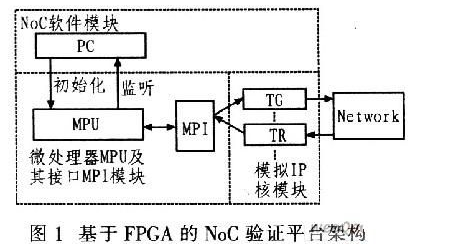

本文提出了一種基于FPGA的NoC驗證平臺。詳細討論了該驗證平臺中FPGA硬件平臺和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點。通過一個實例仿真驗證的結(jié)果說明了該驗證平臺的基本功能和優(yōu)越性。

2021-05-06 07:20:48

SoC系統(tǒng)驗證平臺總體框架是怎樣的?SoC系統(tǒng)驗證平臺如何去構建?

2021-04-28 07:13:41

SoC與IP有什么關系?如何去驗證IP?

2021-04-28 06:02:37

請教一下基于FPGA的通信系統(tǒng)基帶驗證平臺該怎樣去設計?

2021-04-28 06:59:45

請問一下,如何利用AMSVF來進行混合信號SoC的全芯片驗證?

2021-05-06 07:56:08

固網(wǎng)短信電話專用SoC芯片介紹一種數(shù)模混合SoC設計協(xié)同仿真的驗證方法

2021-04-23 06:06:39

、包和庫,特別是半導體知識產(chǎn)權 (IP) 核心設計過程,包括以下章節(jié):驗證方法——概述驗證方法——簡介驗證 IP - 方法論的作用如何選擇驗證方法基于標準的 IP 和 SoC 的驗證方法功能驗證方法

2022-11-26 20:43:20

要使用哪種方法去驗證 FPGA 的邏輯設計?FPGA的優(yōu)缺點是什么?

2021-04-08 06:57:32

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經(jīng)成為ASIC芯片設計中重要的驗證方法[2].本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結(jié)果。

2019-06-18 07:43:00

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經(jīng)成為ASIC芯片設計中重要的驗證方法。本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結(jié)果。1、RFID芯片的FPGA

2019-05-29 08:03:31

數(shù)模混合信號仿真已經(jīng)成為SoC芯片驗證的重要環(huán)節(jié)。文章以一款固網(wǎng)短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協(xié)同仿真環(huán)境進行仿真的驗證方法,并給出驗證結(jié)

2009-05-15 15:41:26 19

19 數(shù)模混合信號仿真已經(jīng)成為SoC芯片驗證的重要環(huán)節(jié)。文章以一款固網(wǎng)短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協(xié)同仿真環(huán)境進行仿真的驗證方法,并給出驗證結(jié)

2009-05-15 15:41:26 5

5 近幾年來,SoC 技術已經(jīng)得到了迅速的發(fā)展,隨之而來的是 SoC 設計的驗證也變得更加復雜,花費的時間和人力成倍增加。一個SoC 芯片的驗證可能會用到多種驗證技術,常用的 SoC 的

2009-08-31 10:33:25 24

24 本文首先介紹RVM驗證方法學和覆蓋率驅(qū)動技術,然后詳細分析如何使用結(jié)合覆蓋率驅(qū)動技術的RVM驗證方法學對SOC(System On Chip)進行完備的功能驗證, 最

2009-09-05 08:53:00 15

15 隨著大容量高速度的FPGA的出現(xiàn),在流片前建立一個高性價比的原型驗證系統(tǒng)已經(jīng)成為縮短系統(tǒng)級芯片(SoC)驗證時間,提高首次流片成功率的重要方法。本文著重討論了用FPGA建

2009-09-11 15:50:09 16

16 ESL 設計和驗證方法使設計工程師能夠?qū)W⒂谀切┙o產(chǎn)品及IP 帶來差異化和價值的系統(tǒng)設計屬性,即功能性和性能。本文討論電子系統(tǒng)級(ESL)設計和驗證方法學在系統(tǒng)級芯片(SoC)設

2009-11-30 16:15:15 33

33 本文從SoC (System on a Chip)驗證環(huán)境外在的框架結(jié)構、內(nèi)在的驗證數(shù)據(jù)的組織與管理和體現(xiàn)其工作原理的系統(tǒng)腳本的設計思想三方面出發(fā),討論SoC 驗證環(huán)境的搭建方法,并搭建的驗證環(huán)

2009-12-14 09:52:58 22

22 基于SOC 的USB 主設備的軟硬件協(xié)同驗證李棟1,李正衛(wèi)2(桂林電子科技大學通信與信息工程系,廣西 桂林 541004)摘 要:本文首先介紹了SOC 軟硬件協(xié)同驗證方法及其平臺Seamless

2009-12-14 11:31:21 15

15 本文介紹了基于事務的SoC驗證方法,詳細說明了事務、事務處理器的概念和事務級驗證平臺的功能結(jié)構。Synopsys公司的RVM驗證方法學是當前比較流行的基于事務的SoC驗證方法,文中詳細

2010-02-24 11:44:04 8

8 在芯片的研發(fā)環(huán)節(jié),FPGA 驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約

2010-06-24 17:43:35 29

29 隨著SoC設計復雜度的提高,驗證已成為集成電路設計過程中的瓶頸,而FPGA技術的快速發(fā)展以及良好的可編程特性使基于FPGA的原型驗證越來越多地被用于SoC系統(tǒng)的設計過程。本文討論

2010-11-11 16:00:07 35

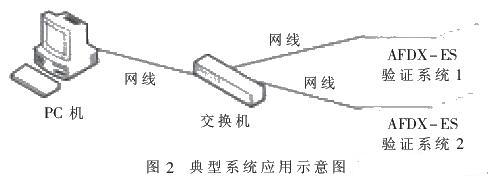

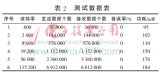

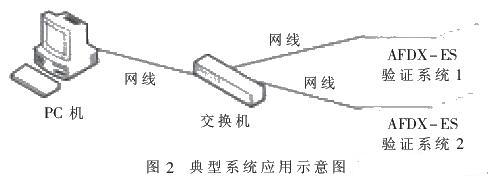

35 以SoC軟硬件協(xié)同設計方法學及驗證方法學為指導,系統(tǒng)介紹了以ARM9為核心的AFDX-ES SoC設計過程中,軟硬件協(xié)同設計和驗證平臺的構建過程及具體實施。應用實踐表明該平臺具有良

2010-11-22 15:18:52 56

56 針對基于軟件仿真片上網(wǎng)絡NoC(Network on Chip)效率低的問題,提出基于FPGA的NoC驗證平臺構建方案。該平臺集成可重用的流量產(chǎn)生器TG(Traffic Generation),流量接收器TR(Traffic Receiver)

2011-01-04 16:24:38 12

12 摘 要: 以SoC軟硬件協(xié)同設計方法學及驗證方法學為指導,系統(tǒng)介紹了以ARM9為核心的AFDX-ES SoC設計過程中,軟硬件協(xié)同設計和驗證平臺的構建過程及具體實施。應用實踐表明該

2010-12-08 10:44:41 1027

1027

臺灣工業(yè)技術研究院提出一種能夠顯著提升客制化FPGA原型板驗證效率的創(chuàng)新方法,自動化現(xiàn)有的 電路仿真 (in-circuit emulation)偵錯功能,并提供更高的FPGA能見度。這個以FPGA為基礎的SoC驗

2011-09-09 11:35:24 871

871

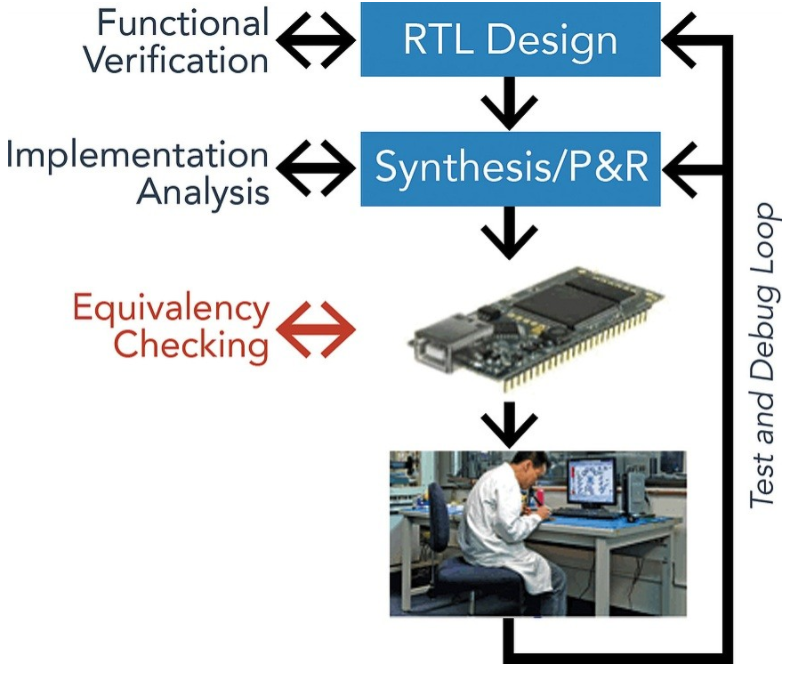

第一編 驗證的重要性 驗證,顧名思義就是通過仿真、時序分析、上板調(diào)試等手段檢驗設計正確性的過程,在 FPGA / IC 開發(fā)流程中,驗證主要包括功能驗證和時序驗證兩個部分。為了了解

2012-05-18 11:50:21 7663

7663 芯片驗證的工作量約占整個芯片研發(fā)的70%,已然成為縮短芯片上市時間的瓶頸。應用OVM方法學搭建SoC設計中的DMA IP驗證平臺,可有效提高驗證效率。

2012-06-20 09:03:29 2627

2627 基于開放的多語言構架庫的解決方案,詳述了多語言協(xié)同驗證技術的原理以及驗證平臺的搭建方法,并通過實例驗證了所提方案的有效性和靈活性。

2015-12-31 09:25:13 12

12 應用于宇航領域的新型元器件必須經(jīng)過嚴格的性能功能的驗證,傳統(tǒng)的驗證平臺是針對特定的待驗證器件設計的,不同的器件需要設計不同的驗證平臺,使得驗證工作周期長、成本高、可移植性差。本文介紹基于FPGA

2017-11-17 03:00:45 1027

1027

設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協(xié)同驗證架構,討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗證

2017-11-17 03:06:01 3769

3769

隨著集成電路設計技術的發(fā)展和芯片集成度的提高,驗證已經(jīng)成為芯片設計流程中的主要瓶頸。本文設計了一個基于FPGA的智能卡驗證平臺,并對驗證方法做了詳細闡述。本文對于雙界面智能卡芯片驗證的成功實踐

2017-11-17 16:25:01 1037

1037 利用Xilinx的FPGA設計了一個FPGA原型驗證平臺,用于無源高頻電子標簽芯片的功能驗證。主要描述了驗證平臺的硬件設計,解決了由分立元件實現(xiàn)模擬射頻前端電路時存在的問題,提出了FPGA器件選型

2017-11-18 08:42:22 1938

1938

驗證RTL模塊或FPGA是否滿足要求可能頗具挑戰(zhàn)。但有些方法可用來優(yōu)化驗證流程,以確保驗證成功。驗證FPGA或RTL模塊可能是一個非常耗時的過程,因為工程師要極力確保設計能夠按照規(guī)范要求并在可能導致

2017-11-18 10:06:01 604

604

門陣列(FPGA)做為安謀國際核心測試芯片,進而建構SoC原型制作平臺。 驗證SoC設計 FPGA原型最穩(wěn)當 FPGA原型制作是在FPGA上實作SoC或特定應用集成電路(ASIC)設計的方法,并進行硬件驗證和早期軟件開發(fā)。

2018-05-11 09:07:00 2405

2405

有關FPGA設計驗證的相關方法

2018-04-03 15:01:41 10

10 本文提出的基于FPGA的NoC驗證平臺在仿真速度方面是一般基于HDL的軟件仿真的16 000倍,而基于PC機編寫的NoC軟件更增強了該平臺的靈活性和實用性。

2019-04-13 11:33:47 2053

2053

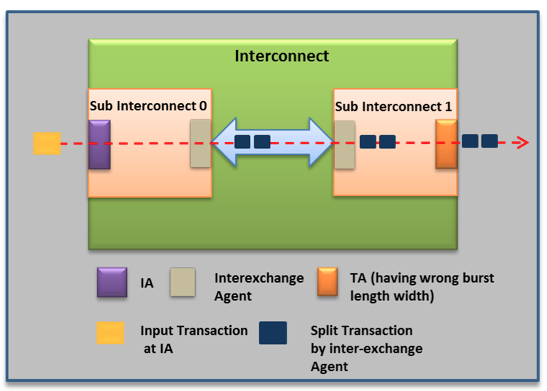

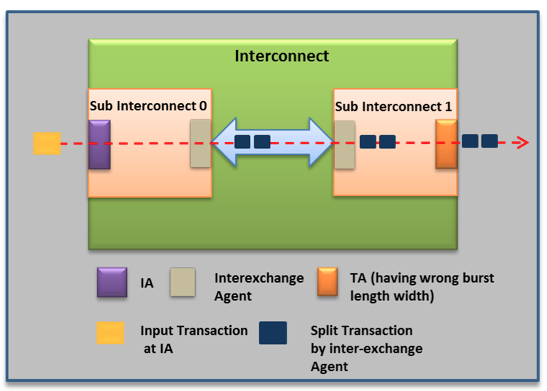

局間總線代理(如OCP 2.2,AXI 3.0,APB 3.0)。在這里,我們通過使用前兩篇文章中提到的一致方法描述了我們在SoC驗證早期階段捕獲的一些主要問題。

2019-08-12 11:22:54 2299

2299

本文以軟件工程的視角切入,分析中科院計算所某片上系統(tǒng)(SoC)項目的驗證平臺,同時也介紹當前較為流行的驗證方法,即以專門的驗汪語言結(jié)合商用的驗證模型,快速建立測試平臺(test-bench)并在今后的項目中重用(reuse)之。

2020-04-10 09:23:23 1151

1151

國微思爾芯(“S2C”), 全球領先的前端電子設計自動化 (EDA) 供應商, 發(fā)布全球首款FPGA驗證仿真云系統(tǒng) Prodigy Cloud System。這是為下一代 SoC 設計驗證需要而特別

2020-07-13 09:18:38 664

664 SoC設計中的驗證技術有哪些。

2021-03-29 10:37:30 12

12 歷時4月,可支持18億門SoC全芯片驗證的英諾達硬件驗證云平臺成都中心一期成功實現(xiàn)滿載運行,圓滿達成云平臺一期運營所有目標!英諾達的云平臺,不同于傳統(tǒng)的IDC機房,機器要求高、運營復雜、專業(yè)要求極高

2021-12-17 13:54:49 1771

1771 擁有如此多的利益相關者和優(yōu)先事項正在推動迫切需要一種更好的方法來完成 SoC 驗證。軟件定義的驗證和驗證環(huán)境和方法將使工程團隊能夠交付復雜的 SoC,滿足上市時間,提供更徹底的檢查,并降低風險和成本。

2022-06-02 10:00:02 1034

1034 確保汽車 SoC 在功能上安全還可以讓駕駛員和乘客對他們的車輛充滿信心。將安全驗證集成到功能驗證流程中可以是加快流程和管理符合 ISO 26262 等標準的工作的有效方法。

2022-06-13 15:17:20 1177

1177

隨著 FPGA 變得越來越大和越來越復雜,它們的設計和功能驗證趨向于 ASIC。在現(xiàn)代 FPGA 設計流程的先進性的推動下,這種趨勢現(xiàn)在正在擴展到實現(xiàn)驗證領域。EC 現(xiàn)在是該流程的必要組成部分,保留了 FPGA 生產(chǎn)過程中的固有效率。

2022-06-14 09:21:55 1080

1080

在現(xiàn)代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-03-28 09:33:16 854

854 我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-03-28 14:11:15 768

768 FPGA原型驗證在數(shù)字SoC系統(tǒng)項目當中已經(jīng)非常普遍且非常重要,但對于一個SoC的項目而言,選擇合適的FPGA原型驗證系統(tǒng)顯的格外重要

2023-04-03 09:46:45 928

928 當SoC系統(tǒng)的規(guī)模很大的時候,單片FPGA驗證平臺已經(jīng)無法容納這么多容量,我們將采取將SoC設計劃分為多個FPGA的映射。

2023-04-06 11:20:48 603

603 FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 FPGA原型驗證平臺系統(tǒng)靈活性主要體現(xiàn)在其外部連接表現(xiàn)形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統(tǒng)。

2023-04-11 09:50:03 628

628 FPGA原型驗證系統(tǒng)要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-04-19 09:08:15 852

852 當SoC的規(guī)模在一片FPGA中裝不下的時候,我們通常選擇多片FPGA原型驗證的平臺來承載整個SoC系統(tǒng)。

2023-05-23 15:31:10 319

319 FPGA原型驗證系統(tǒng)要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-05-23 16:50:34 381

381

我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-05-30 11:10:27 769

769

在現(xiàn)代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-05-30 15:04:06 905

905

當SoC系統(tǒng)的規(guī)模很大的時候,單片FPGA驗證平臺已經(jīng)無法容納這么多容量,我們將采取將SoC設計劃分為多個FPGA的映射。

2023-06-19 15:42:08 543

543 很多其他行業(yè)也能從電子器件的增加受益,當然保障功能安全是大的前提。本文討論SOC芯片設計驗證、驗證計劃和策略以及驗證方法。它定義了功能模擬、功能覆蓋、代碼覆蓋以及設計驗證中使用的重要術語。本文還涉及FPGA驗證及其在S

2023-07-20 09:05:59 597

597 proFPGA是mentor的FPGA原型驗證平臺,當然mentor被西門子收購之后,現(xiàn)在叫西門子EDA。

2024-01-22 09:21:01 546

546

FPGA驗證和UVM驗證在芯片設計和驗證過程中都扮演著重要的角色,但它們之間存在明顯的區(qū)別。

2024-03-15 15:00:41 94

94 FPGA原型驗證流程是確保FPGA(現(xiàn)場可編程門陣列)設計正確性和功能性的關鍵步驟。它涵蓋了從設計實現(xiàn)到功能驗證的整個過程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 97

97 FPGA原型驗證平臺與硬件仿真器在芯片設計和驗證過程中各自發(fā)揮著獨特的作用,它們之間存在明顯的區(qū)別。

2024-03-15 15:07:03 131

131

電子發(fā)燒友App

電子發(fā)燒友App

評論