摘要:在軟硬件的開發階段中,測試結果直接關系到這個軟硬件能否順利進行調試應用。其中,硬件的測試往往容易受外界因素的影響,如環境、計算機設備等,可以通過一些仿真軟件來避免外界環境的影響,但是其測試速度比較慢,不利于硬件的開發進度。面對這一難題,文章從FPGA 的軟硬件協同測試角度出發,利用PC 機和測試硬件設備的特點,進行FPGA 的軟硬件協同測試的設計,努力實現FPGA 的軟硬件協調測試系統在軟硬件的測試和分析中的應用。

FPGA是現場可編程門陣列,是集成電路的一個新型門類,具有高度的靈活性、可現場定義相關數據存儲容的能力、可反復改寫程序等特點。在不久的將來,FPGA 將在很大程度上取代標準的數字集成電路,從而引起電子數據系統在設計方式上的變革,使其朝著集成電路的方向發展。目前,我國在計算機應用領域方面對基于FPGA 的軟硬件協同測試的設計是比較重視的。

FPGA主要依賴于集成電路的發展,采用FPGA的數字化硬件設備,在圖像處理中的優勢越來越突出。每一個新的計算機軟硬件產生,都必須經過測試,合格后才能正式投入使用。由此可見測試對于計算機軟硬件設計開發的重要性。

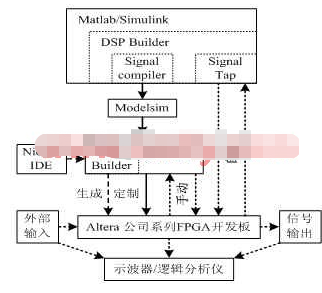

1 系統框架設計

系統框架設計是整個系統設計的整體概念,在這個過程中設計者需要對整個軟硬件協同測試系統進行全局把握,明確其系統設計目的,并運用軟硬件協同測試原理,結合軟硬件協同測試的影響因素,PC 機與測試系統通信的設計及實時數據傳輸通道的設計來構建其系統設計框架。

1.1 軟硬件協同測試原理

軟硬件協同測試是通過對PC機進行模擬的設備輸入、輸出,來實現對硬件設備電路的測試。軟硬件協同測試避免了PC 機在仿真過程中花費時間長的問題,充分利用了PC 機的系統資源,同時又發揮了硬件設備在電路工作過程中的高效,為硬件設備的測試提供了實時、高效的測試環境。

基于FPGA 的軟硬件協同測試是將PC 機與待測試硬件設備相連接,能夠將PC 機的資源充分利用,同時也能將硬件設備的高效工作速度發揮出來,可以實現實時、高效的雙向數據傳輸,并能廣泛地應用于各種硬件設備的開發測試與分析。用戶在進行硬件設備的測試過程中,可以根據自身的需求,對單向傳輸通道或是雙向傳輸通道進行選擇。

1.2 軟硬件協同測試的影響因素

在進行軟硬件協同測試過程中,需要對能夠影響其測試結果的相關因素進行分析,盡可能地減少或是避免其影響因素對測試結果造成偏差。

1.2.1 測試系統與待測試硬件設備之間的接口方式

待測試硬件設備的接口一般不是固定不變的,具體的接口方式主要根據其硬件設備的使用對象而有所不同,如數據線的接口與主從控制的接口就有所不同,若為了方便軟硬件協同測試的進行,需要對測試硬件設備的接口進行相關的改進,使待測試硬件設備的接口標準化。

1.2.2 PC 機與測試系統的傳輸速度

在對待測試硬件設備進行實時測試過程中,待測試硬件設備的數據傳輸速度起到決定性作用。據相關資料顯示,通常情況下,電視信號的數據量所要求的傳輸頻率是28Mbps,軟硬件協同測試過程中PC 機與待測試硬件設備之間的傳輸頻率必須在100 Mbps 以上,才能夠保證數據在PC 機與待測試硬件設備之間進行實時傳輸。

1.2.3 雙向數據的實時傳輸

測試系統是模擬的待測試硬件設備在正常環境下的工作情況。所以,待測硬件設備的數據輸入、輸出等實時傳輸是對測試系統的最基本要求,也是保證硬件設備進行測試結果的真實性。PC 機的數據傳輸與待測試硬件設備有所不同,前者的通信模式通常是不定時的、突發的,后者往往是連續的、不間斷的,因此,在實現數據的雙向實時傳輸的過程中,測試系統對PC 機的設計存在著很大的改進空間。

1.3 PC 機與測試系統通信的設計

通常使用的USB、PCI 等數據接口可以保障PC 機與硬件設備測試系統之間的傳輸速度在100Mbps 以上。其中, PCI數據接口的傳輸數率比較高,但是不方便拔插,僅在一些計算機專業領域使用;USB數據接口的使用比較方便,是目前最普遍的數據接口。在硬件設備測試過程中,可以利用USB 數據接口的統一方便使用、即插即用、成本低廉等優點,將USB 作為其測試系統的數據接口。用戶在對硬件設備進行檢測時,只需要將外設同PC 機以外的總線進行連接,PC 機就可以對USB 數據接口的設備進行自動識別安裝。目前使用的USB2.0的最大傳輸速度是480Mbps,可以滿足PC機與硬件設備測試系統之間的傳輸速度需求。同時,USB 數據接口可以簡化測試系統的相關設計方案,方便用戶操作,節省測試成本。

1.4 實時數據傳輸通道的設計

待測試硬件設備的數據輸入、輸出是兩個完全獨立的實時通信,而USB 數據接口的通信模式是突發性的。數據傳輸方式的不統一,容易造成數據包在傳輸過程中的丟失。使用USB數據接口就需要解決傳輸方式不同而導致數據在傳輸過程中的丟失,保證設備之間進行數據實時傳輸和對輸出數據的結果進行運算。

2 控制電路設計

軟硬件協同測試的主要原理是對電路進行控制,以達到其測試的目的。本文以FPGA 為控制器、參與硬件設備測試系統與USB 數據接口的控制芯相關協議為例,來進行相關設計。其設計的出發點是根據待測試硬件設備的不同,設計出與之相適應的數據接口電路。

在整個設計過程中,SDRAM 的控制器功能主要是通過FPGA來實現的,主要包括SDRA控制器通過識讀、存儲數據、讀取等操作所獲取的信號、數據,來實現數據的雙向傳輸通道。

2.1 請求發生器

SDRA控制器在每接收到8 個單位的數據后,就會向服務器發出一個關于寫的請求;每識讀出8 個單位的數據后,就會向相應的服務器發出一個關于讀的請求。SDRA 的四個緩存分別用于兩對控制器發出的讀寫請求。

SDRA 控制器的構造框架:USB 數據接口通過數據通道對請求發生器、刷新計數器進行控制,當信號發生器向請求發生器在兩個以上請求時,仲裁器就根據SDRA決定運行的先后順序。

2.2 仲裁器

在請求發生器產生兩個及其以上的請求時,仲裁器會根據優先級別來決定SDRA 執行請求的先后順序,并將其反饋到請求發生器上。仲裁器的功能是保證數據傳輸通道的暢通。

2.3 有限狀態機

SDRA 控制的具體操作過程:狀態接收器在收到有關讀、寫命令后會將其狀態信息發送給信號發生器,進行相關數據的輸入、輸出。

目前使用最廣泛的一種方式就是采用自動預充電的模式,主要步驟如下:(1)執行200 納秒的空操作,來保障電源與時間信號的穩定性;(2)對SDRA 控制器中的區進行預充電操作;(3)執行至少兩次刷新操作,保證仲裁器下達先后順序指令的正確性。

2.4 信號發生器

根據SDRA 控制器的狀態機來判斷信號發生器的狀態,并隨之產生相應的SDRA 信號,包括CS、A、RAS 等。

2.5 數據通道

對FPGA 與待測硬件設備、USB 數據接口、控制芯片和SDRA 控制器的處理,主要是通過SDRA 數據緩存來實現的。

3 軟硬件協同測試的實現

根據PC機與待測試硬件設備的優缺點,對硬件設備進行測試過程中的影響因素分析,為達到更加真實的測試結果,進行軟硬件協同測試的相關結構組成部分的分析、測試過程中的各個部件的運行流程設計,形成了一個相對較準確、高效的測試環境。對于這樣一個軟硬件協同測試系統的最終實現,也需要經過向普通軟硬件的產品生命周期,經過產品的設計、開發、測試、調試等一系列過程。

3.1 協同測試系統

在軟硬件協同測試系統設計前期理念的前提下,對基于FPGA 的軟硬件協同測試的設計成果應該進行相應的功能成果的驗證。在計算機上面的相關軟件環境下完成FPGA 的文件配置下載和安裝后,形成一個軟硬件協同測試環境,再進行相關順序的步驟操作,同時,應該對其測試過程中的數據傳輸信號進行監控,以便與之前傳統硬件設備測試結果進行對比,為基于FPGA的軟硬件協同測試的實現創造有利的數據條件。

3.2 系統調試

按照設計目標,在實際的系統調試過程中,需要根據實際的調試結果進行相應的修改。

3.3 協同測試系統的驗證

協同測試系統的功能的可行性包含兩個方面的試驗結果,一方面是協同測試系統功能在測試中的具體體現,另一方面是協同測試系統對于數據傳輸的速度的測定和分析。

協同測試系統功能在測試中的具體體現:基于FPGA 的軟硬件協同測試通過了其內部的各個模塊功能的設計,說明了協同測試系統設計完全符合其設計之初的功能期望。

協同測試系統對于數據傳輸的速度的測定和分析:只需要在FPGA 上運行非常短的時間就能夠完成,表明在FPGA下的協同測試系統的初步設計構成,可以將硬件設備的高效工作速度發揮出來,可以實現實時、高效的雙向數據傳輸,并能廣泛地應用于各種硬件設備的開發測試與分析。

4 結語

隨著計算機科學技術的發展,軟硬件協同測試越來越受到重視和關注,也成為計算機領域的軟硬件測試研究方向。基于FPGA 的軟硬件協同測試在具體的系統測試過程中容易受到FPGA 容量的限制,因此,基于FPGA 的軟硬件協同測試系統設計開發的重點在于其數據雙向傳輸的速度。本文從FPGA 的軟硬件協同測試的角度出發,根據PC機和測試硬件設備的特點和影響其測試的因素,進行FPGA 的軟硬件協同測試原理設計、控制電路設計,并對軟硬件協同測試系統測試、調試等運營結果進行研究分析,使其最終能夠應用于各種軟硬件設備的測試和分析中。

電子發燒友App

電子發燒友App

評論