在FPGA 上設(shè)計(jì)一個高性能、靈活的、面積小的通信體系結(jié)構(gòu)是一項(xiàng)巨大的挑戰(zhàn)。大多數(shù)基于FPGA 的片上網(wǎng)絡(luò)都是運(yùn)行在一個單一時(shí)鐘下。隨著FPGA 技術(shù)的發(fā)展,Xilinx 公司推出了Virtex-4 平臺

2011-10-21 16:13:51 1270

1270

在多時(shí)鐘設(shè)計(jì)中可能需要進(jìn)行時(shí)鐘的切換。由于時(shí)鐘之間可能存在相位、頻率等差異,直接切換時(shí)鐘可能導(dǎo)致產(chǎn)生glitch。

2020-09-24 11:20:38 5317

5317

跨時(shí)鐘域處理是FPGA設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還是在校的學(xué)生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個問題。 在本篇文章中,主要

2020-11-21 11:13:01 3278

3278

01、如何決定FPGA中需要什么樣的時(shí)鐘速率 設(shè)計(jì)中最快的時(shí)鐘將確定 FPGA 必須能處理的時(shí)鐘速率。最快時(shí)鐘速率由設(shè)計(jì)中兩個觸發(fā)器之間一個信號的傳輸時(shí)間 P 來決定,如果 P 大于時(shí)鐘周期

2020-11-23 13:08:24 3565

3565

當(dāng)這些時(shí)鐘一啟動,它們之間存在一個固定的相位關(guān)系,如此可以避免任何建立時(shí)間和保持時(shí)間違規(guī)。只要時(shí)鐘沒有漂移,就沒有任何時(shí)序違規(guī)出現(xiàn),并且器件會如預(yù)想那樣工作。

2022-10-28 09:05:11 636

636 本文主要介紹Xilinx FPGA的GTx的參考時(shí)鐘。下面就從參考時(shí)鐘的模式、參考時(shí)鐘的選擇等方面進(jìn)行介紹。

2023-09-15 09:14:26 1956

1956

有一個有趣的現(xiàn)象,眾多數(shù)字設(shè)計(jì)特別是與FPGA設(shè)計(jì)相關(guān)的教科書都特別強(qiáng)調(diào)整個設(shè)計(jì)最好采用唯一的時(shí)鐘域。

2023-12-22 09:04:46 875

875

生成時(shí)鐘包括自動生成時(shí)鐘(又稱為自動衍生時(shí)鐘)和用戶生成時(shí)鐘。自動生成時(shí)鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時(shí)鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 400

400

FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(高級技巧):現(xiàn)代FPGA的結(jié)構(gòu)越來越復(fù)雜,多時(shí)鐘域的設(shè)計(jì)現(xiàn)在已是常態(tài)。對于功能電路來說,復(fù)位結(jié)構(gòu)都必不可少。在同步邏輯設(shè)計(jì)中如何很好地處理異步復(fù)位,甚至在多時(shí)鐘域之間傳遞

2020-04-22 14:47:39

嗨,我有一個4時(shí)鐘域的原始設(shè)計(jì)。在添加第5個時(shí)鐘域并將設(shè)計(jì)加載到芯片中后,該設(shè)計(jì)在硬件中不再起作用。我正在使用斯巴達(dá)3E 1600這是一個很大的設(shè)計(jì),但作為一個例子,我有一個簡單的計(jì)數(shù)器,如下所示

2019-06-17 14:32:33

本人菜鳥一枚,請問FPGA中(使用verilog)ChipScope顯示輸入時(shí)鐘信號(clk50M),報(bào)錯誤,如果通過pll獲取其他頻率比如clk40M,為什么ChipScope顯示的時(shí)鐘頻率一直為

2017-05-09 20:31:19

FPGA的全局時(shí)鐘是什么?什么是第二全局時(shí)鐘?在FPGA的主配置模式中,CCLK信號是如何產(chǎn)生的?

2021-11-01 07:26:34

當(dāng)信號在不相關(guān)或者異步時(shí)鐘域之間傳送時(shí),會出現(xiàn)壓穩(wěn)態(tài),它是導(dǎo)致包括FPGA 在內(nèi)的數(shù)字器件系統(tǒng)失敗的一種現(xiàn)象。本白皮書介紹FPGA 中的壓穩(wěn)態(tài),解釋為什么會出現(xiàn)這一現(xiàn)象,討論它是怎樣導(dǎo)致設(shè)計(jì)失敗的。

2019-08-09 08:07:10

本帖最后由 lee_st 于 2017-10-31 08:58 編輯

FPGA多時(shí)鐘設(shè)計(jì)

2017-10-21 20:28:45

大型設(shè)計(jì)

中FPGA 的

多時(shí)鐘設(shè)計(jì)策略Tim Behne 軟件與信號處理部經(jīng)理 Microwave Networks 公司Email:

[email protected]利用

2012-10-26 17:26:43

說FPGA的實(shí)現(xiàn),由于是基于觸發(fā)器的設(shè)計(jì)實(shí)現(xiàn),這就造成了,在布局布線時(shí),同一時(shí)鐘域但是布局相隔較遠(yuǎn)的同步器件再被相同時(shí)鐘觸發(fā)時(shí),會有延時(shí),這反映在時(shí)鐘的skew(相位傾斜),為了解決這個問題,時(shí)鐘樹就出

2019-07-09 08:00:00

跨時(shí)鐘域處理是FPGA設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還在校生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個問題。這里主要介紹三種跨時(shí)鐘域

2021-03-04 09:22:51

利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系。設(shè)計(jì)過程中最重要的一步是確定要用多少個不同的時(shí)鐘,以及如何進(jìn)行布線?

2019-08-30 08:31:41

摘要:FPGA異步時(shí)鐘設(shè)計(jì)中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個必須考慮的問題。本文介紹了FPGA異步時(shí)鐘設(shè)計(jì)中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時(shí)根據(jù)實(shí)踐經(jīng)驗(yàn)給出了解決這些問題的幾種同步策略。關(guān)鍵詞

2009-04-21 16:52:37

FPGA的多時(shí)鐘系統(tǒng)設(shè)計(jì) Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

FPGA設(shè)計(jì)中有多個時(shí)鐘域時(shí)如何處理?跨時(shí)鐘域的基本設(shè)計(jì)方法是:(1)對于單個信號,使用雙D觸發(fā)器在不同時(shí)鐘域間同步。來源于時(shí)鐘域1的信號對于時(shí)鐘域2來說是一個異步信號。異步信號進(jìn)入時(shí)鐘域2后,首先

2012-02-24 15:47:57

[size=11.818181991577148px]FPGA開發(fā)中,遇到的最多的就是異步時(shí)鐘域了。[size=11.818181991577148px]檢查初學(xué)者的代碼,發(fā)現(xiàn)最多的就是這類

2014-08-13 15:36:55

(10)FPGA跨時(shí)鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時(shí)鐘域處理5)結(jié)語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 07:47:50

FPGA設(shè)計(jì)重利用方法(Design Reuse Methodology)SRAM工藝FPGA的加密技術(shù)大規(guī)模FPGA設(shè)計(jì)中的多點(diǎn)綜合技術(shù)定點(diǎn)乘法器設(shè)計(jì)(中文)你的PLD是亞穩(wěn)態(tài)嗎_設(shè)計(jì)異步多時(shí)鐘系統(tǒng)的綜合以及描述技巧使用retiming提高FPGA性能

2014-04-30 23:57:42

很大。 在設(shè)計(jì)PLD/FPGA時(shí)通常采用幾種時(shí)鐘類型。時(shí)鐘可分為如下四種類型:全局時(shí)鐘、門控時(shí)鐘、多級邏輯時(shí)鐘和波動式時(shí)鐘。多時(shí)鐘系統(tǒng)能夠包括上述四種時(shí)鐘類型的任意組合。1.全局時(shí)鐘對于一個設(shè)計(jì)項(xiàng)目

2012-12-14 16:02:37

時(shí)鐘域電路設(shè)計(jì)中由于不存在時(shí)鐘之間的延遲和錯位,所以建立條件和保持條件的時(shí)間約束容易滿足。而在多時(shí)鐘域里由于各個模塊的非同步性,則必須考慮亞穩(wěn)態(tài)的發(fā)生,如圖1所示。 2 多時(shí)鐘域數(shù)據(jù)傳遞方案 多時(shí)鐘

2011-09-07 09:16:40

時(shí)鐘)的邏輯。在真正的ASIC設(shè)計(jì)領(lǐng)域,單時(shí)鐘設(shè)計(jì)非常少。2、控制信號從快時(shí)鐘域同步到慢時(shí)鐘域與同步器相關(guān)的一個問題是來自發(fā)送時(shí)鐘域的信號可能在被慢時(shí)鐘域采樣之前變化。將慢時(shí)鐘域的控制信號同步到快時(shí)鐘域

2022-04-11 17:06:57

文章目錄前言時(shí)鐘及時(shí)鐘域時(shí)鐘,時(shí)序邏輯的心跳時(shí)鐘信...

2021-07-29 07:43:44

1、IC設(shè)計(jì)中的多時(shí)鐘域處理方法簡析我們在ASIC或FPGA系統(tǒng)設(shè)計(jì)中,常常會遇到需要在多個時(shí)鐘域下交互傳輸?shù)膯栴},時(shí)序問題也隨著系統(tǒng)越復(fù)雜而變得更為嚴(yán)重。跨時(shí)鐘域處理技術(shù)是IC設(shè)計(jì)中非常重要的一個

2022-06-24 16:54:26

視頻信號(包括數(shù)據(jù)與時(shí)鐘,其中數(shù)據(jù)位寬16位,時(shí)鐘1位,最高工作頻率148.5MHZ).2.遇到的問題時(shí)鐘相對于數(shù)據(jù)的延時(shí),也就是信號的建立與保持時(shí)間在經(jīng)過FPGA后出現(xiàn)偏移。造成后端的DA不能正確的采集到數(shù)據(jù)。

2014-02-10 16:08:02

利用 FPGA 實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA 具有以多個時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘 FPGA 設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系

2012-03-05 14:42:09

跨越時(shí)鐘域FPGA設(shè)計(jì)中可以使用多個時(shí)鐘。每個時(shí)鐘形成一個FPGA內(nèi)部時(shí)鐘域“,如果需要在另一個時(shí)鐘域的時(shí)鐘域產(chǎn)生一個信號,需要特別小心。隧道四部分第1部分:過路處。第2部分:道口標(biāo)志第3部分:穿越

2012-03-19 15:16:20

跨時(shí)鐘域處理是FPGA設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還在校生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個問題。這里主要介紹三種跨時(shí)鐘域

2021-02-21 07:00:00

60MHz的時(shí)鐘上升沿變化,而FPGA內(nèi)部需要使用100MHz的時(shí)鐘來處理ADC采集到的數(shù)據(jù)(多bit)。在這種類似的場景中,我們便可以使用異步雙口RAM來做跨時(shí)鐘域處理。 先利用ADC芯片提供的60MHz

2021-01-08 16:55:23

ISE中編譯為.bit文件。系統(tǒng)被設(shè)計(jì)為多重鎖定域,其中第一個域只是獲取數(shù)據(jù)并負(fù)責(zé)寫入和重置共享FIFO,并且從相機(jī)計(jì)時(shí)(因此也以相同的時(shí)鐘速度運(yùn)行 - 大約8MHz) - 此信號用于Sys.gen。具有

2019-08-27 06:28:47

關(guān)于異步時(shí)鐘域的理解的問題: 這里面的count[25]、和count[14]和count[1]算是多時(shí)鐘域吧?大俠幫解決下我的心結(jié)呀,我這樣的理解對嗎?

2012-02-27 15:50:12

你好,我在Viv 2016.4上使用AC701板。我需要同步從一個時(shí)鐘域到另一個時(shí)鐘域的多位信號(33位)。對我來說,這個多位信號的3階段流水線應(yīng)該足夠了。如果將所有觸發(fā)器放在同一個相同的切片

2020-08-17 07:48:54

在FPGA 上設(shè)計(jì)一個高性能、靈活的、面積小的通信體系結(jié)構(gòu)是一項(xiàng)巨大的挑戰(zhàn)。大多數(shù)基于FPGA 的片上網(wǎng)絡(luò)都是運(yùn)行在一個單一時(shí)鐘下。隨著FPGA 技術(shù)的發(fā)展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

本帖最后由 mingzhezhang 于 2012-5-23 20:05 編輯

大型設(shè)計(jì)中FPGA的多時(shí)鐘設(shè)計(jì)策略 利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個時(shí)鐘運(yùn)行的多重

2012-05-23 19:59:34

利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系。設(shè)計(jì)過程中

2015-05-22 17:19:26

跨時(shí)鐘域處理是 FPGA 設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個 FPGA 初學(xué)者的必修課。如果是還在校生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個問題。這里主要介紹三種跨

2020-09-22 10:24:55

跨時(shí)鐘域處理是FPGA設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還是在校的學(xué)生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個問題。在本篇文章中,主要

2021-07-29 06:19:11

跨時(shí)鐘域處理是什么意思?如何處理好跨時(shí)鐘域間的數(shù)據(jù)呢?有哪幾種跨時(shí)鐘域處理的方法呢?

2021-11-01 07:44:59

時(shí)鐘域轉(zhuǎn)換中亞穩(wěn)態(tài)是怎樣產(chǎn)生的?多時(shí)鐘域數(shù)據(jù)傳遞的FPGA實(shí)現(xiàn)

2021-04-30 06:06:32

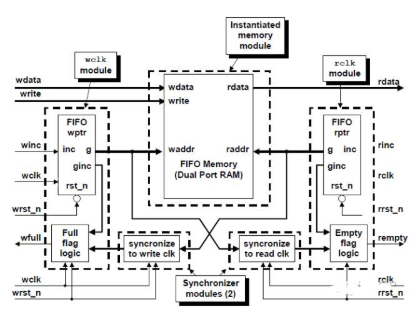

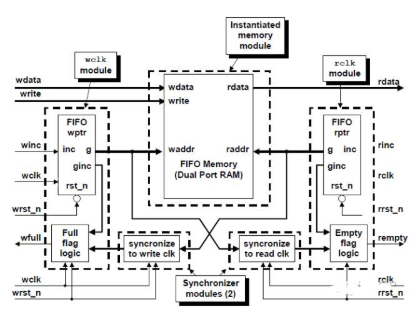

對多時(shí)鐘系統(tǒng)的同步問題進(jìn)行了討論?提出了亞穩(wěn)態(tài)的概念及其產(chǎn)生機(jī)理和危害;敘述了控制信號和數(shù)據(jù)通路在多時(shí)鐘域之間的傳遞?討論了控制信號的輸出次序?qū)ν郊夹g(shù)的不同要求,重點(diǎn)論述了常用的數(shù)據(jù)通路同步技術(shù)----用FIFO實(shí)現(xiàn)同步的原理及其實(shí)現(xiàn)思路

2012-05-23 19:54:32

親愛的朋友們, 我有一個多鎖設(shè)計(jì)。時(shí)鐘為50MHz,200MHz和400Mhz。如果僅使用400MHz時(shí)鐘并使用時(shí)鐘使能產(chǎn)生200Mhz和50Mhz時(shí)鐘域。現(xiàn)在我需要將信號從一個時(shí)鐘域傳遞到另一個

2019-03-11 08:55:24

跨時(shí)鐘域處理是 FPGA 設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個 FPGA 初學(xué)者的必修課。如果是還在校生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個問題。這里主要介紹三種跨

2020-10-20 09:27:37

大型設(shè)計(jì)中FPGA的多時(shí)鐘設(shè)計(jì)策略利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動、最大時(shí)鐘數(shù)、異步時(shí)鐘

2020-04-26 07:00:00

邏輯出身的農(nóng)民工兄弟在面試時(shí)總難以避免“跨時(shí)鐘域”的拷問,在諸多跨時(shí)鐘域的方法里,握手是一種常見的方式,而Stream作為一種天然的握手信號,不妨看看它里面是如做跨時(shí)鐘域的握手

2022-07-07 17:25:02

。雖然這樣可以簡化時(shí)序分析以及減少很多與多時(shí)鐘域有關(guān)的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時(shí)鐘常常又不現(xiàn)實(shí)。FPGA時(shí)常需要在兩個不同時(shí)鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收

2022-10-14 15:43:00

小弟最近在研究FPGA時(shí)鐘資源的手冊,遇到一個問題想請教各位大神。在Virtex6系列FPGA中,Bank分為top層和bottom層,請問我怎么查看一個Bank到底是在top層還是在bottom層

2015-02-10 10:30:25

請問,想通過FPGA的PLL倍頻產(chǎn)生個500MHz的時(shí)鐘來使用,以此時(shí)鐘來做定時(shí)精密延遲,不知道PLL倍頻倍數(shù)有什么要求,比如好像有的器件支持不到500MHz,有沒有可推薦的器件呢

補(bǔ)充內(nèi)容 (2017-1-4 09:26):

或者有大神用過類似能到500MHz的FPGA推薦么

2017-01-03 17:04:23

1、跨時(shí)鐘域信號的約束寫法 問題一:沒有對設(shè)計(jì)進(jìn)行全面的約束導(dǎo)致綜合結(jié)果異常,比如沒有設(shè)置異步時(shí)鐘分組,綜合器對異步時(shí)鐘路徑進(jìn)行靜態(tài)時(shí)序分析導(dǎo)致誤報(bào)時(shí)序違例。 約束文件包括三類,建議用戶應(yīng)該將

2022-11-15 14:47:59

bq1_dat穩(wěn)定在1,bq2_dat也輸出穩(wěn)定的1。最后,從特權(quán)同學(xué)的經(jīng)驗(yàn)和實(shí)踐的角度聊一下。跨時(shí)鐘域的信號同步到底需要1級還是2級,完全取決于具體的應(yīng)用。如果設(shè)計(jì)中這類跨時(shí)鐘域信號特別多,增加1級

2020-08-20 11:32:06

] set_false_paths –from [get_clocks clk_66] –to [get_clocks clk_100]設(shè)計(jì)中fifo前端時(shí)鐘域是cmos_pclk在TimeQuest

2018-07-03 11:59:59

,以及為帶門控時(shí)鐘的低功耗ASIC進(jìn)行原型驗(yàn)證。本章討論一下在FPGA設(shè)計(jì)中多時(shí)鐘域和異步信號處理有關(guān)的問題和解決方案,并提供實(shí)踐指導(dǎo)。

這里以及后面章節(jié)提到的時(shí)鐘域,是指一組邏輯,這組邏輯中的所有同步

2023-06-02 14:26:23

Multiple Clock System Design PLD設(shè)計(jì)技巧—多時(shí)鐘系統(tǒng)設(shè)計(jì)

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 DLL在FPGA時(shí)鐘設(shè)計(jì)中的應(yīng)用:在ISE集成開發(fā)環(huán)境中,用硬件描述語言對FPGA 的內(nèi)部資源DLL等直接例化,實(shí)現(xiàn)其消除時(shí)鐘的相位偏差、倍頻和分頻的功能。時(shí)鐘電路是FPGA開發(fā)板設(shè)計(jì)中的

2009-11-01 15:10:30 33

33 在大規(guī)模集成電路設(shè)計(jì)中,一個系統(tǒng)包含了很多不相關(guān)的時(shí)鐘信號,當(dāng)其目標(biāo)域時(shí)鐘與源域時(shí)鐘不同時(shí),如何在這些不同域之間傳遞數(shù)據(jù)成為了一個重要問題。為了解決這個問題,

2009-12-14 10:19:07 14

14 本文闡述了用于FPGA的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探討了FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案。

2010-08-06 16:08:45 12

12 大型設(shè)計(jì)中FPGA的多時(shí)鐘設(shè)計(jì)策略

利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率

2009-12-27 13:28:04 645

645

1 多時(shí)鐘片上網(wǎng)絡(luò)架構(gòu)的分析

片上網(wǎng)絡(luò)結(jié)構(gòu)包含了拓?fù)浣Y(jié)構(gòu)、流量控制、路由、緩沖以及仲裁。選擇合適網(wǎng)絡(luò)架構(gòu)方面的元素,將對片上網(wǎng)絡(luò)的性能產(chǎn)生重大影響[2]

2010-09-02 09:43:47 832

832

本文采用FPGA來設(shè)計(jì)一款廣泛應(yīng)用于計(jì)算機(jī)、Modem、數(shù)據(jù)終端以及許多其他數(shù)字設(shè)備之間的數(shù)據(jù)傳輸?shù)膶S卯惒讲⑿型ㄐ沤涌谛酒瑢?shí)現(xiàn)了某一 時(shí)鐘域 (如66 MHz)的8位并行數(shù)據(jù)到另一低時(shí)

2011-08-29 11:33:44 905

905

在FPGA設(shè)計(jì)中,為了成功地操作,可靠的時(shí)鐘是非常關(guān)鍵的。設(shè)計(jì)不良的時(shí)鐘在極限的溫度、電壓下將導(dǎo)致錯誤的行為。在設(shè)計(jì)PLD/FPGA時(shí)通常采用如下四種類型時(shí)鐘:全局時(shí)鐘、門控時(shí)鐘

2011-09-21 18:38:58 3472

3472

基于AD9540產(chǎn)生多時(shí)鐘輸出

2011-11-25 00:02:00 31

31 利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)

2012-05-21 11:26:10 1100

1100

DLL在_FPGA時(shí)鐘設(shè)計(jì)中的應(yīng)用,主要說明DLL的原理,在Xilinx FPGA中是怎么實(shí)現(xiàn)的。

2015-10-28 14:25:42 1

1 FPGA學(xué)習(xí)資料,有興趣的同學(xué)可以下載看看。

2016-04-07 16:33:47 0

0 基于FPGA的數(shù)字時(shí)鐘設(shè)計(jì),可實(shí)現(xiàn)鬧鐘的功能,可校時(shí)。

2016-06-23 17:15:59 64

64 如何正確使用FPGA的時(shí)鐘資源

2017-01-18 20:39:13 22

22 很大。 在設(shè)計(jì)PLD/FPGA時(shí)通常采用幾種時(shí)鐘類型。時(shí)鐘可分為如下四種類型:全局時(shí)鐘、門控時(shí)鐘、多級邏輯時(shí)鐘和波動式時(shí)鐘。多時(shí)鐘系統(tǒng)能夠包括上述四種時(shí)鐘類型的任意組合。

2017-11-25 09:16:01 3907

3907

跨時(shí)鐘域問題(CDC,Clock Domain Crossing )是多時(shí)鐘設(shè)計(jì)中的常見現(xiàn)象。在FPGA領(lǐng)域,互動的異步時(shí)鐘域的數(shù)量急劇增加。通常不止數(shù)百個,而是超過一千個時(shí)鐘域。

2019-08-19 14:52:58 2854

2854 時(shí)鐘是FPGA設(shè)計(jì)中最重要的信號,FPGA系統(tǒng)內(nèi)大部分器件的動作都是在時(shí)鐘的上升沿或者下降沿進(jìn)行。

2019-09-20 15:10:18 5065

5065

一、概述 在大規(guī)模ASIC或FPGA設(shè)計(jì)中,多時(shí)鐘系統(tǒng)往往是不可避免的,這樣就產(chǎn)生了不同時(shí)鐘域數(shù)據(jù)傳輸?shù)膯栴},其中一個比較好的解決方案就是使用異步FIFO來作不同時(shí)鐘域數(shù)據(jù)傳輸?shù)木彌_區(qū),這樣既可以

2020-07-17 09:38:20 478

478

有一個有趣的現(xiàn)象,眾多數(shù)字設(shè)計(jì)特別是與FPGA設(shè)計(jì)相關(guān)的教科書都特別強(qiáng)調(diào)整個設(shè)計(jì)最好采用唯一的時(shí)鐘域。

2020-09-24 10:20:00 2487

2487

利用 FPGA 實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA 具有以多個時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA 設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系。設(shè)計(jì)過程中最重要的一步是確定要用多少個不同的時(shí)鐘,以及如何進(jìn)行布線,本文將對這些設(shè)計(jì)策略深入闡述。

2021-01-15 15:57:00 14

14 AN-769: 基于AD9540產(chǎn)生多時(shí)鐘輸出

2021-03-18 23:03:12 2

2 引言:從本文開始,我們陸續(xù)介紹Xilinx 7系列FPGA的時(shí)鐘資源架構(gòu),熟練掌握時(shí)鐘資源對于FPGA硬件設(shè)計(jì)工程師及軟件設(shè)計(jì)工程師都非常重要。本章概述7系列FPGA時(shí)鐘,比較了7系列FPGA時(shí)鐘

2021-03-22 10:25:27 4326

4326 減少很多與多時(shí)鐘域有關(guān)的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時(shí)鐘常常又不現(xiàn)實(shí)。 FPGA時(shí)常需要在兩個不同時(shí)鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時(shí)鐘的低功耗

2021-05-10 16:51:39 3719

3719

減少很多與多時(shí)鐘域有關(guān)的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時(shí)鐘常常又不現(xiàn)實(shí)。FPGA時(shí)常需要在兩個不同時(shí)鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時(shí)鐘的低功耗

2021-09-23 16:39:54 2763

2763 一、概述 在大規(guī)模ASIC或FPGA設(shè)計(jì)中,多時(shí)鐘系統(tǒng)往往是不可避免的,這樣就產(chǎn)生了不同時(shí)鐘域數(shù)據(jù)傳輸?shù)膯栴},其中一個比較好的解決方案就是使用異步FIFO來作不同時(shí)鐘域數(shù)據(jù)傳輸?shù)木彌_區(qū),這樣既可以

2021-09-30 09:57:40 1533

1533

(08)FPGA時(shí)鐘概念1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時(shí)鐘概念5)結(jié)語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (29)FPGA原語設(shè)計(jì)(差分時(shí)鐘轉(zhuǎn)單端時(shí)鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設(shè)計(jì)(差分時(shí)鐘轉(zhuǎn)單端時(shí)鐘)5)結(jié)語1.2 FPGA簡介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原語設(shè)計(jì)(單端時(shí)鐘轉(zhuǎn)差分時(shí)鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設(shè)計(jì)(單端時(shí)鐘轉(zhuǎn)差分時(shí)鐘)5)結(jié)語1.2 FPGA簡介FPGA

2021-12-29 19:41:48 10

10 在大規(guī)模ASIC或FPGA設(shè)計(jì)中,多時(shí)鐘系統(tǒng)往往是不可避免的,這樣就產(chǎn)生了不同時(shí)鐘域數(shù)據(jù)傳輸?shù)膯栴},其中一個比較好的解決方案就是使用異步FIFO來作不同時(shí)鐘域數(shù)據(jù)傳輸?shù)木彌_區(qū),這樣既可以使相異時(shí)鐘域數(shù)據(jù)傳輸?shù)臅r(shí)序要求變得寬松,也提高了它們之間的傳輸效率。此文內(nèi)容就是闡述異步FIFO的設(shè)計(jì)。

2022-03-09 16:29:18 2309

2309 ?xilinx 的 FPGA 時(shí)鐘結(jié)構(gòu),7 系列 FPGA 的時(shí)鐘結(jié)構(gòu)和前面幾個系列的時(shí)鐘結(jié)構(gòu)有了很大的區(qū)別,7系列的時(shí)鐘結(jié)構(gòu)如下圖所示。

2022-07-03 17:13:48 2592

2592 ASIC 和FPGA芯片的內(nèi)核之間最大的不同莫過于時(shí)鐘結(jié)構(gòu)。ASIC設(shè)計(jì)需要采用諸如時(shí)鐘樹綜合、時(shí)鐘延遲匹配等方式對整個時(shí)鐘結(jié)構(gòu)進(jìn)行處理,但是 FPGA設(shè)計(jì)則完全不必。

2022-11-23 16:50:49 686

686

我們在ASIC或FPGA系統(tǒng)設(shè)計(jì)中,常常會遇到需要在多個時(shí)鐘域下交互傳輸?shù)膯栴},時(shí)序問題也隨著系統(tǒng)越復(fù)雜而變得更為嚴(yán)重。

2023-04-06 10:56:35 413

413 當(dāng)設(shè)計(jì)存在多個時(shí)鐘時(shí),根據(jù)時(shí)鐘的相位和頻率關(guān)系,分為同步時(shí)鐘和異步時(shí)鐘,這兩類要分別討論其約束

2023-04-06 14:34:28 886

886

FPGA多bit跨時(shí)鐘域適合將計(jì)數(shù)器信號轉(zhuǎn)換為格雷碼。

2023-05-25 15:21:31 1953

1953

減少很多與多時(shí)鐘域有關(guān)的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時(shí)鐘常常又不現(xiàn)實(shí)。FPGA時(shí)常需要在兩個不同時(shí)鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時(shí)鐘的低功耗

2023-08-23 16:10:01 336

336

電子發(fā)燒友App

電子發(fā)燒友App

評論