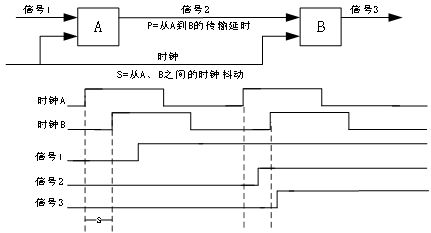

設(shè)計(jì)中最快的時(shí)鐘將確定 FPGA 必須能處理的時(shí)鐘速率。最快時(shí)鐘速率由設(shè)計(jì)中兩個(gè)觸發(fā)器之間一個(gè)信號(hào)的傳輸時(shí)間 P 來(lái)決定,如果 P 大于時(shí)鐘周期 T,則當(dāng)信號(hào)在一個(gè)觸發(fā)器上改變后,在下一個(gè)邏輯級(jí)上將不會(huì)改變,直到兩個(gè)時(shí)鐘周期以后才改變,如圖所示。

圖1

02、FPGA所使用的時(shí)鐘必須具有低抖動(dòng)特性

傳輸時(shí)間為信號(hào)在第一個(gè)觸發(fā)器輸出處所需的保持時(shí)間加上兩級(jí)之間的任何組合邏輯的延遲,再加兩級(jí)之間的布線(xiàn)延遲以及信號(hào)進(jìn)入第二級(jí)觸發(fā)器的設(shè)置時(shí)間。無(wú)論時(shí)鐘速率為多少,每一個(gè) FPGA 設(shè)計(jì)所用的時(shí)鐘必須具有低抖動(dòng)特性。抖動(dòng) S 是觸發(fā)器的一個(gè)時(shí)鐘輸入到另一個(gè)觸發(fā)器的時(shí)鐘輸入之間的最大延遲。為使電路正常工作,抖動(dòng)必須小于兩個(gè)觸發(fā)器之間的傳輸時(shí)間。

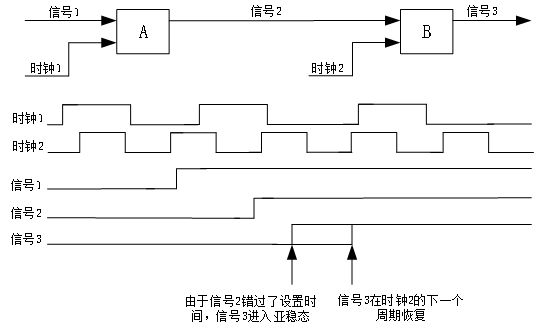

圖 2 顯示了如果抖動(dòng)大于傳輸時(shí)間(S>P)將出現(xiàn)的情況,該電路用時(shí)鐘的兩個(gè)上升沿來(lái)延 遲信號(hào) 1。然而,信號(hào) 1 上的一個(gè)改變會(huì)在相同的時(shí)鐘周期上傳輸?shù)降男盘?hào) 3 上,從而引起信號(hào) 2 的改變。因?yàn)?S > P,電路將不能不正常。

圖2

注意事項(xiàng)

須注意的是,時(shí)鐘速率與傳輸延時(shí)并沒(méi)有什么關(guān)系,甚至普通的 100bps 時(shí)鐘也會(huì)出現(xiàn)抖動(dòng)問(wèn)題。這意味著雖然 FPGA 供應(yīng)商宣稱(chēng)他們的芯片具有較短的傳輸時(shí)間和很高的時(shí)鐘速率,但抖動(dòng)問(wèn)題可能會(huì)嚴(yán)重,甚至那些沒(méi)有運(yùn)行在最高速率上的設(shè)計(jì)也是如此。

好在 FPGA 供應(yīng)商已經(jīng)認(rèn)識(shí)到時(shí)鐘抖動(dòng)的影響,并在他們的芯片中提供低抖動(dòng)的布線(xiàn)資源。這些特殊的布線(xiàn)能夠在芯片中一個(gè)給定范圍內(nèi)的任何兩個(gè)觸發(fā)器之間提供一個(gè)確定的最大抖動(dòng)。部分產(chǎn)品的低抖動(dòng)資源覆蓋了整個(gè)芯片,而其它的則可能只覆蓋了 FPGA 邏輯塊中的一個(gè)特定的行或列。對(duì)于一個(gè)需要很多不同時(shí)鐘源的設(shè)計(jì),這些低抖動(dòng) FPGA 是比較理想的選擇。

03、多時(shí)鐘設(shè)計(jì)中使用異步時(shí)鐘將兩級(jí)邏輯結(jié)合

多時(shí)鐘設(shè)計(jì)的最嚴(yán)重問(wèn)題之一是用異步時(shí)鐘將兩級(jí)邏輯結(jié)合在一起。由于異步時(shí)鐘會(huì)產(chǎn)生亞穩(wěn)態(tài),從而嚴(yán)重降低設(shè)計(jì)性能,或完全破壞設(shè)計(jì)所能實(shí)現(xiàn)的功能。在觸發(fā)器的時(shí)序要求產(chǎn)生沖突時(shí)(設(shè)置時(shí)間和保持時(shí)間)將產(chǎn)生亞穩(wěn)態(tài),觸發(fā)器的最終輸出是未知的,并使整個(gè)設(shè)計(jì)處于不確定狀態(tài)。如果有一級(jí)邏輯要將數(shù)據(jù)異步地發(fā)送到另一級(jí),圖 3 所示的情形將不能滿(mǎn)足觸發(fā)器的設(shè)置和保持時(shí)間要求。確切地說(shuō),如果設(shè)計(jì)中含有異步邏輯將有可能會(huì)產(chǎn)生亞穩(wěn)態(tài)。在處置異步資源時(shí)必需非常小心,因?yàn)檫@可能產(chǎn)生一些很?chē)?yán)重的問(wèn)題。

圖3

在用異步時(shí)鐘產(chǎn)生任何邏輯前應(yīng)該盡量先考慮采用其它替代方法,用異步時(shí)鐘的組合邏輯是產(chǎn)生亞穩(wěn)態(tài)問(wèn)題的主要原因。同樣,當(dāng)違反觸發(fā)器的設(shè)置和保持時(shí)間約束時(shí),在一個(gè)短時(shí)間內(nèi)輸出將具有不確定性,并且將最終設(shè)定在“1”或“0”上,確切的狀態(tài)不可預(yù)知。

幸好在面對(duì)亞穩(wěn)態(tài)時(shí),已經(jīng)有了一些解決方案。比如雙寄存器方法:進(jìn)入第一級(jí)觸發(fā)器的數(shù)據(jù)與時(shí)鐘異步,所以第一級(jí)觸發(fā)器幾乎肯定是亞穩(wěn)態(tài);然而,只要亞穩(wěn)態(tài)的長(zhǎng)度小于時(shí)鐘的周期,第二級(jí)觸發(fā)器就不會(huì)進(jìn)入亞穩(wěn)態(tài)。但是,F(xiàn)PGA 供應(yīng)商很少提供亞穩(wěn)態(tài)時(shí)間,盡管該時(shí)間一般小于觸發(fā)器的設(shè)置和保持時(shí)間之和。

編輯:hfy-

FPGA

+關(guān)注

關(guān)注

1643文章

21966瀏覽量

614143 -

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123356

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

一文看懂!時(shí)鐘在數(shù)據(jù)采集系統(tǒng)中究竟起到哪些關(guān)鍵作用?

基于FPGA的數(shù)字時(shí)鐘設(shè)計(jì)

請(qǐng)問(wèn)ADC32xx的時(shí)鐘由FPGA直接輸出嗎?

如果用FPGA采集AD1672,如何保障FPGA時(shí)鐘同1672時(shí)鐘一致?

ADS58C48的輸出給FPGA的時(shí)鐘怎樣產(chǎn)生的,是只要有輸入時(shí)鐘,就有輸出時(shí)鐘嗎?

DAC5675的數(shù)據(jù)和時(shí)鐘到底怎么設(shè)計(jì)才算合理?

時(shí)序約束一主時(shí)鐘與生成時(shí)鐘

DDR4時(shí)鐘頻率和速率的關(guān)系

PLL1707-Q1多時(shí)鐘發(fā)生器數(shù)據(jù)表

PLL1705/PLL1706雙通道PLL多時(shí)鐘發(fā)生器數(shù)據(jù)表

LMH1982多速率視頻時(shí)鐘發(fā)生器數(shù)據(jù)表

FPGA中時(shí)鐘速率和多時(shí)鐘設(shè)計(jì)案例分析

FPGA中時(shí)鐘速率和多時(shí)鐘設(shè)計(jì)案例分析

評(píng)論