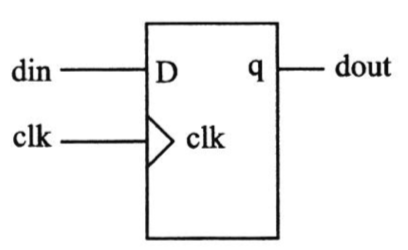

xilinx verilog語(yǔ)法技巧 一 硬件描述語(yǔ)言(HDL)編碼技術(shù)讓您: ?描述數(shù)字邏輯電路中最常見的功能。 ?充分利用Xilinx?器件的架構(gòu)特性。 1 Flip-Flops

2020-12-13 10:29:00 3065

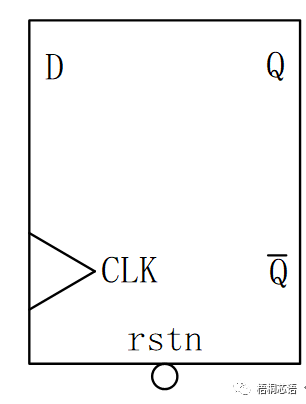

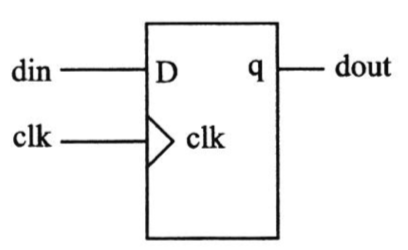

3065 現(xiàn)代邏輯設(shè)計(jì)中,時(shí)序邏輯設(shè)計(jì)是核心,而寄存器又是時(shí)序邏輯的基礎(chǔ),下面將介紹幾種常見的寄存器的Verilog設(shè)計(jì)代碼供初學(xué)者進(jìn)行學(xué)習(xí)理解。

2023-07-27 09:03:59 1899

1899

Verilog HDL硬件描述語(yǔ)言

2013-01-13 14:40:20

Verilog HDL的語(yǔ)法,希望能幫助正在學(xué)習(xí)或者要用到的朋友

2014-05-25 14:10:04

;5"><strong>Verilog HDL硬件描述語(yǔ)言。J.Bhasker著,徐振林等譯<br/></strong></font><br/>

2009-08-21 12:37:14

Verilog HDL硬件描述語(yǔ)言(非常經(jīng)典的教材)FPGA軟件無線電開發(fā)(全階視頻教程+開發(fā)板+實(shí)例)詳情鏈接:http://url.elecfans.com/u/5e4a12f2ba

2013-07-22 14:50:03

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214.5.2 寄存器類型

2017-12-08 14:39:50

本帖最后由 IC那些事兒 于 2020-11-30 19:05 編輯

Verilog HDL是一種硬件描述語(yǔ)言,用于從算法級(jí)、門級(jí)到開關(guān)級(jí)的多種抽象設(shè)計(jì)層次的數(shù)字系統(tǒng)建模。被建模的數(shù)字系統(tǒng)對(duì)象

2020-11-30 19:03:38

前不久學(xué)FPGA,找到的verilog的教程 第1章 簡(jiǎn) 介 本章介紹Verilog HDL語(yǔ)言的發(fā)展歷史和它的主要能力。 1.1什么是Verilog HDL? Verilog HDL是一種硬件描述

2018-07-03 05:19:30

Level):描述數(shù)據(jù)在寄存器之間流動(dòng)和如何處理這些數(shù)據(jù)的模型。? 門級(jí)(gate-level):描述邏輯門以及邏輯門之間的連接的模型。? 開關(guān)級(jí)(switch-level):描述器件中三極管和儲(chǔ)存節(jié)點(diǎn)以及它們之間連接的模型。

2019-09-06 09:14:16

本合集資料包括:1.Verilog HDL程序設(shè)計(jì)實(shí)例詳解2.Verilog HDL經(jīng)典教程3.Verilog HDL實(shí)驗(yàn)練習(xí)與語(yǔ)法手冊(cè)4.Verilog HDL硬件描述語(yǔ)言

2020-08-21 10:06:20

我是FPGA的新手想請(qǐng)教一下Verilog中什么時(shí)候需要給變量定義寄存器。一開始我以為每個(gè)輸入、輸出都要定義沒定義的話默認(rèn)為一,但是今天看到一段代碼輸入變量[3:0] key_in并沒有定義寄存器。

2017-01-18 19:55:47

Verilog_HDL硬件描述語(yǔ)言 FPGA的資料

2013-02-26 14:03:42

verilog+hdl硬件描述語(yǔ)言 初學(xué)者的福音 幫助廣大初學(xué)者步入此行

2013-08-12 23:47:12

個(gè)人覺得如果用“HDL通用寄存器描述”一個(gè)32位寄存器,則綜合需要32個(gè)LUT(假設(shè)每個(gè)LUT后有1個(gè)FF)。而用廠家 distributed ram 原語(yǔ)描述,則是不是可把每個(gè)LUT用做RAM

2012-10-04 22:44:03

各位大佬有會(huì)FPGA Verilog HDL編程的嘛,小弟現(xiàn)在有一個(gè)關(guān)于移位寄存器的問題想問:利用ASM流程圖寫出代碼!!有會(huì)的可以聯(lián)系我!可支付酬金!!

2019-11-15 06:19:58

NVIC是與內(nèi)核高度集成的外設(shè),由ARM負(fù)責(zé)設(shè)計(jì),與其他外設(shè)不同,因此在ST的參考手冊(cè)中并為過多提及,具體的寄存器需要參考 M4內(nèi)核參考手冊(cè) 。寄存器描述 core_cm4.htypedef

2022-01-24 07:14:57

大,目前很多國(guó)外大學(xué)都使用SystemVerilog作為教學(xué)語(yǔ)言。本文以Verilog語(yǔ)言為基礎(chǔ)講述HDL代碼編寫技巧。RAM部分內(nèi)容比較多,單獨(dú)放在第27篇講述。1.觸發(fā)器、寄存器和鎖存器

2020-09-29 10:08:57

《Verilog_HDL硬件描述語(yǔ)言》_,[美]貝斯克(Bhasker,J.)_,徐振林等譯

2013-04-18 15:57:52

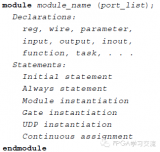

、寄存器、線網(wǎng)和參數(shù)等的說明部分必須在使用前出現(xiàn)。為了使模塊描述清晰和具有良好的可讀性, 最好將所有的說明部分放在語(yǔ)句前。圖 2-6 所示的是一個(gè)半加器。圖 2-6 半加器這個(gè)半加器用 Verilog

2018-09-18 09:37:40

、數(shù)據(jù)流方式、結(jié)構(gòu)化方式;? Verilog HDL 中有線網(wǎng)(Wire)數(shù)據(jù)類型和寄存器(Reg)數(shù)據(jù)類型兩類數(shù)據(jù)類型,線網(wǎng)類型表示構(gòu)件間的物理連線,而寄存器類型表示抽象的數(shù)據(jù)存儲(chǔ)元件。? 能夠描述

2018-09-18 09:33:31

硬件描述語(yǔ)言Verilog,西安科大教學(xué)課件,總共包括完整八個(gè)章節(jié)學(xué)習(xí)內(nèi)容。具體每章節(jié)內(nèi)容如下第一章:Verilog HDL數(shù)字集成電路設(shè)計(jì)方法概述第二章:Verilog HDL基礎(chǔ)知識(shí)第三章

2021-03-30 14:31:41

邏輯,應(yīng)在敏感信號(hào)表中列出所有的輸入信號(hào);7、所有的內(nèi)部寄存器都應(yīng)該可以被復(fù)位;8、用戶自定義原件(UDP元件)是不能被綜合的。一:基本Verilog中的變量有線網(wǎng)類型和寄存器類型。線網(wǎng)型變量綜合成wire,而寄存器可能綜合成WIRE,鎖存器和觸發(fā)器,還有可能被優(yōu)化掉。二:veril...

2021-07-29 06:10:04

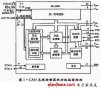

CAM具有什么功能?基于移位寄存器的CAM的設(shè)計(jì)基于移位寄存器的CAM的Verilog HDL實(shí)現(xiàn)

2021-04-13 06:28:23

Verilog模型有哪幾種?Verilog HDL模型是由哪些模塊構(gòu)成的?如何用Verilog HDL語(yǔ)言描述D型主從觸發(fā)器模塊?

2021-10-19 08:36:32

)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。HDL硬件描述語(yǔ)言(HDL)是一種用來設(shè)計(jì)數(shù)字邏輯系統(tǒng)和描述數(shù)字電路的語(yǔ)言,常用的主要有VHDL、Verilog HDL、System Verilog 和 System C。VHDL是一種用于電路設(shè)計(jì)的高級(jí)

2021-12-22 07:39:43

Verilog HDL Synthesis (A Practical Primer)

2009-02-12 09:36:24 40

40 本書簡(jiǎn)要介紹了Verilog硬件描述語(yǔ)言的基礎(chǔ)知識(shí),包括語(yǔ)言的基本內(nèi)容和基本結(jié)構(gòu) ,以及利用該語(yǔ)言在各種層次上對(duì)數(shù)字系統(tǒng)的建模方法。書中列舉了大量實(shí)例,幫助讀者掌握語(yǔ)言

2009-07-20 11:36:35 0

0 Verilog-HDL實(shí)踐與應(yīng)用系統(tǒng)設(shè)計(jì)本書從實(shí)用的角度介紹了硬件描述語(yǔ)言Verilog-HDL。通過動(dòng)手實(shí)踐,體驗(yàn)Verilog-HDL的語(yǔ)法結(jié)構(gòu)、功能等內(nèi)涵。在前五章,以簡(jiǎn)單的實(shí)例列舉了Verilog-HDL的用法;

2009-11-14 22:57:40 146

146 Verilog HDL 華為入門教程

本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能

2010-02-11 08:35:38 140

140 本書簡(jiǎn)要介紹了Verilog 硬件描述語(yǔ)言的基礎(chǔ)知識(shí),包括語(yǔ)言的基本內(nèi)容和基本結(jié)構(gòu),以及利用該語(yǔ)言在各種層次上對(duì)數(shù)字系統(tǒng)的建模方法。書中列舉了大量實(shí)例,幫助讀者掌握

2010-07-02 14:55:51 124

124 摘要:一種利用Verilog HDL設(shè)計(jì)CAM的方案,該方案以移位寄存器為核心,所實(shí)現(xiàn)的CAN具有可重新配置改變字長(zhǎng)、易于擴(kuò)展、匹配查找速度等特點(diǎn),并在網(wǎng)絡(luò)協(xié)處理器仿

2006-05-26 21:52:14 933

933

什么是Verilog HDL?

Verilog HDL是一種硬件描述語(yǔ)言,用于從算法級(jí)、門級(jí)到開關(guān)級(jí)的多種抽象設(shè)計(jì)層次的數(shù)字系統(tǒng)建模。被建模的數(shù)字系統(tǒng)

2009-01-18 14:53:26 3678

3678

【摘 要】 基于EPP協(xié)議的特點(diǎn),應(yīng)用復(fù)雜可編程邏輯器件(CPLD)開發(fā)了移位寄存器輸出接口。介紹了EPP協(xié)議和接口的Verilog HDL描述。

2009-05-11 19:34:31 1215

1215

摘要:一種利用Verilog HDL設(shè)計(jì)CAM的方案,該方案以移位寄存器為核心,所實(shí)現(xiàn)的CAN具有可重新配置改變字長(zhǎng)、易于擴(kuò)展、匹配查找速度等特點(diǎn),并在網(wǎng)絡(luò)協(xié)處理器仿真中得到

2009-06-20 12:49:52 1307

1307

摘要: 介紹了一種采用硬件控制的自動(dòng)數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方法,包括數(shù)字系統(tǒng)自頂向下的設(shè)計(jì)思路、Verilog HDL對(duì)系統(tǒng)硬件的描述和狀態(tài)機(jī)的設(shè)計(jì)以及MAX+PLUSII開發(fā)

2009-06-20 14:57:47 1264

1264

Verilog HDL程序基本結(jié)構(gòu)與程序入門

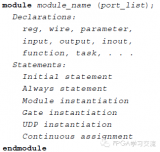

Verilog HDL程序基本結(jié)構(gòu)

Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語(yǔ)言。用Verilog HDL描述的

2010-02-08 11:43:30 2185

2185 Verilog HDL語(yǔ)言簡(jiǎn)介

1.什么是Verilog HDLVerilog HDL是硬件描述語(yǔ)言的一種,用于數(shù)

2010-02-09 08:59:33 3609

3609 VHDL和Verilog HDL語(yǔ)言對(duì)比

Verilog HDL和VHDL都是用于邏輯設(shè)計(jì)的硬件描述語(yǔ)言,并且都已成為IEEE標(biāo)準(zhǔn)。VHDL是在1987年成為IEEE標(biāo)準(zhǔn),Verilog HDL

2010-02-09 09:01:17 10317

10317 寄存器,寄存器是什么意思

寄存器定義 寄存器是中央處理器內(nèi)的組成部分。寄存器是有限存貯容量的高速存貯部件,它們可用

2010-03-08 14:26:32 20897

20897 在我國(guó)使用Verilog HDL的公司比使用VHDL的公司多。從EDA技術(shù)的發(fā)展上看,已出現(xiàn)用于CPLD/FPGA設(shè)計(jì)的硬件C語(yǔ)言編譯軟件,雖然還不成熟,應(yīng)用極少,但它有可能會(huì)成為繼VHDL和Verilog之后,設(shè)計(jì)大規(guī)模CPLD/FPGA的又一種手段。

2011-03-12 11:21:20 1686

1686 《Verilog HDL 程序設(shè)計(jì)教程》對(duì)Verilog HDL程序設(shè)計(jì)作了系統(tǒng)全面的介紹,以可綜合的設(shè)計(jì)為重點(diǎn),同時(shí)對(duì)仿真和模擬也作了深入的闡述。《Verilog HDL 程序設(shè)計(jì)教程》以Verilog-1995標(biāo)準(zhǔn)為基礎(chǔ)

2011-09-22 15:53:36 0

0 verilog硬件描述語(yǔ)言課程講義

2012-05-21 15:01:29 33

33 在此利用Verilog HDL設(shè)計(jì)了一款CAN總線控制器,首先根據(jù)協(xié)議把整個(gè)CAN總線控制器劃分為接口邏輯管理、寄存器邏輯和CAN核心模塊3個(gè)模塊,然后用Verilog HDL硬件描述語(yǔ)言設(shè)計(jì)了各個(gè)功能模塊

2012-07-31 14:25:24 7806

7806

Verilog_HDL的基本語(yǔ)法詳解(夏宇聞版):Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語(yǔ)言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)

2012-10-08 14:48:31 0

0 電子發(fā)燒友網(wǎng)核心提示 :目前,硬件描述語(yǔ)言(HDL)可謂是百花齊放,有VHDL、Superlog、Verilog、SystemC、Cynlib C++、C Level等等。電子發(fā)燒友網(wǎng)小編今天就帶大家一起來了解下幾種具有代表

2012-10-15 10:51:38 4127

4127 Verilog HDL程序設(shè)計(jì)與實(shí)踐著重介紹了Verilog HDL語(yǔ)言

2015-10-29 14:45:47 21

21 Verilog硬件描述語(yǔ)言參考手冊(cè),Verilog語(yǔ)法內(nèi)容介紹

2015-11-12 17:20:37 0

0 Verilog HDL硬件描述語(yǔ)言

有需要的下來看看

2015-12-29 15:31:27 0

0 本章講述Verilog HDL中的結(jié)構(gòu)建模方式。結(jié)構(gòu)建模方式用以下三種實(shí)例語(yǔ)句描述,verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 14:58:20 14

14 本章講述Verilog HDL指定用戶定義原語(yǔ)UDP的能力。UDP的實(shí)例語(yǔ)句與基本門的實(shí)例語(yǔ)句完全相同,即U D P實(shí)例語(yǔ)句的語(yǔ)法與基本門的實(shí)例語(yǔ)句語(yǔ)法一致。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 16:09:32 12

12 本章講述Verilog HDL為門級(jí)電路建模的能力,包括可以使用的內(nèi)置基本門和如何使用它們來進(jìn)行硬件描述。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 16:09:32 18

18 本章講述在Verilog HDL中編寫表達(dá)式的基礎(chǔ)。表達(dá)式由操作數(shù)和操作符組成。表達(dá)式可以在出現(xiàn)數(shù)值的任何地方使用。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 16:09:32 19

19 本章介紹Verilog HDL語(yǔ)言的發(fā)展歷史和它的主要能力。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-25 16:09:32 14

14 本章介紹Verilog HDL的基本要素,包括標(biāo)識(shí)符、注釋、數(shù)值、編譯程序指令、系統(tǒng)任務(wù)和系統(tǒng)函數(shù)。另外,本章還介紹了Verilog硬件描述語(yǔ)言中的兩種數(shù)據(jù)類型。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 16:09:32 16

16 本章描述Verilog HDL中的第三種建模方式,即行為建模方式。為充分使用Verilog HDL,一個(gè)模型可以包含所有上述三種建模方式。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-25 16:09:32 14

14 本章給出了一些用Verilog HDL編寫的硬件建模實(shí)例。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-25 16:09:32 25

25 本章介紹了如何編寫測(cè)試驗(yàn)證程序(test bench)。測(cè)試驗(yàn)證程序用于測(cè)試和驗(yàn)證設(shè)計(jì)的正確性。Verilog HDL提供強(qiáng)有力的結(jié)構(gòu)來說明測(cè)試驗(yàn)證程序。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-25 16:09:32 17

17 本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2016-07-15 15:27:00 0

0 verilog HDL,fpga,硬件電路學(xué)習(xí)資料

2016-09-01 14:55:49 0

0 VHDL語(yǔ)言編程學(xué)習(xí)Verilog硬件描述語(yǔ)言

2016-09-01 15:27:27 0

0 ;第4章至第6章主要討論如何合理地使用Verilog HDL語(yǔ)言描述高性能的可綜合電路;第7章和第8章重點(diǎn)介紹了如何編寫測(cè)試激勵(lì)以及Verilog的仿真原理;第9章展望HDL語(yǔ)言的發(fā)展趨勢(shì)。

2016-10-10 17:04:40 566

566 Verilog HDL硬件描述語(yǔ)言,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 11:20:11 11

11 Verilog HDL是一種硬件描述語(yǔ)言(HDL:Hardware Discription Language),Verilog HDL語(yǔ)言是一種以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

2017-02-11 14:00:20 35998

35998

本文描述的是GD32硬件中斷錯(cuò)誤的所有寄存器以及相應(yīng)的位功能。

2017-08-28 15:32:09 9

9 9s12系列單片機(jī)寄存器描述詳細(xì)

2017-10-24 10:40:21 10

10 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL入門教程之Verilog HDL數(shù)字系統(tǒng)設(shè)計(jì)教程。

2018-09-20 15:51:26 80

80 本文主要介紹了Verilog HDL 語(yǔ)言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL 設(shè)計(jì)方法,初步了解并掌握Verilog HDL語(yǔ)言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2019-02-11 08:00:00 95

95 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語(yǔ)言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語(yǔ)言也是一種結(jié)構(gòu)描述的語(yǔ)言。

2019-03-08 14:29:12 12094

12094 從數(shù)字電路中學(xué)到的邏輯電路功能,使用硬件描述語(yǔ)言(Verilog/VHDL)描述出來,這需要設(shè)計(jì)人員能夠用硬件編程思維來編寫代碼,以及擁有扎實(shí)的數(shù)字電路功底。

2019-12-05 07:10:00 2977

2977

Verilog HDL是一種硬件描述語(yǔ)言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語(yǔ)言,都是在20世紀(jì)80年代中期開發(fā)出來的。

2019-11-13 07:03:00 3029

3029 Verilog HDL是一種硬件描述語(yǔ)言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

2019-11-20 07:00:00 5088

5088 硬件描述語(yǔ)言基本語(yǔ)法和實(shí)踐

(1)VHDL 和Verilog HDL的各自特點(diǎn)和應(yīng)用范圍

(2)Verilog HDL基本結(jié)構(gòu)語(yǔ)言要素與語(yǔ)法規(guī)則

(3) Verilog HDL組合邏輯語(yǔ)句結(jié)構(gòu)

2019-07-03 17:36:00 53

53 Verilog HDL是一種硬件描述語(yǔ)言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。 Verilog HDL

2020-06-17 16:13:11 12910

12910 本書介紹了硬件描述和Verilog HDL概述、Verilog HDL的基本語(yǔ)法、Verilog HDL程序設(shè)計(jì)語(yǔ)句和描述方式、Verilog HDL對(duì)組合邏輯和時(shí)序邏輯的設(shè)計(jì)舉例、Verilog

2020-07-21 08:00:00 0

0 Verilog HDL和VHDL是目前兩種最常用的硬件描述語(yǔ)言,同時(shí)也都是IEEE標(biāo)準(zhǔn)化的HDL語(yǔ)言。

2020-08-25 09:14:34 8605

8605 的是硬件描述語(yǔ)言。最為流行的硬件描述語(yǔ)言有兩種Verilog HDL/VHDL,均為IEEE標(biāo)準(zhǔn)。Verilog HDL具有C語(yǔ)言基礎(chǔ)就很容易上手,而VHDL語(yǔ)言則需要Ada編程基礎(chǔ)。另外Verilog

2020-09-01 11:47:09 4002

4002

Verilog HDL是一種硬件描述語(yǔ)言(HDL:Hardware Description Language),以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。

2020-11-02 17:30:55 23

23 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog教程之Verilog HDL程序設(shè)計(jì)語(yǔ)句和描述方式。

2020-12-09 11:24:23 46

46 本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL硬件語(yǔ)義的詳細(xì)資料分析。

2021-02-01 15:37:11 13

13 進(jìn)行描述; 時(shí)序行為使用過程結(jié)構(gòu)描述。一個(gè)模塊可以在另一個(gè)模塊中使用。 一個(gè)模塊的基本語(yǔ)法如下: 說明部分用于定義不同的項(xiàng),例如模塊描述中使用的寄存器和參數(shù)。語(yǔ)句定義設(shè)計(jì)的功能和結(jié)構(gòu)。說明部分和語(yǔ)句可以散布在模塊中的任何地方

2021-03-12 16:24:28 1951

1951

1、如何使用Verilog HDL描述可綜合電路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL語(yǔ)言僅是對(duì)已知硬件電路的文本描述。所以編寫前: 對(duì)所需實(shí)現(xiàn)的硬件

2021-04-04 11:19:00 3837

3837

),這里的D也是描述的首字母。 也就是說,HDL的D,是描述的意義。HDL也就是硬件描述語(yǔ)言。 2. 為了支持Soc的驗(yàn)證,支持?jǐn)?shù)模混合,新的System Verilog加入了HVL(Hardware Verification Language),即硬件驗(yàn)證語(yǔ)言。 3. 合并之前的硬件描述語(yǔ)言功能,稱為

2021-04-15 15:44:02 2773

2773 其中,返回值的類型和位寬是可選項(xiàng),如果缺省會(huì)返回一位寄存器類型數(shù)據(jù)。Verilog HDL認(rèn)為函數(shù)的定義隱式地聲明了與函數(shù)同名的寄存器。函數(shù)的定義把函數(shù)被返回值所賦值寄存器的名稱初始化為與函數(shù)同名的內(nèi)部變量。

2021-07-02 10:24:26 1939

1939 Verilog HDL是一種以文本形式描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的硬件描述語(yǔ)言,也可描述邏輯電路圖、邏輯表達(dá)式等。Verilog HDL和VHDL是目前主流的、最受歡迎的兩種硬件描述語(yǔ)言。

2021-07-23 14:36:55 9910

9910 Verilog HDL入門教程-Verilog HDL的基本語(yǔ)法

2022-01-07 09:23:42 159

159 個(gè)人感覺:硬件描述語(yǔ)言(vhdl等):是為了制造cpu(類似的芯片),設(shè)計(jì)人員使用hdl設(shè)計(jì)和安排寄存器和時(shí)序電路如何組合,然后最終會(huì)生成門級(jí)網(wǎng)表,然后通過相關(guān)軟件等生成最終物理電氣電路(怎么布局

2022-01-13 15:09:46 0

0 HDLBits 是一組小型電路設(shè)計(jì)習(xí)題集,使用 Verilog/SystemVerilog 硬件描述語(yǔ)言 (HDL) 練習(xí)數(shù)字硬件設(shè)計(jì)~

2022-08-31 09:06:59 1168

1168 VersaClock 6E 系列寄存器描述和編程指南

2023-01-10 19:13:58 0

0 汽車 VersaClock 6E 寄存器描述和編程指南

2023-01-30 18:47:53 0

0 VersaClock 6 系列寄存器描述和編程指南

2023-03-15 19:12:28 0

0 VersaClock 6E 系列寄存器描述和編程指南

2023-06-30 20:07:01 2

2 汽車 VersaClock 6E 寄存器描述和編程指南

2023-07-03 20:13:38 0

0 VersaClock 6 系列寄存器描述和編程指南

2023-07-05 20:54:30 0

0 使用硬件描述語(yǔ)言(VHDL,Verilog HDL,業(yè)界公司一般都是使用后者)將模塊功能以代碼來描述實(shí)現(xiàn),也就是將實(shí)際的硬件電路功能通過HDL語(yǔ)言描述出來,形成RTL(寄存器傳輸級(jí))代碼。

2023-07-09 10:20:12 562

562

節(jié)通過硬件描述語(yǔ)言Verilog HDL對(duì)二十進(jìn)制編碼器的描述,介紹Verilog HDL程序的基本結(jié)構(gòu)及特點(diǎn)。

2023-08-28 09:54:34 1115

1115

Verilog HDL是一種硬件描述語(yǔ)言,以文本形式來描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。 Verilog HDL

2023-08-29 15:58:29 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論