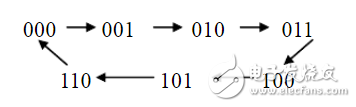

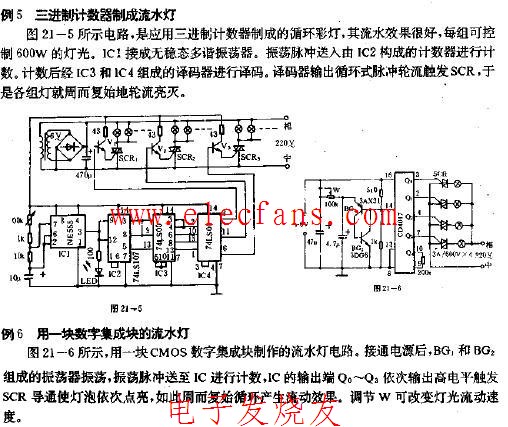

三進(jìn)制計(jì)數(shù)器制成流水燈

相關(guān)推薦

構(gòu)建LED二進(jìn)制計(jì)數(shù)器

電子發(fā)燒友網(wǎng)站提供《構(gòu)建LED二進(jìn)制計(jì)數(shù)器.zip》資料免費(fèi)下載

2023-06-12 09:54:30 0

0

0

0可預(yù)置同步BCD十進(jìn)制計(jì)數(shù)器;異步復(fù)位-74HC160

可預(yù)置同步BCD十進(jìn)制計(jì)數(shù)器;異步復(fù)位-74HC160

2023-02-20 20:05:50 4

4

4

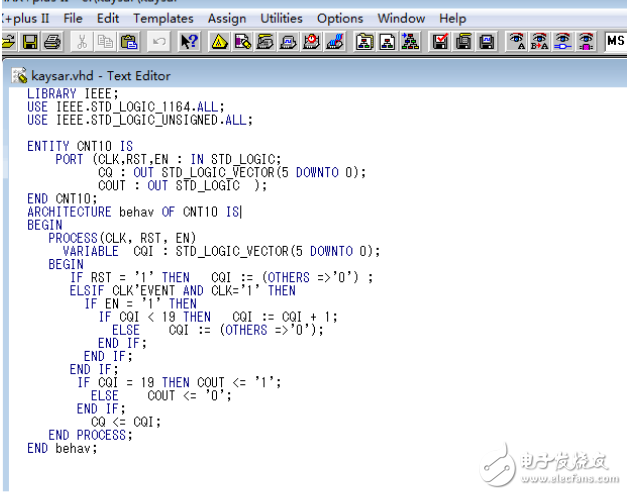

4基于FPGA的十進(jìn)制計(jì)數(shù)器

本方案是一個基于 FPGA ?的十進(jìn)制計(jì)數(shù)器。共陽極 7 段顯示器上的 0 到 9 十進(jìn)制計(jì)數(shù)器,硬件在 Xilinx Spartan 6 FPGA 板上實(shí)現(xiàn)。

2022-12-20 14:52:25 2

2

2

2構(gòu)建一個4位二進(jìn)制計(jì)數(shù)器

構(gòu)建一個4位二進(jìn)制計(jì)數(shù)器,計(jì)數(shù)范圍從0到15(包括0和15),計(jì)數(shù)周期為16。同步復(fù)位輸入時(shí),將計(jì)數(shù)器重置為0。

2022-12-02 09:20:28 1762

1762

1762

1762FPGA上的十六進(jìn)制計(jì)數(shù)器

電子發(fā)燒友網(wǎng)站提供《FPGA上的十六進(jìn)制計(jì)數(shù)器.zip》資料免費(fèi)下載

2022-11-23 10:47:06 7

7

7

7十進(jìn)制計(jì)數(shù)器的工作原理

二進(jìn)制編碼的十進(jìn)制是一個串行數(shù)字計(jì)數(shù)器,可計(jì)數(shù)十位數(shù)字,它會為每個新的時(shí)鐘輸入重置。由于它可以通過10種獨(dú)特的輸出組合,因此也被稱為“十進(jìn)制(BCD)計(jì)數(shù)器”。十進(jìn)制計(jì)數(shù)器可以計(jì)數(shù)0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

2022-10-31 16:25:37 11019

11019

11019

11019

數(shù)字二進(jìn)制計(jì)數(shù)器的設(shè)計(jì)和實(shí)現(xiàn)

將二進(jìn)制數(shù)視為元胞自動機(jī)可能有助于數(shù)字二進(jìn)制計(jì)數(shù)器的設(shè)計(jì)和實(shí)現(xiàn)嗎?

2022-07-28 11:47:10 840

840

840

840

CD4017十進(jìn)制計(jì)數(shù)器的應(yīng)用實(shí)驗(yàn)

CD4017 十進(jìn)制計(jì)數(shù)器的應(yīng)用實(shí)驗(yàn)

2022-05-11 16:58:25 47

47

47

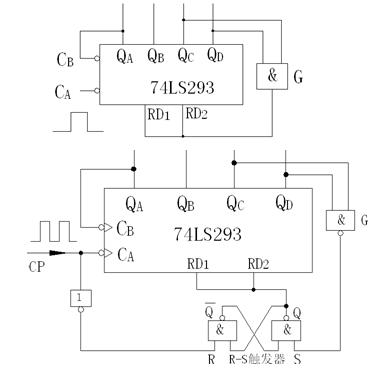

47N進(jìn)制計(jì)數(shù)器的實(shí)現(xiàn)

N進(jìn)制計(jì)數(shù)器的實(shí)現(xiàn) 一、用集成計(jì)數(shù)器可以實(shí)現(xiàn)任意進(jìn)制的計(jì)數(shù)器二、集成計(jì)數(shù)器控制功能的歸類三、集成計(jì)數(shù)器的級聯(lián)擴(kuò)展四、復(fù)位法組成任意進(jìn)制加法計(jì)數(shù)器五、置位法組成任意進(jìn)制加法計(jì)數(shù)器六

2008-07-05 13:41:26

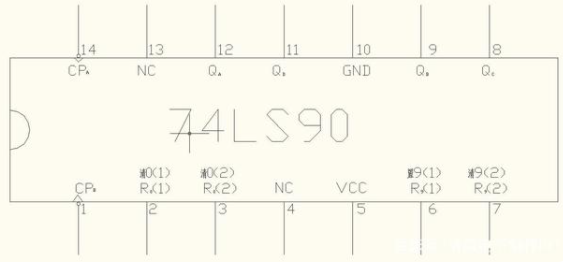

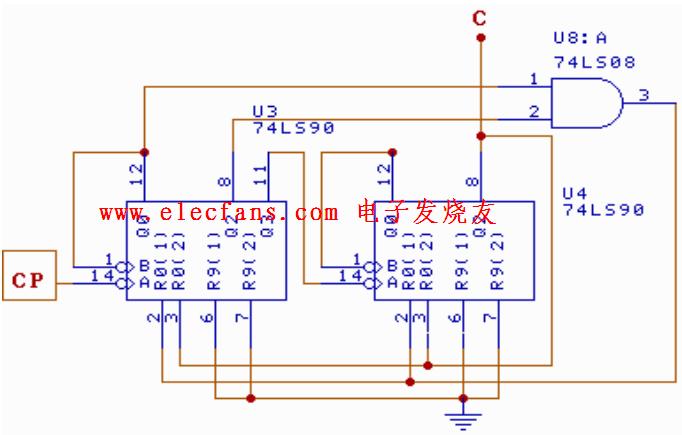

74LS90十進(jìn)制計(jì)數(shù)器的功能電路及真值表

其中CPa和Qa構(gòu)成1位二進(jìn)制計(jì)數(shù)器,CPb和Qd、Qc、Qb 組成五進(jìn)制計(jì)數(shù)器,將兩個計(jì)數(shù)器有關(guān)端子適當(dāng)組合,可以組成其他類型的計(jì)數(shù)器。R0(1)、R0(2)為兩個清0端,R9(1)、 R9(2)為兩 個置9端。

2021-06-21 09:39:44 34099

34099

34099

34099

同步7進(jìn)制計(jì)數(shù)器的設(shè)計(jì)資料免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是同步7進(jìn)制計(jì)數(shù)器的設(shè)計(jì)資料免費(fèi)下載。

2020-05-20 08:00:00 11

11

11

11用CD4017組成的l~17進(jìn)制計(jì)數(shù)器

十進(jìn)制計(jì)數(shù)器是人們最常用的計(jì)數(shù)器,但在某些特殊的計(jì)數(shù)場合下,也需要其他進(jìn)制的計(jì)數(shù)器。

2020-01-14 09:46:48 6705

6705

6705

6705

FPGA視頻教程之BJ-EPM240學(xué)習(xí)板Johnson計(jì)數(shù)器實(shí)驗(yàn)的詳細(xì)資料說明

所謂Johnson計(jì)數(shù)器,其實(shí)說白了無非就是復(fù)雜一-點(diǎn)的流水燈實(shí)驗(yàn)。流水燈加上了按鍵控制,流水燈的開啟關(guān)閉和變化方向在按鍵的控制下進(jìn)行。本實(shí)例是帶停止控制的雙向4bit Johnson 計(jì)數(shù)器,可以通過LED燈直觀的在學(xué)習(xí)板上進(jìn)行演示。該工程的接口義如表所示。

2019-03-04 17:06:48 6

6

6

6如何使用Multisim仿真一個60進(jìn)制的計(jì)數(shù)器

本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Multisim仿真一個60進(jìn)制的計(jì)數(shù)器的詳細(xì)資料免費(fèi)下載

2018-10-23 11:37:56 126

126

126

126由TTL十進(jìn)制計(jì)數(shù)器構(gòu)成的分頻器

關(guān)鍵詞:TTL , 分頻器 , 計(jì)數(shù)器 , 十進(jìn)制 如圖所示為由TTL十進(jìn)制計(jì)數(shù)器構(gòu)成的分頻電路。在許多情況下。需要對脈沖序列進(jìn)行N(N為整數(shù))分頻。例如,數(shù)字鐘需要進(jìn)行60分頻,得到重復(fù)頻率為

2018-10-03 18:46:02 2650

2650

2650

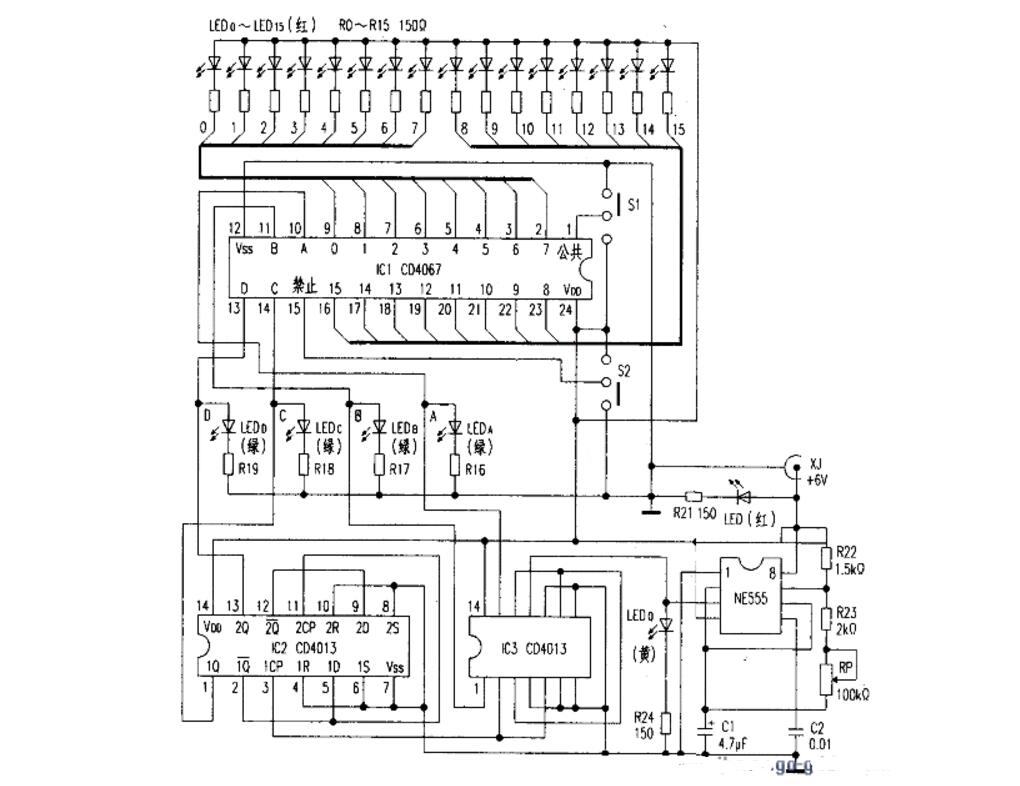

2650cd4067應(yīng)用電路圖大全(計(jì)數(shù)器/自動巡檢/流水燈數(shù)控/采集分站)

本文主要介紹了四款cd4067應(yīng)用電路圖。其中包括了cd4067計(jì)數(shù)器電路、十六通道數(shù)顯式自動巡檢電路和流水燈數(shù)控電路及采集分站電路。

2018-06-04 10:38:57 16356

16356

16356

16356

同步計(jì)數(shù)器74ls162設(shè)計(jì)24進(jìn)制計(jì)數(shù)器

本文首先介紹了計(jì)數(shù)器種類與應(yīng)用,其次介紹了74LS160并行置零法設(shè)計(jì)24進(jìn)制計(jì)數(shù)器電路圖,最后介紹了74ls162設(shè)計(jì)24進(jìn)制計(jì)數(shù)器原理電路圖。

2018-05-08 11:46:43 54648

54648

54648

54648基于74ls192設(shè)計(jì)4/7進(jìn)制計(jì)數(shù)器詳解

由題目及其要求分析可知,首先要使用74LS192或40192設(shè)計(jì)一個4進(jìn)制計(jì)數(shù)器和一個7進(jìn)制計(jì)數(shù)器,然后通過數(shù)碼管來顯示狀態(tài)。兩種進(jìn)制間的切換可以通過一個單刀雙擲開關(guān)來實(shí)現(xiàn)。其重點(diǎn)和難點(diǎn)在于設(shè)計(jì)一個4進(jìn)制計(jì)數(shù)器和一個7進(jìn)制計(jì)數(shù)器。

2018-01-31 16:18:13 54591

54591

54591

54591

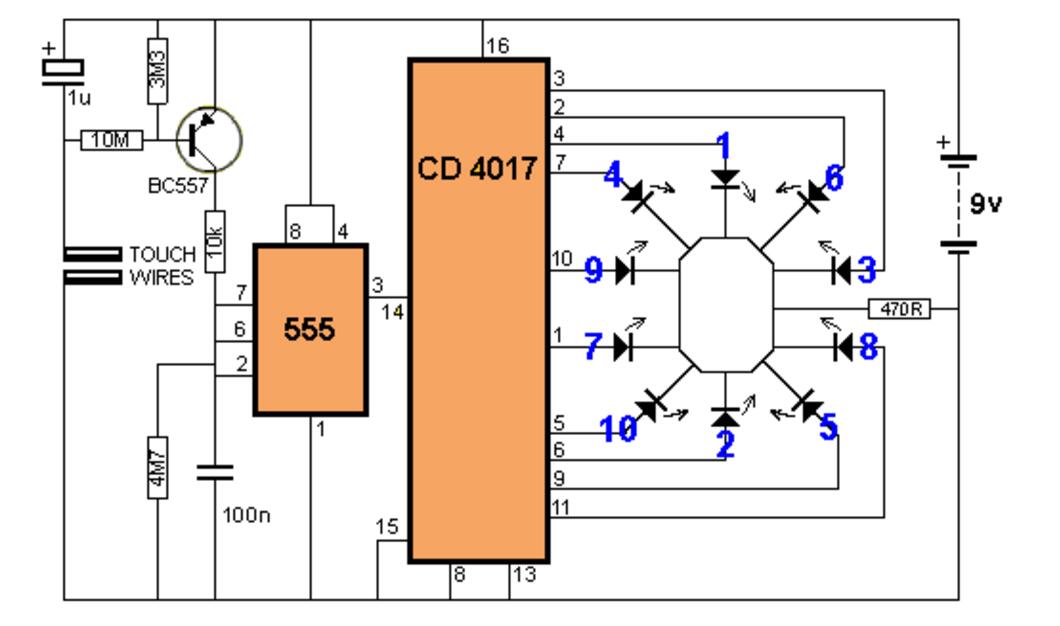

cd4017計(jì)數(shù)器電路圖(三款cd4017計(jì)數(shù)器電路)

本文開始對CD4017功能與CD4017邏輯結(jié)構(gòu)圖進(jìn)行了介紹,其次分別介紹了用CD4017和選擇開關(guān)組成多進(jìn)制計(jì)數(shù)器、CD4017組成的1/n計(jì)數(shù)器電路與用CD4017組成1~17進(jìn)制計(jì)數(shù)器電路圖。

2018-01-31 13:58:06 22819

22819

22819

22819

cd4017流水燈電路圖(六款cd4017流水燈電路介紹)

CD4017是目前廣泛使用的一種十進(jìn)制計(jì)數(shù)器/脈沖分配器。本文主要介紹了六款用cd4017制作流水燈電路概況。

2018-01-31 11:08:34 109235

109235

109235

109235

74ls290計(jì)數(shù)器電路大全(六種進(jìn)制計(jì)數(shù)器電路)

74ls290是一個二,五,十進(jìn)制計(jì)數(shù)器,本文為大家介紹由74ls290構(gòu)成的各種進(jìn)制計(jì)數(shù)器的電路。

2018-01-26 09:26:11 106188

106188

106188

106188

74ls290構(gòu)成31進(jìn)制計(jì)數(shù)器電路圖文詳解

74LS290為異步二-五-十進(jìn)制加法計(jì)數(shù)器。本文為大家介紹74ls290構(gòu)成31進(jìn)制計(jì)數(shù)器電路。

2018-01-25 14:36:39 16924

16924

16924

16924

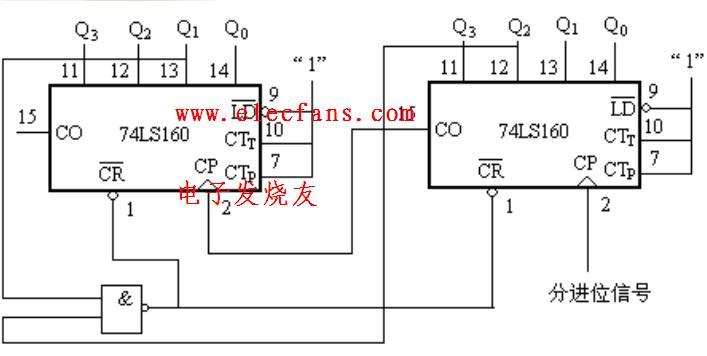

74ls160構(gòu)成24進(jìn)制計(jì)數(shù)器

本文主要介紹了74ls160構(gòu)成24進(jìn)制計(jì)數(shù)器電路設(shè)計(jì)。本設(shè)計(jì)采用異步清零。由兩片十進(jìn)制同步加法計(jì)數(shù)器74LS160和一片與非門74LS00以及相應(yīng)的電阻開關(guān)組成。由外加送來的計(jì)數(shù)脈沖送入兩個計(jì)數(shù)器

2018-01-18 15:43:05 145644

145644

145644

145644

74ls160十進(jìn)制計(jì)數(shù)器

本文主要介紹了74ls160十進(jìn)制計(jì)數(shù)器電路的設(shè)計(jì)與實(shí)現(xiàn)。74LS160是二~十進(jìn)制同步可預(yù)置計(jì)數(shù)器,1腳Cr為清零端,低電平有效.2腳CP為時(shí)鐘脈沖輸人端,上升沿觸發(fā).3~6V腳D1一D4為數(shù)據(jù)

2018-01-18 15:14:45 182091

182091

182091

182091

74LS161集成計(jì)數(shù)器電路(2、3、4、6、8、10、60進(jìn)制計(jì)數(shù)器)

本文主要介紹了74LS161集成計(jì)數(shù)器電路(2、3、4、6、8、10、60進(jìn)制計(jì)數(shù)器)。74LS161是4位二進(jìn)制同步計(jì)數(shù)器,該計(jì)數(shù)器能同步并行預(yù)置數(shù)據(jù),具有清零置數(shù),計(jì)數(shù)和保持功能,具有進(jìn)位輸出端

2018-01-18 10:56:39 324594

324594

324594

324594

7進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案匯總(三種模擬電路設(shè)計(jì)過程詳細(xì))

本文為大家介紹三種7進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案。

2018-01-17 16:57:33 52835

52835

52835

52835

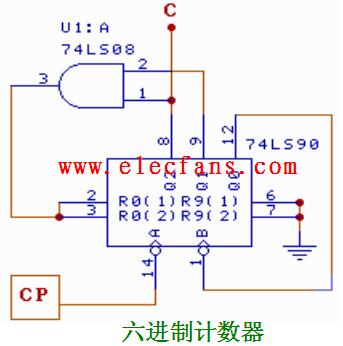

6進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案匯總(三款模擬電路原理圖分享)

本文為大家分享三種6進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案。

2018-01-17 16:18:56 60706

60706

60706

60706

5進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案匯總(三款計(jì)數(shù)器的電路原理圖)

本文為大家?guī)?b style="color: red">三種5進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案。

2018-01-17 15:51:48 56298

56298

56298

56298

20進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案匯總(三款仿真電路設(shè)計(jì)原理詳細(xì))

本文為大家介紹三個20進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案。

2018-01-17 14:16:19 10234

10234

10234

10234

74ls161制作24進(jìn)制計(jì)數(shù)器設(shè)計(jì)

74ls161為二進(jìn)制同步計(jì)數(shù)器,具有同步預(yù)置數(shù)、異步清零以及保持等功能。兩片74ls161可設(shè)計(jì)一個24進(jìn)制計(jì)數(shù)器。

2018-01-16 15:30:46 110315

110315

110315

110315

74ls90設(shè)計(jì)60進(jìn)制計(jì)數(shù)器

60進(jìn)制計(jì)數(shù)器,由于24進(jìn)制、60進(jìn)制計(jì)數(shù)器均由集成計(jì)數(shù)器級聯(lián)構(gòu)成,且都包含有基本的十進(jìn)制計(jì)數(shù)器,從設(shè)計(jì)簡便考慮,芯片選擇同步十進(jìn)制計(jì)數(shù)器

2017-12-22 13:55:48 148134

148134

148134

148134

74ls160設(shè)計(jì)60進(jìn)制計(jì)數(shù)器

計(jì)數(shù)器是一個用以實(shí)現(xiàn)計(jì)數(shù)功能的時(shí)序部件,本設(shè)計(jì)主要設(shè)備是兩個74LS160同步十進(jìn)制計(jì)數(shù)器,并且由200HZ,5V電源供給。作高位芯片與作低芯片位之間級聯(lián)。

2017-12-21 17:23:51 224996

224996

224996

224996

基于74LS160的N進(jìn)制計(jì)數(shù)器仿真設(shè)計(jì)

針對任意進(jìn)制(N進(jìn)制)計(jì)數(shù)器的設(shè)計(jì)目的,采用反饋復(fù)零法對基于同步十進(jìn)制計(jì)數(shù)器7415160進(jìn)行設(shè)計(jì),分別采用異步清零法實(shí)現(xiàn)了6進(jìn)制計(jì)數(shù)器和同步置數(shù)法實(shí)現(xiàn)7進(jìn)制計(jì)數(shù)器的設(shè)計(jì),通過應(yīng)用EWB軟件對所設(shè)

2017-12-21 17:08:37 60783

60783

60783

60783

基于74LS192的任意進(jìn)制計(jì)數(shù)器的設(shè)計(jì)

本文為大家介紹基于74LS192的任意進(jìn)制計(jì)數(shù)器的設(shè)計(jì)。

2017-12-21 12:00:28 92329

92329

92329

92329

24進(jìn)制計(jì)數(shù)器的設(shè)計(jì)

集成計(jì)數(shù)器常見的是多位二進(jìn)制計(jì)數(shù)器及十進(jìn)制計(jì)數(shù)器,當(dāng)需要實(shí)現(xiàn)其它進(jìn)制計(jì)數(shù)器時(shí),通常利用現(xiàn)有的集成計(jì)數(shù)器進(jìn)行適當(dāng)?shù)倪B接而構(gòu)成。對于當(dāng)設(shè)計(jì)要求沒有限定計(jì)數(shù)器的狀態(tài)編碼時(shí)電路設(shè)計(jì)的靈活性問題已有文獻(xiàn)進(jìn)行

2017-11-09 16:36:16 81

81

81

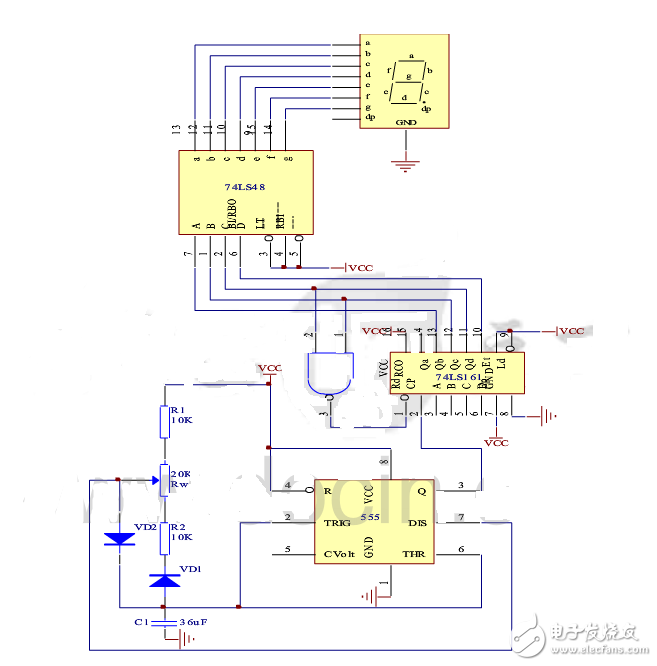

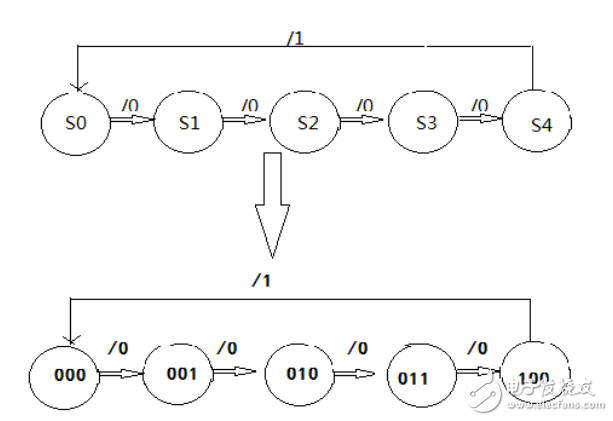

81基于555定時(shí)器和Johnson計(jì)數(shù)器的CD4017十路流水燈電路的設(shè)計(jì)與制作

一、電路設(shè)計(jì)功能介紹 該電路主要由555構(gòu)成的多諧振蕩器產(chǎn)生脈沖提供給由4017組成的十進(jìn)制移位計(jì)數(shù)器,進(jìn)而控制十路LED燈,通電后,LED燈從上往下逐個點(diǎn)亮,直到第十個LED燈,循環(huán)往復(fù),且移動

2017-09-07 16:29:15 58

58

58

58十進(jìn)制計(jì)數(shù)器/分頻器

約翰遜MC14017B是五級十進(jìn)制計(jì)數(shù)器內(nèi)置代碼轉(zhuǎn)換器。 高速運(yùn)行和約翰遜spike-free輸出是通過使用十進(jìn)制計(jì)數(shù)器的設(shè)計(jì)。 十個解碼輸出通常是低,只在適當(dāng)?shù)氖?b style="color: red">進(jìn)制時(shí)間走高。 輸出的正向變化的時(shí)鐘脈沖。 這部分可用于分頻應(yīng)用程序以及十進(jìn)制計(jì)數(shù)器或十進(jìn)制譯碼顯示應(yīng)用程序。

2017-04-06 09:03:48 28

28

28

28基于Proteus的任意進(jìn)制計(jì)數(shù)器設(shè)計(jì)與仿真

提出一種基于Proteus 軟件的任意進(jìn)制計(jì)數(shù)器的設(shè)計(jì)。以74LS163 集成計(jì)數(shù)器為基礎(chǔ),用置數(shù)法設(shè)計(jì)了兩種48 進(jìn)制計(jì)數(shù)器,采用Proteus 軟件對計(jì)數(shù)器進(jìn)行仿真。結(jié)果表明,Proteus 軟件具有實(shí)現(xiàn)48 進(jìn)制計(jì)數(shù)器的功能。仿真圖像清晰,能快速準(zhǔn)確地驗(yàn)證設(shè)計(jì)結(jié)果。

2016-07-29 18:53:03 24

24

24

24集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)

集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)

2016-06-08 14:28:43 15

15

15

15EDA實(shí)驗(yàn)4-10進(jìn)制計(jì)數(shù)器

關(guān)于FPGA的資料,包括很多有用的東西,在EDA實(shí)驗(yàn)4-10進(jìn)制計(jì)數(shù)器。

2016-05-05 15:43:18 0

0

0

0二五十進(jìn)制計(jì)數(shù)器

數(shù)字電子技術(shù)--中規(guī)模集成計(jì)數(shù)器及其應(yīng)用--同步、異步二五十進(jìn)制計(jì)數(shù)器-PPT

2016-03-22 14:33:06 1

1

1

1基于Multisim的計(jì)數(shù)器設(shè)計(jì)仿真

計(jì)數(shù)器是常用的時(shí)序邏輯電路器件,文中介紹了以四位同步二進(jìn)制集成計(jì)數(shù)器74LS161和異步二-五-十模值計(jì)數(shù)器74LS290為主要芯片,設(shè)計(jì)實(shí)現(xiàn)了任意模值計(jì)數(shù)器電路,并用Multisim軟件進(jìn)行了

2013-07-26 11:38:41 133

133

133

133采用歸零法的N進(jìn)制計(jì)數(shù)器原理

計(jì)數(shù)器是一種重要的時(shí)序邏輯電路,廣泛應(yīng)用于各類數(shù)字系統(tǒng)中。介紹以集成計(jì)數(shù)器74LS161和74LS160為基礎(chǔ),用歸零法設(shè)計(jì)N進(jìn)制計(jì)數(shù)器的原理與步驟。用此方法設(shè)計(jì)了3種36進(jìn)制計(jì)數(shù)器,并

2012-03-20 10:21:38 95

95

95

95基于MSI的N進(jìn)制計(jì)數(shù)器設(shè)計(jì)方法

計(jì)數(shù)器是數(shù)字邏輯系統(tǒng)中的基本部件,它是數(shù)字系統(tǒng)中用得最多的時(shí)序邏輯電路,本文主要闡述了用中規(guī)模集成計(jì)數(shù)器設(shè)計(jì)任意進(jìn)制同步加法計(jì)數(shù)器的設(shè)計(jì)思想,并對設(shè)計(jì)方法和步驟作

2012-02-28 11:41:43 6157

6157

6157

6157

N進(jìn)制異步計(jì)數(shù)器設(shè)計(jì)方案

異步計(jì)數(shù)器電路是指其構(gòu)成的基本功能單元觸發(fā)器的時(shí)鐘輸入信號不是與觸發(fā)器在一起的,有的是外輸入的脈沖信號,有的是其他觸發(fā)器的輸出。本文給出了N進(jìn)制 異步計(jì)數(shù)器 設(shè)計(jì)方案

2011-10-24 15:39:38 3245

3245

3245

3245

數(shù)字集成電路實(shí)現(xiàn)流水燈設(shè)計(jì)

采用數(shù)字集成電路的控制方法,結(jié)合十進(jìn)制計(jì)數(shù)器/譯碼電路設(shè)計(jì)了該 流水燈 控制系統(tǒng)。該系統(tǒng)由電源、時(shí)鐘電路、計(jì)數(shù)器和譯碼顯示電路4部分組成。能實(shí)現(xiàn)任意方式的流水,只要改變

2011-09-27 15:05:04 28955

28955

28955

2895574LS161異步置零法構(gòu)成任意進(jìn)制計(jì)數(shù)器的Multisim仿真

介紹了集成4位二進(jìn)制計(jì)數(shù)器 74LS161 異步置零法構(gòu)成任意進(jìn)制計(jì)數(shù)器的 Multisim 仿真方案,即以波形方式顯示計(jì)數(shù)器的計(jì)數(shù)過程、過渡狀態(tài)形成異步置零信號的過程,用四蹤示波器以面板

2011-08-05 14:25:22 330

330

330

330基于可編程器件的任意進(jìn)制計(jì)數(shù)器的設(shè)計(jì)

采用可編程器件設(shè)計(jì)電路,利用MAX+plus II設(shè)計(jì)軟件中LPM元件庫所提供的lpm_counter元件,實(shí)現(xiàn)任意進(jìn)制計(jì)數(shù)器的設(shè)計(jì)。該計(jì)數(shù)器電路與結(jié)構(gòu)無關(guān),可編程器件的芯片利用率及效率達(dá)到最

2010-12-29 17:47:07 55

55

55

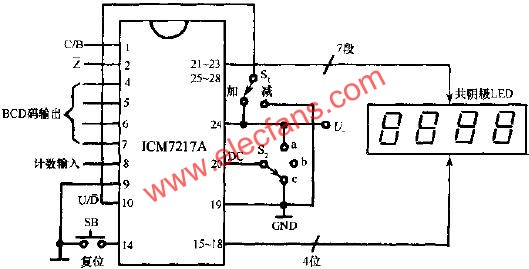

554位十進(jìn)制可逆計(jì)數(shù)器電路

使用一片ICM7217A配4只共陰極LED數(shù)碼管,可構(gòu)成4位十進(jìn)制可逆計(jì)數(shù)器,其

2010-12-10 13:55:24 6871

6871

6871

6871

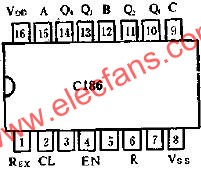

C186任意進(jìn)制串行計(jì)數(shù)器的應(yīng)用線路圖

C186是任意進(jìn)制串行計(jì)數(shù)器,所謂任意進(jìn)制,即在進(jìn)行計(jì)數(shù)或分頻時(shí),不需外加門電路,依靠本身管腳引出線的

2010-10-19 16:09:24 1361

1361

1361

1361

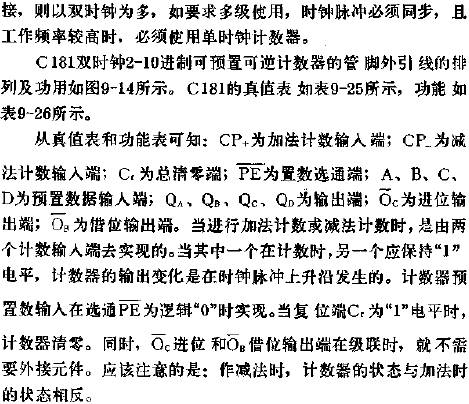

C181 2-10進(jìn)制可預(yù)置可逆計(jì)數(shù)器的應(yīng)用線路圖

C181是雙時(shí)鐘2-10進(jìn)制可預(yù)置可逆計(jì)數(shù)器.所謂雙時(shí)鐘是指計(jì)數(shù)器的加法計(jì)數(shù)時(shí)鐘和減法計(jì)數(shù)時(shí)鐘各有它自身的輸入

2010-10-19 15:16:06 814

814

814

814

十進(jìn)制計(jì)數(shù)器,十進(jìn)制計(jì)數(shù)器原理是什么?

十進(jìn)制計(jì)數(shù)器,十進(jìn)制計(jì)數(shù)器原理是什么?

二進(jìn)制計(jì)數(shù)器具有電路結(jié)構(gòu)簡單、運(yùn)算方便等特點(diǎn),但是日常生活中我們所接觸的大部分都是十進(jìn)制數(shù),特

2010-03-08 13:19:54 23684

23684

23684

23684什么是二進(jìn)制計(jì)數(shù)器,二進(jìn)制計(jì)數(shù)器原理是什么?

什么是二進(jìn)制計(jì)數(shù)器,二進(jìn)制計(jì)數(shù)器原理是什么?

計(jì)數(shù)器是數(shù)字系統(tǒng)中用得較多的基本邏輯器件。它不僅能記錄輸入時(shí)鐘脈沖的個數(shù),還可以實(shí)現(xiàn)

2010-03-08 13:16:34 29984

29984

29984

29984100進(jìn)制加減計(jì)數(shù)器的設(shè)計(jì)與制作

100進(jìn)制加減計(jì)數(shù)器的設(shè)計(jì)與制作:本電路結(jié)構(gòu)如圖袁主要由晶體振蕩電路,分頻電路,控制電路,計(jì)數(shù)電路,譯碼電路,數(shù)碼管顯示等幾部分構(gòu)成。

2009-10-22 21:50:19 228

228

228

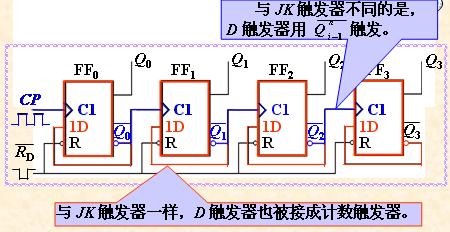

228同步二進(jìn)制計(jì)數(shù)器

同步二進(jìn)制計(jì)數(shù)器

1. 同步與異步二進(jìn)制加法計(jì)數(shù)器比較態(tài)序表和工作波形一樣電路結(jié)構(gòu)不同: 異步二進(jìn)制加法

2009-09-30 18:37:29 10744

10744

10744

10744

24進(jìn)制計(jì)數(shù)器電路

24進(jìn)制計(jì)數(shù)器電路

在百進(jìn)制基礎(chǔ)上,采用反饋歸零法即可組成二十四進(jìn)制計(jì)數(shù)器。計(jì)數(shù)范圍為0~23,24為過渡狀態(tài),當(dāng)高位計(jì)數(shù)至2、低位計(jì)數(shù)至4

2009-09-16 15:50:29 19522

19522

19522

19522

百進(jìn)制計(jì)數(shù)器電路

百進(jìn)制計(jì)數(shù)器電路

將兩塊74LS290進(jìn)行級聯(lián),組成的百進(jìn)制計(jì)數(shù)器如圖12.8所示。

2009-09-16 15:47:50 5541

5541

5541

5541

七進(jìn)制計(jì)數(shù)器電路

74LS290組成七進(jìn)制計(jì)數(shù)器?

解 首先,將74LS290的CP1端與Q0端相接,使

2009-09-16 15:46:35 8926

8926

8926

8926100進(jìn)制計(jì)數(shù)器

100進(jìn)制計(jì)數(shù)器一、 實(shí)驗(yàn)?zāi)康模?、 熟悉MAX+PLUS環(huán)境的基本操作。2、 掌握VHDL和原理圖的設(shè)計(jì)輸入方式。3、 設(shè)計(jì)100進(jìn)制計(jì)數(shù)器。二、&

2009-06-28 00:07:21 7414

7414

7414

7414第二十五講 同步計(jì)數(shù)器

第二十五講 同步計(jì)數(shù)器

7.3.2 同步計(jì)數(shù)器一、同步二進(jìn)制計(jì)數(shù)器1.同步二進(jìn)制加法計(jì)數(shù)器JK觸發(fā)器組成的4位同步二進(jìn)制加法

2009-03-30 16:28:45 7879

7879

7879

7879

74LS161構(gòu)成的五十(50)進(jìn)制計(jì)數(shù)器電路圖-原理圖

兩片4位二進(jìn)制數(shù)加法計(jì)數(shù)器74LS161級聯(lián)成五十進(jìn)制計(jì)數(shù)器。

2009-03-28 10:10:23 33045

33045

33045

33045

100進(jìn)制計(jì)數(shù)器

100進(jìn)制計(jì)數(shù)器

異步級聯(lián)法組成的100進(jìn)制計(jì)數(shù)器

定義集成計(jì)數(shù)器的高低位,1#芯片為低位(相當(dāng)

2008-07-05 14:25:17 5412

5412

5412

5412

256進(jìn)制計(jì)數(shù)器

我們可以采用具有保持功能的同步集成計(jì)數(shù)器(如74LS160)組成同步計(jì)數(shù)器,電路如圖3-4所示。在160計(jì)數(shù)器中當(dāng)S1=S2

2008-07-05 14:17:49 4236

4236

4236

4236

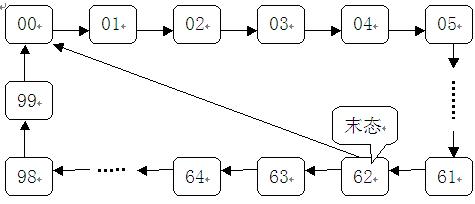

先級聯(lián)后預(yù)置數(shù)構(gòu)成的63進(jìn)制計(jì)數(shù)器

先級聯(lián)后預(yù)置數(shù)構(gòu)成的63進(jìn)制計(jì)數(shù)器:我們同樣也可以先用級聯(lián)法組成10i計(jì)數(shù)器、或16i計(jì)數(shù)器,再用預(yù)置

2008-07-05 13:58:00 1405

1405

1405

1405

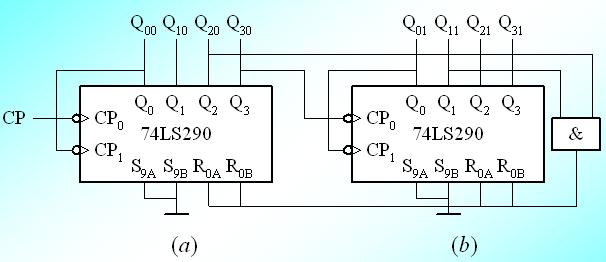

24進(jìn)制計(jì)數(shù)器

計(jì)數(shù)器級聯(lián)時(shí)的時(shí)鐘構(gòu)成方式可以采用同步時(shí)鐘,也可以采用異

2008-06-30 00:03:32 11061

11061

11061

11061

60進(jìn)制計(jì)數(shù)器

60進(jìn)制計(jì)數(shù)器,由于24進(jìn)制、60進(jìn)制計(jì)數(shù)器均由集成計(jì)數(shù)器級聯(lián)構(gòu)成,且都包含有基本的

2008-06-30 00:00:41 15300

15300

15300

15300

十進(jìn)制計(jì)數(shù)器工作原理

十進(jìn)制計(jì)數(shù)器工作原理

同二進(jìn)制計(jì)數(shù)器相比,十進(jìn)制計(jì)數(shù)器較為復(fù)雜。分析步驟一般是:

2008-01-21 13:15:22 27668

27668

27668

27668

計(jì)數(shù)器的級連使用

計(jì)數(shù)器的級連使用

一個十進(jìn)制計(jì)數(shù)器只能顯示0~9十個數(shù),為了擴(kuò)大計(jì)數(shù)器范圍,常用多個十進(jìn)制計(jì)數(shù)器級連使用。

2007-11-22 12:53:25 3143

3143

3143

3143

十進(jìn)制計(jì)數(shù)器

十進(jìn)制計(jì)數(shù)器

二進(jìn)制計(jì)數(shù)器具有電路結(jié)構(gòu)簡單、運(yùn)算方便等特點(diǎn),但是日常生活中我們所接觸的大部分都是十進(jìn)制數(shù),特別是當(dāng)二進(jìn)制數(shù)的位數(shù)較多時(shí),閱讀非常困難,還

2007-06-20 13:46:05 3559

3559

3559

3559 電子發(fā)燒友App

電子發(fā)燒友App

評論