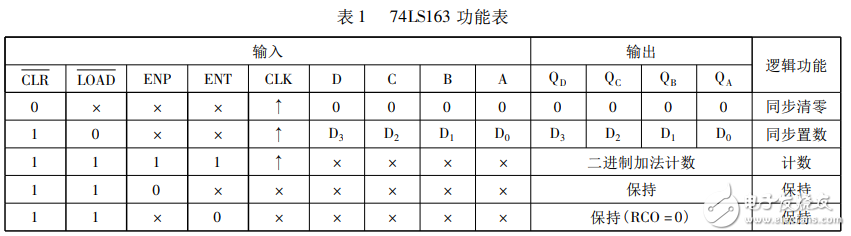

1、74LS163的功能及同步置數法

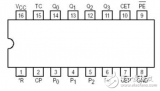

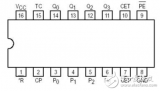

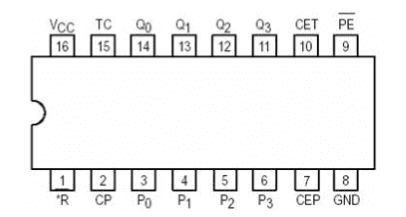

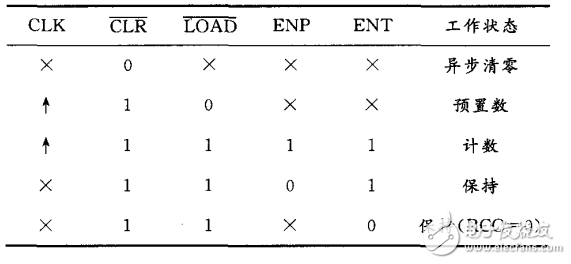

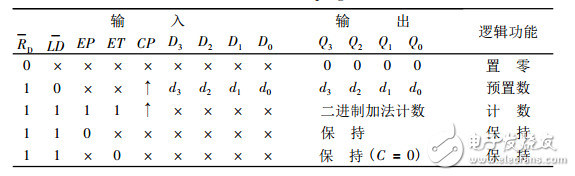

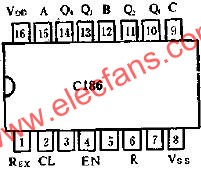

74LS163是集成4位二進制加法計數器,功能表如表1所示。其中CLK為時鐘脈沖輸入端、ENP及ENT為計數控制端、LOAD為同步預置數控制端、CLR為同步清零控制端、DCBA為預置數輸入端、QDQCQBQA為狀態輸出端、RCO為進位輸出端,芯片74IS163有從0000—111l共16個計數狀態。

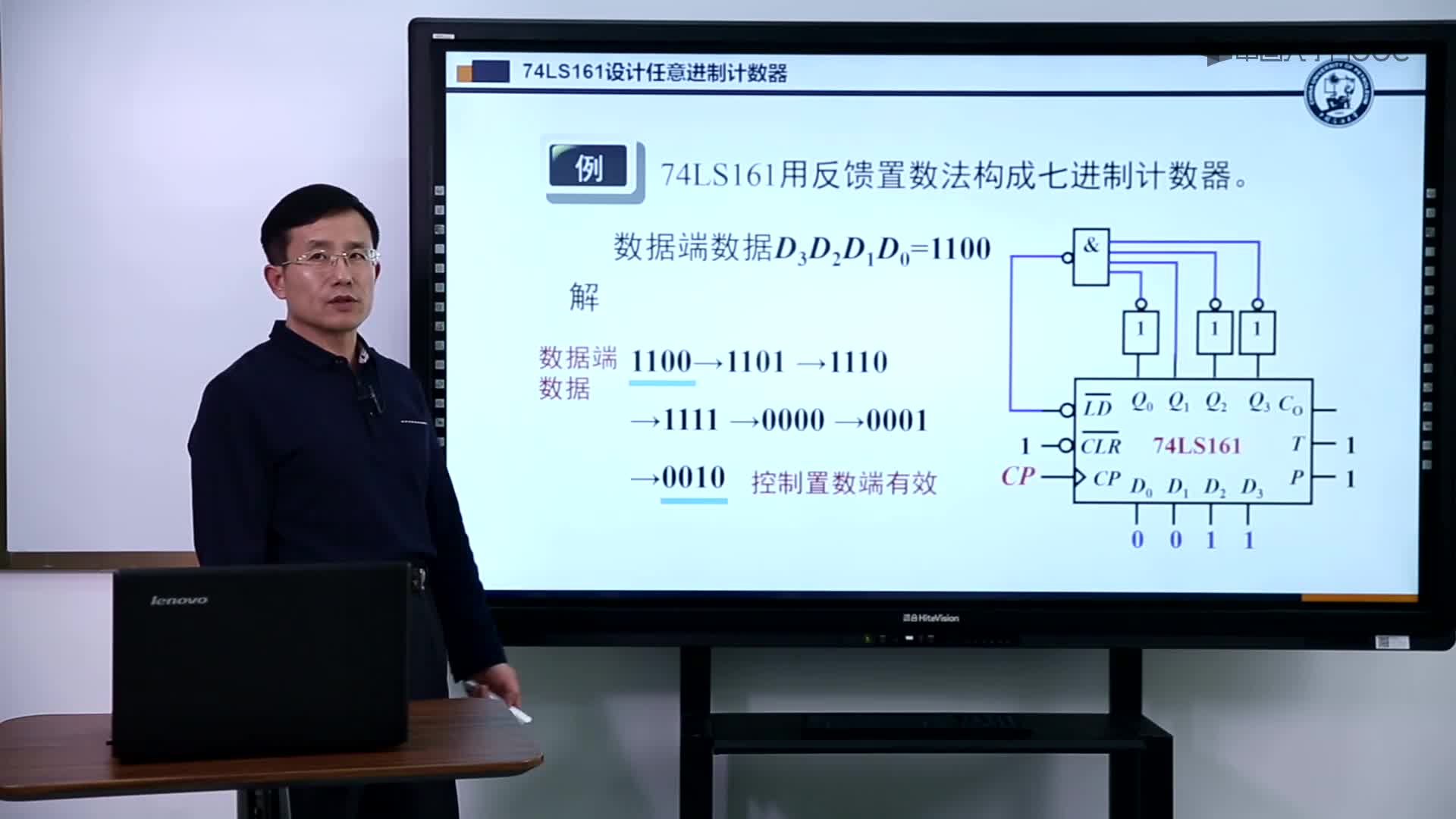

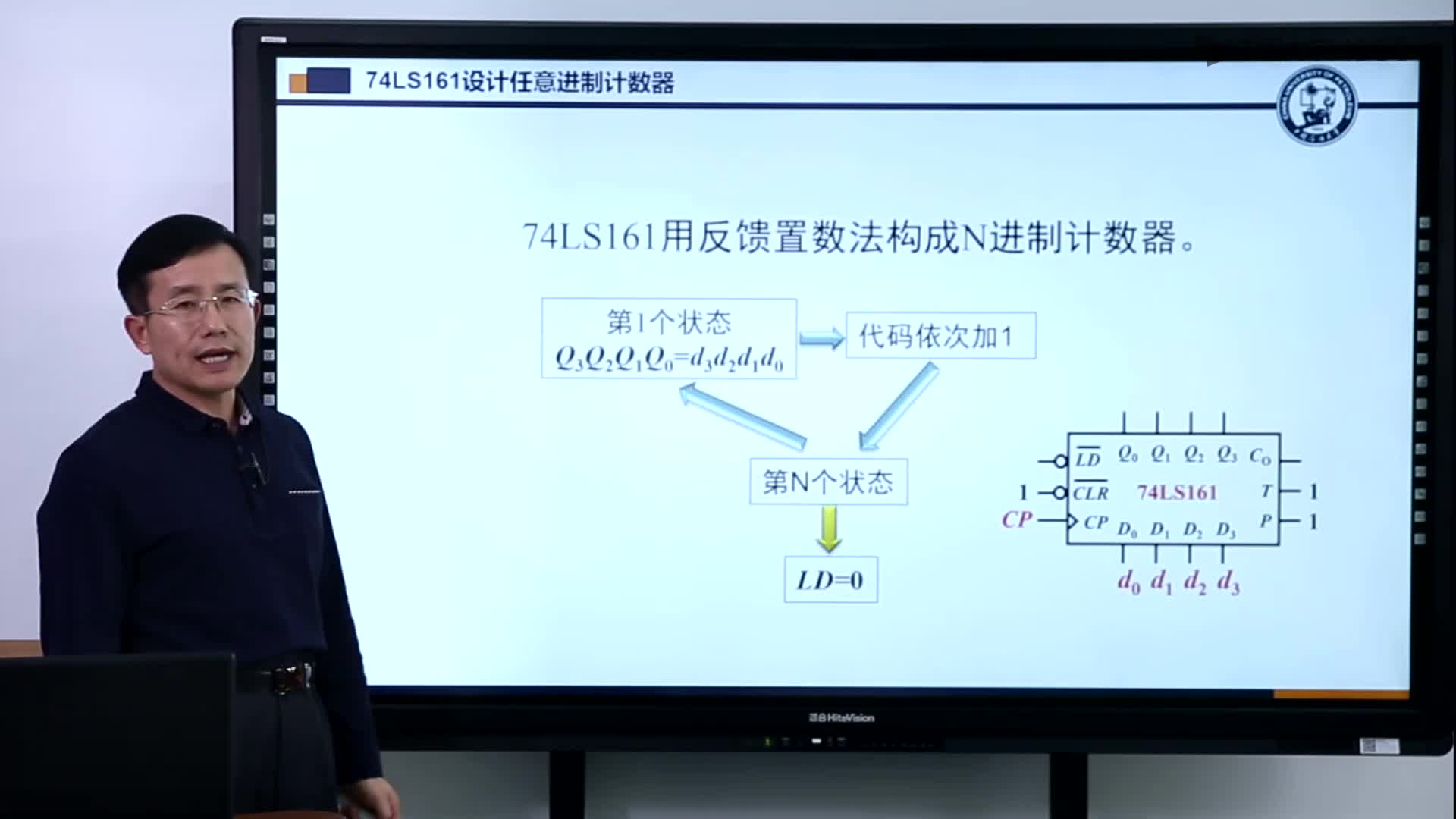

采用74LS163的同步預置數控制端或同步清零端構成進制計數器,方法是讓計數循環過程跳過SN以及后面的各個狀態,直接從SN-1狀態轉到全0狀態。基本方法有清零法和置數法。

用同步置數法將74LS163構成N進制計數器,使用計數和同步置數功能時,需要在狀態SN-1時給計數器的同步置數端發一個有效脈沖,使計數器在下一個計數脈沖到來時轉到全0狀態而非SN狀態。同時,按自然態序進行計數的N進制計數器的預置數端必須設置為零,按逆排序計數的N進制計數器和按任意排序計數的N進制計數器的預置數端必須設置為計數狀態中的最小數。

設計按自然態序進行計數的N進制計數器的步驟:

(1)寫出N進制狀態SN-1的二進制代碼。

(2)寫出SN-1狀態的譯碼PN-1。因為利用同步置數法構成的N進制加法計數器時,狀態SN—S2n-1不會出現,對應的最小項可作為隨意項處理,利用這些隨意項化簡后,狀態SN-1中代碼為0的各個觸發器的輸出Q可被消去,所以譯碼時只要將SN-1狀態中代碼為1的各個觸發器的輸出Q相乘即可。

(3)寫出置數邏輯表達式,即LD=PN-1。(4)74LS163其他輸入端的設置,ENP=ENT=1,CR=1,DCBA=0000。

2、利用74LS163同步置數法構成N進制計數器的不同方法

2.1、按自然態序計數的N進制計數器(取前N個狀態)

前面所介紹的構成N進制的方法,都是按自然態序計數的N進制計數器的設計方法。此處不再重述。

2.2、按逆排序計數的N進制計數器(取后N個狀態)

當取后N個狀態來構成N進制計數器時,因為需要計的最大數與所用計數器的最大計數相同,所以可用進位輸出信號RCO來控制置數控制端LOAD,這樣當計數器輸出最大數并產生進位信號后,置數控制端LOAD=0,在下一個CP脈沖到來時,計數器將執行置數功能,即通過數據輸入端DCBA置入需要計的最小數,于是在CP脈沖作用下,計數器又從最小數開始重新計數。

2.3、按任意排序計數的進制計數器(取中間N個狀態)

當取中間N個狀態來構成N進制計數器,可利用與非門檢測需要計的最大數。當最大數出現時,與非門輸出低電平,使置數控制端LOAD=0,在下一個CP脈沖到來時,計數器將執行置數功能,即通過數據輸入端DCBA置入需要計的最小數,于是在CP脈沖作用下,計數器又從最小數開始重新計數。

3、同步置位法Multisim仿真設計

用 Multisiml0 版本構成 9 進制計數器為例,說明 Multisim 仿真設計。

3.1、按自然態序計數的9進制計數器仿真設計

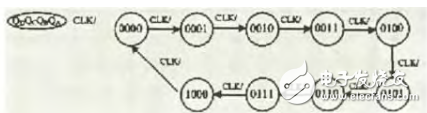

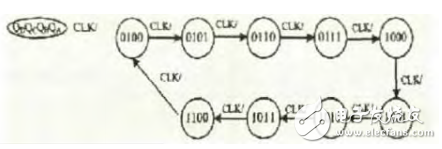

(1)按自然態序計數的9進制計數器狀態圖

同步置位法構成9進制計數器的狀態圖如圖1所示,其中0000—1000共9個狀態為正常的計數狀態,作用9個時鐘脈沖完成一個計數周期的循環。

圖1自然態序計數9進制計數器狀態圖

(2)按自然態序計數的9進制計數器設計步驟

1)確定SN-1的二進制代碼為:SN-1=S9-1=S8=1000

2)確定SN-1狀態的譯碼PN-1為:PN-1=P9-1=P8=QD

3)寫出置數邏輯表達式,即LD=PN-1=QD

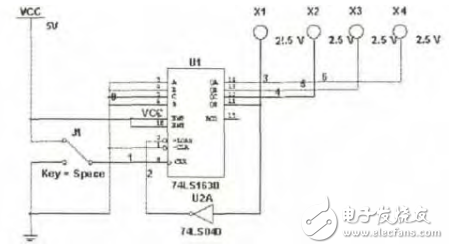

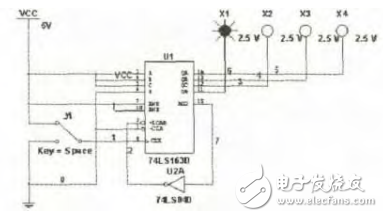

4)構建仿真電路

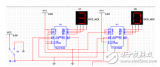

構建的仿真電路如圖2所示。其中脈沖信號選擇由雙向開關構成的手動脈沖信號,以便實驗中更好地觀察每個時鐘作用后計數器的狀態變化情況。在Multisim中,集成4位二進制計數器74LS163的時鐘脈沖觸發方式為CLK為下降沿觸發與實際器件不附(實際器件為上升沿觸發方式),仿真實驗時應進行說明。顯示器件使用不同顏色的探針,更加直觀地顯示了實驗效果。

圖2自然態序計數9進制計數器仿真電路

(3)仿真結果分析在圖2中,探針X1、X2、X3、X4分別顯示輸出端QD、QC、QB、QA電平,當輸出為1(高電平)時探針發光,為0(低電平)時探針不發光。

當第一個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=0001;當第二個CLK脈沖信號下降沿到來后計數器狀態為QDQCQBQA=0010;當第三個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=0011;當第四個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=0100;當第五個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=0101;當第六個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=0110;當第七個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=0111;當第八個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=1000,此時,LOAD=0但并沒有進行同步置位;當第九個脈沖信號CLK下降沿到來時,進行同步置數,將數據輸入端DCBA=0000送入計數器,使計數器狀態為QDQCQBQA=0000。經過9個時鐘脈沖信號作用后完成一個計數周期的循環,仿真實驗結果和圖1所示狀態圖的要求一致。

3.2、按逆排序計數的9進制計數器(取后9個狀態)

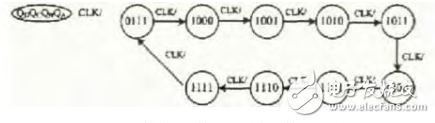

(1)按逆排序計數的9進制計數器的狀態圖

同步置位法構成9進制計數器的狀態圖如圖3所示,其中0111—1111共9個狀態為正常的計數狀態,作用9個時鐘脈沖完成一個計數周期的循環。

圖3按逆排序計數9進制計數器狀態圖

(2)按逆排序計數的9進制計數器設計步驟

當取后9個狀態來構成9進制計數器時,因為需要計的最大數與所用計數器的最大計數相同,因此可確定SN-1狀態中最小狀態的最小數的數據輸入端的輸入數據為:DCBA=0111,置數邏輯表達式為LD=RCO。

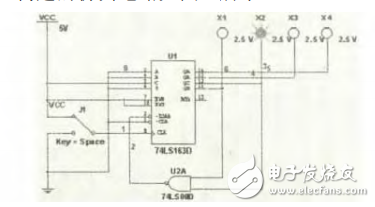

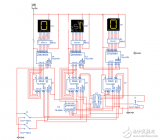

(3)構建仿真電路

構建的仿真電路如圖4所示。

圖4按逆排序計數9進制計數器仿真電路

(4)仿真結果分析

在圖4中,探針X1、X2、X3、X4分別顯示輸出端QD、QC、QB、QA電平,當輸出為1(高電平)時探針發光,為0(低電平)時探針不發光。

當第一個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=1000;當第二個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=1001;當第八個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=1111,此時進位端RCO=1產生進位,LOAD=RCO=0,但并沒有進行同步置位;當第九個脈沖信號CLK下降沿到來時,進行同步置數,將數據輸入端DCBA=0111送入計數器,使計數器狀態為QDQCQBQA=0111。經過9個時鐘脈沖信號作用后完成一個計數周期的循環,仿真實驗結果和圖3所示狀態圖的要求一致。

3.3、按任意排序計數的9進制計數器(取中間9個狀態)

(1)按任意排序計數的9進制計數器狀態圖

同步置位法構成9進制計數器的狀態圖如圖5所示,其中0100—1100共9個狀態為正常的計數狀態,作用9個時鐘脈沖完成一個計數周期的循環。

圖5按任意排序計數9進制計數器狀態圖

(2)按任意排序計數的進制計數器設計步驟

當取中間9個狀態來構成9進制計數器,可利用與非門檢測需要計的最大數。當最大數出現時,與非門輸出低電平,使置數控制端LOAD=0,即LOAD=QDQC。通過數據輸入端DCBA置入需要計的最小數,即DCBA=0100。

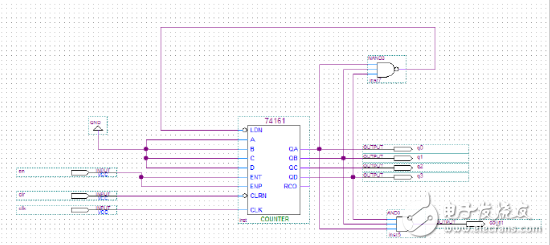

(3)構建仿真電路

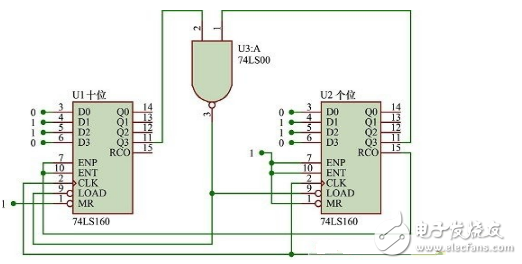

構建的仿真電路如圖6所示。

圖6按任意排序計數9進制計數器仿真電路

(4)仿真結果分析

在圖6中,探針X1、X2、X3、X4分別顯示輸出端QD、QC、QB、QA電平,當輸出為1(高電平)時探針發光,為0(低電平)時探針不發光。

當第一個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=0101;當第二個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=0110;當第八個脈沖信號CLK下降沿到來后計數器狀態為QDQCQBQA=1100,此時LOAD=QDQC=0,但并沒有進行同步置位;當第九個脈沖信號CLK下降沿到來時,進行同步置數,將數據輸入端DCBA=0100送入計數器,使計數器狀態為QDQCQBQA=0100。經過9個時鐘脈沖信號作用后完成一個計數周期的循環,仿真實驗結果和圖5所示狀態圖的要求一致。

電子發燒友App

電子發燒友App

評論