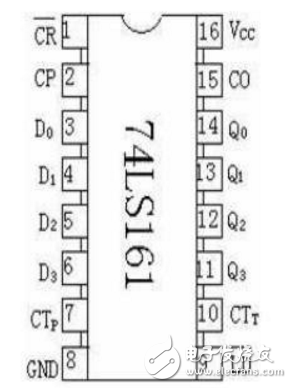

2.2、字組產生器輸出字組的設計

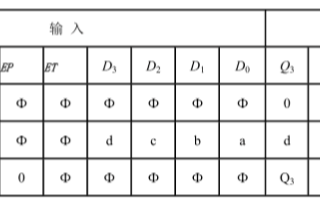

所設計的各字數據為0,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,如圖2所示。

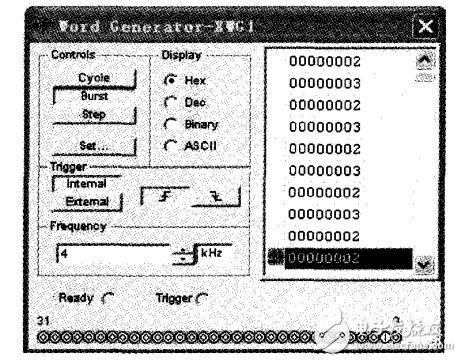

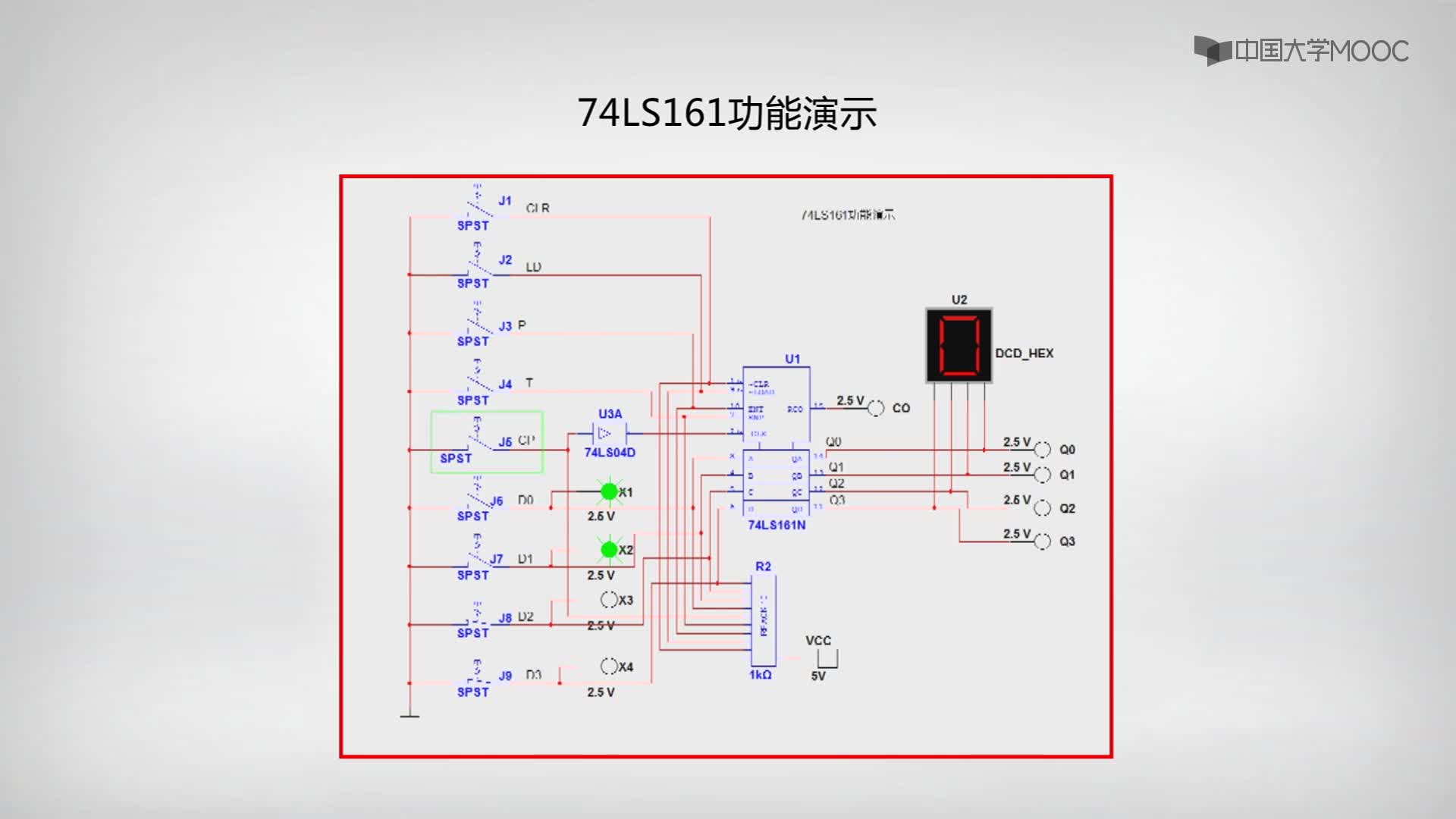

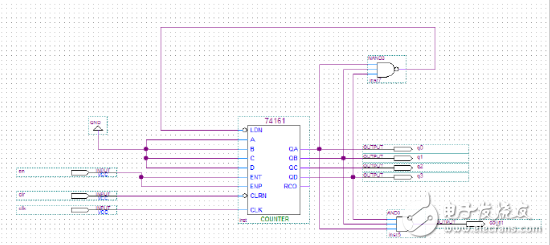

在字組產生器的數據欄內以十六進制(Hex)依次輸入各字組數據,并對最后一個字數據進行末地址設置(SetFinalPosition),完成所有字組信號的設置,如圖3所示。

圖3 ?集成計數器74LS161仿真實驗字組信號的設置

2.3、仿真運行分析

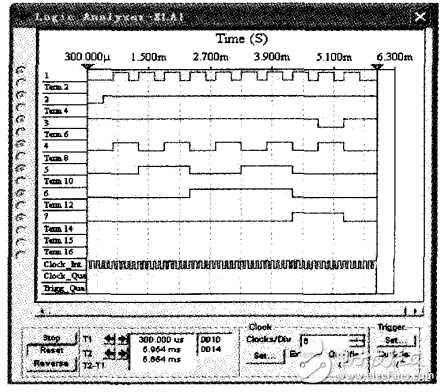

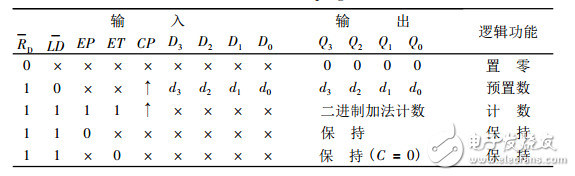

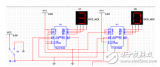

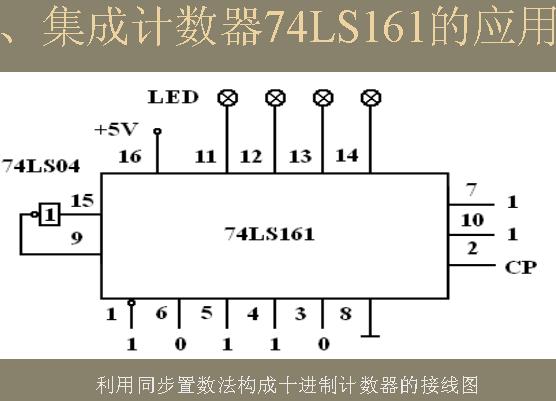

邏輯儀分析顯示波形如圖4所示。

圖4 ? 集成計數器74LS161仿真實驗波形

圖4中,“1”為時鐘脈沖/CLK的波形;“2”為異步置0信號/CLR的波形;“3”為預置數控制信號/LOAD的波形;“4”~“7”為狀態輸出信號QA~QD的波形。

由圖4可知,/CLR一0時將計數器置于0000初始狀態;/CLR=1時,從0000~1001狀態,預置數控制信號/LOAD=1,計數器在時鐘脈沖/CLK作用下按計數方式工作;在1001狀態預置數控制信號/LOAD一0,計數器在時鐘脈沖/CLK作用下按預置數方式工作,使QAQBQcQD—ABCD一0000。

3、結語

由于受實驗儀器的限制無法對計數器工作波形進行硬件實驗驗證,主要是,現有的信號發生器不能產生多路同步信號,現有的示波器多為雙蹤示波器無法同時觀測多路波形,用Multisim軟件仿真解決了這一問題,所述方法具有實際應用意義。

電子發燒友App

電子發燒友App

評論