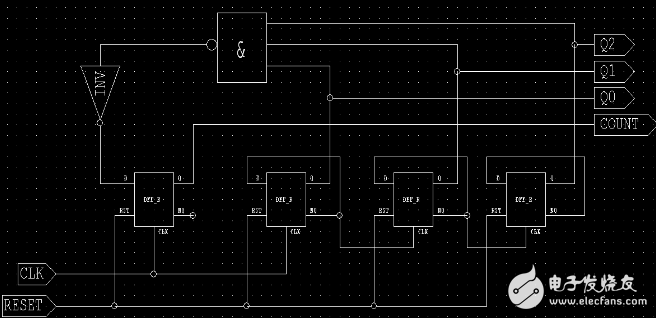

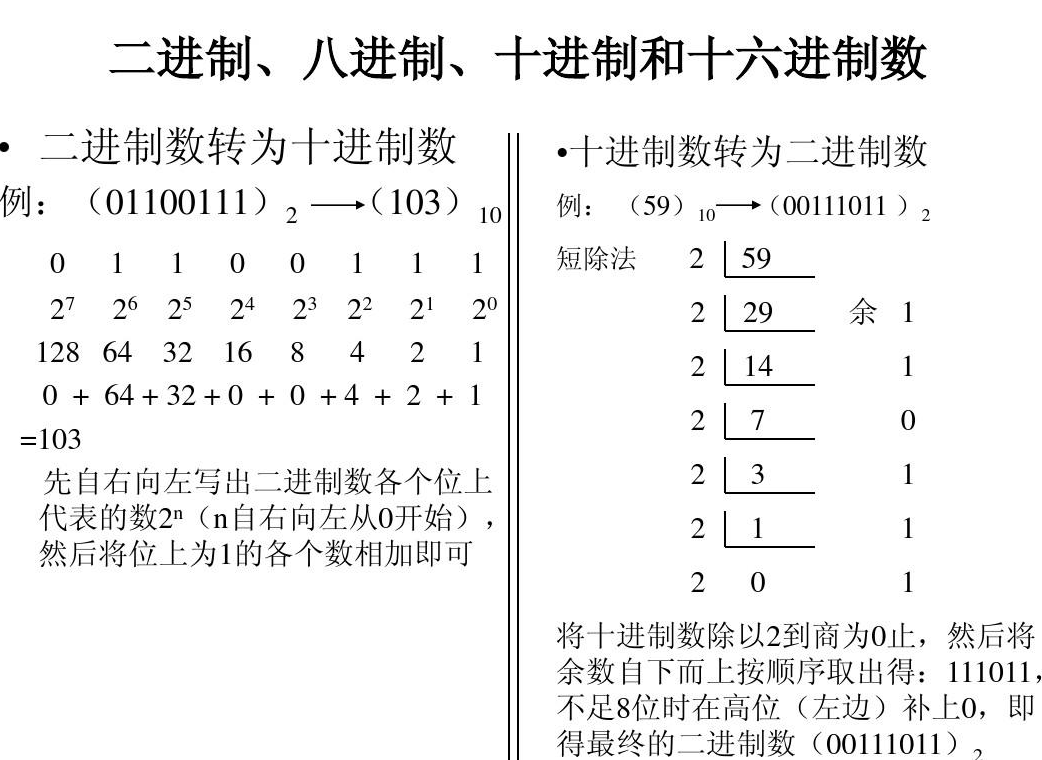

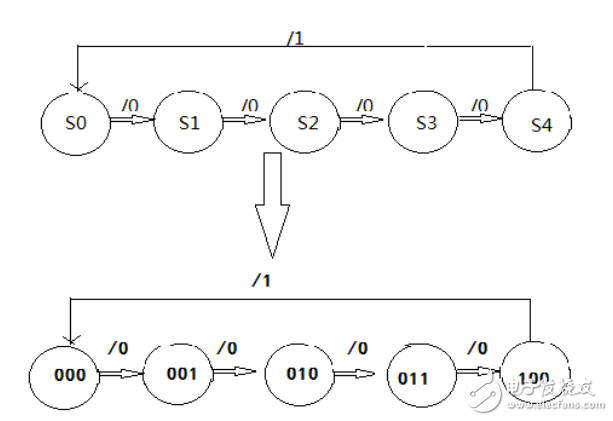

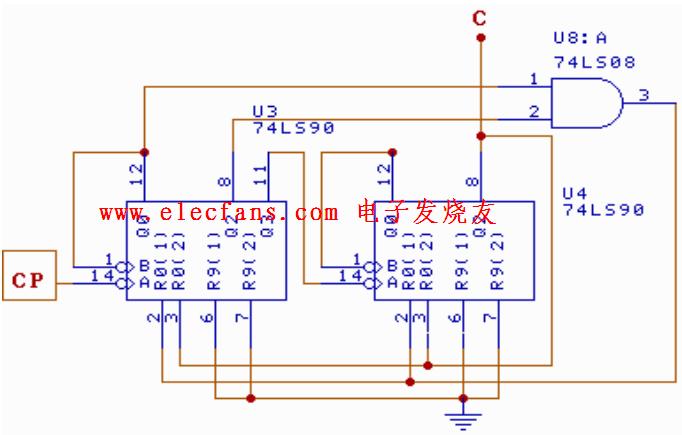

異步八進制計數器邏輯圖

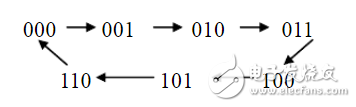

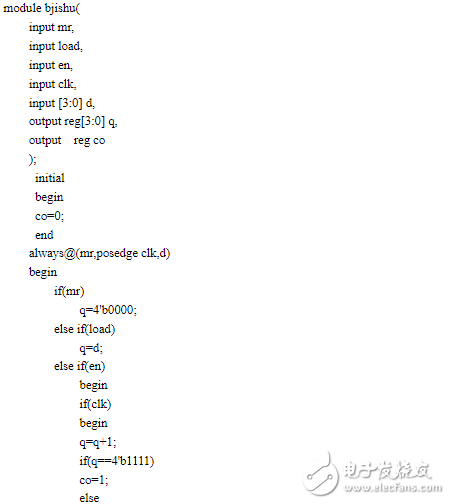

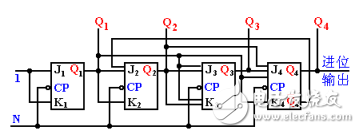

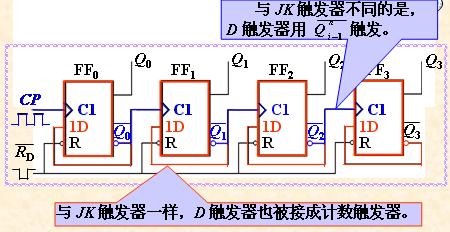

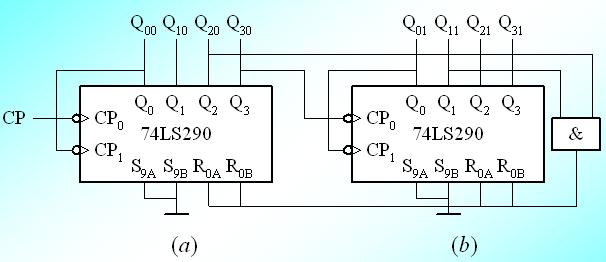

據方程得知我們所用的D觸發器的連接方式,其中根據D2D1D0可知道本電路需要用到三個D觸發器,而且每個D觸發器的“非”輸出都接到自身的D輸入,時鐘脈沖除第一級時鐘接到時鐘輸入信號外其余的都接到前一級的“非”輸出。當計數到“111”后計數器進行進位,輸出C為“1”,而且此動作要與CP脈沖同步,則此功能使用三輸入與門和D觸發器來實現。

根據輸入輸出方程得出八進制加法計數器的邏輯圖如下圖所示。

邏輯圖端口描述:

輸入控制信號:RESET實現異步清零;

輸入時鐘信號:CLK輸出信號:Q0Q1Q2;

輸出進位端:count實現計數進位。

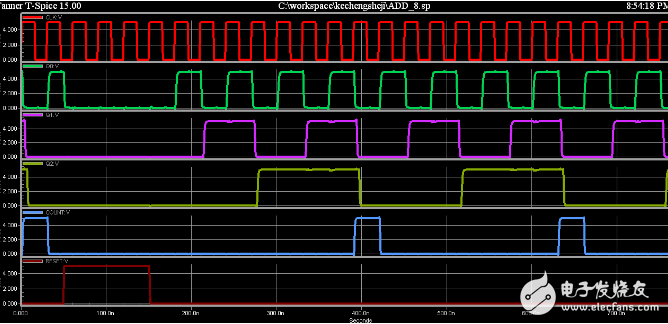

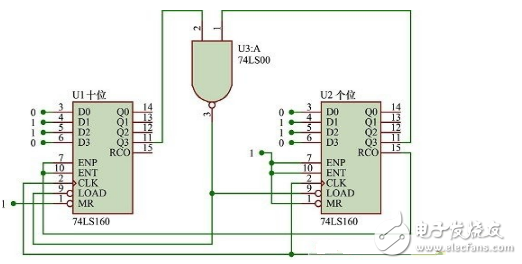

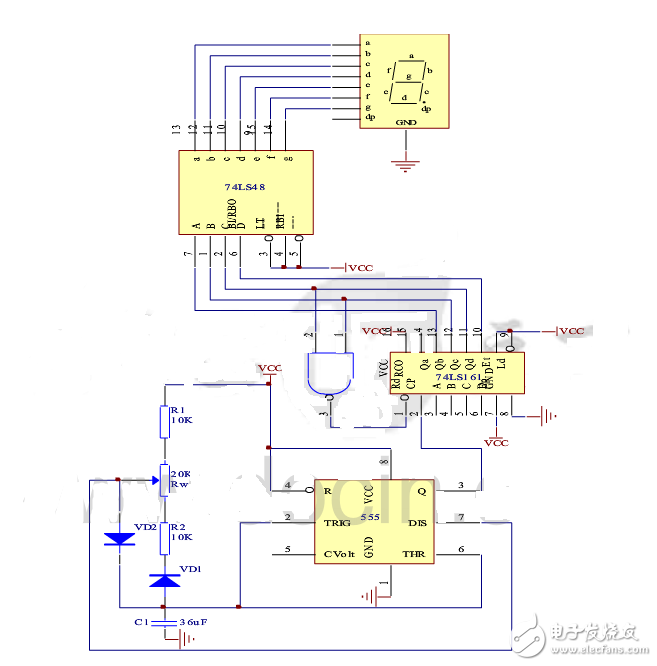

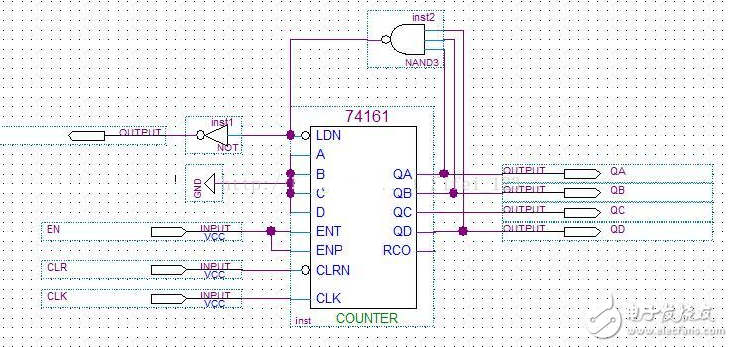

八進制計數器原理圖仿真

八進制計數器仿真波形

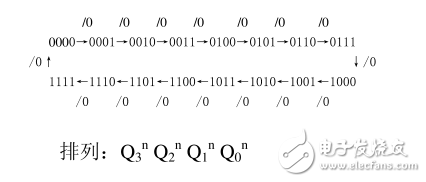

如上圖所示,當時鐘上升沿到來時,輸出信號歲時鐘由“000”開始計數一直計到“111”,且當“111”變為“000”時僅為信號輸出“1”。當清零端信號為高電平時不管時鐘沿是否到來輸出均為低電平。該結果符合設計目標。

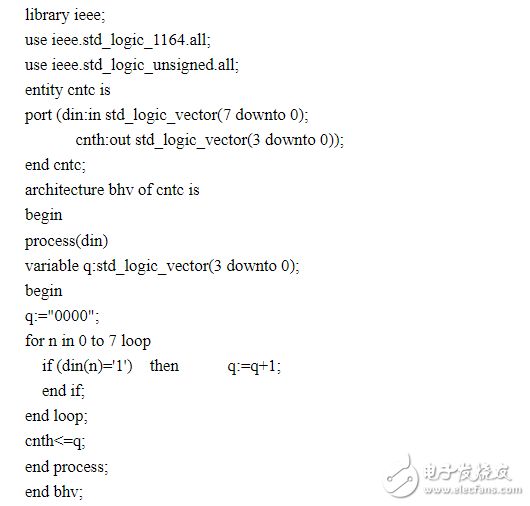

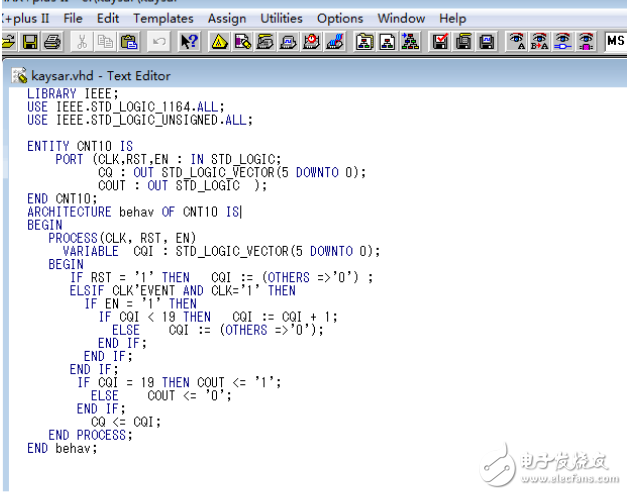

八進制計數器設計方案四:vhdl的八進制計數器的設計

電子發燒友App

電子發燒友App

評論