介紹一種通過SystemC做RTL/C/C++聯(lián)合仿真的方法

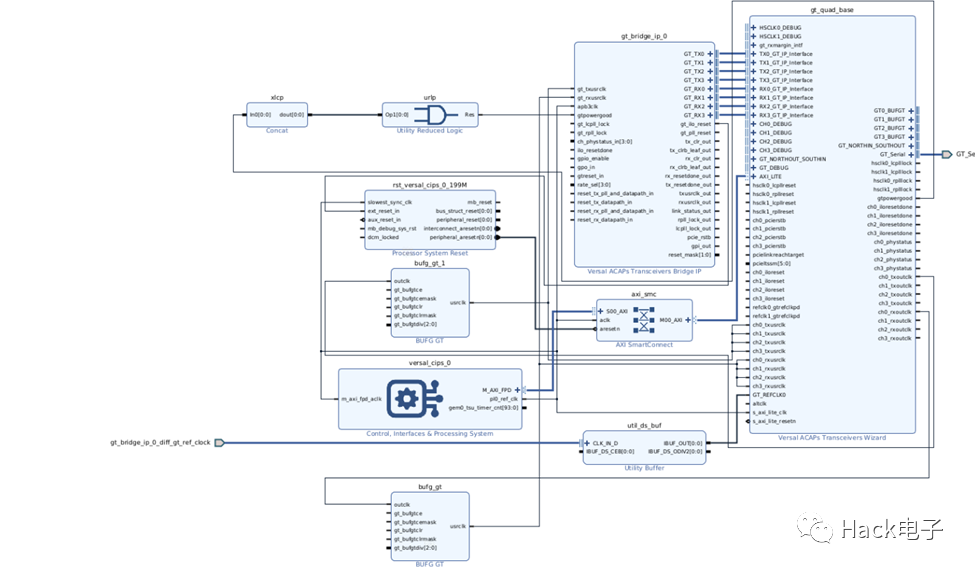

當(dāng)FPGA開發(fā)者需要做RTL和C/C++聯(lián)合仿真的時候,一些常用的方法包括使用MicroBlaze軟....

什么是2.5 Gb以太網(wǎng)?2.5 Gb以太網(wǎng)的優(yōu)點

自 20 世紀(jì) 70 年代誕生以來,以太網(wǎng)已成為局域網(wǎng)事實上的標(biāo)準(zhǔn)。多年來,其經(jīng)歷了多項進(jìn)步,以滿足....

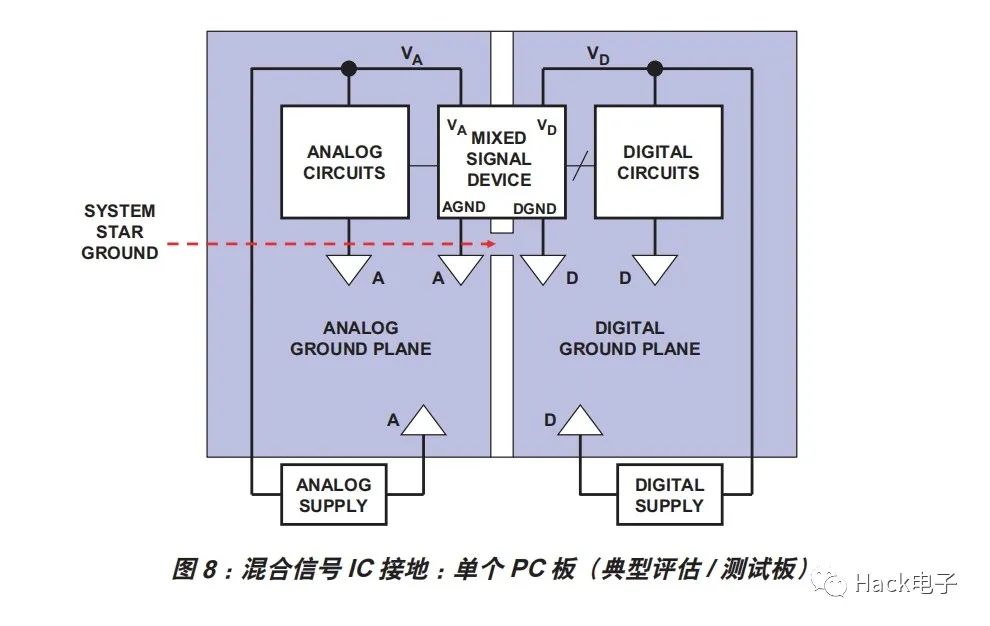

混合信號接地的困惑根源:對多卡系統(tǒng)應(yīng)用單卡接地概念

大多數(shù) ADC、DAC 和其他混合信號器件數(shù)據(jù)手冊是針對單個 PCB 討論接地,通常是制造商自己的評....

為什要區(qū)分AGND和DGND?雙面和多層印刷電路板

系統(tǒng)內(nèi)的每個 PCB 至少應(yīng)有完整的一層專用于接地層。理想情況下,雙面電路板的一面應(yīng)完全用于接地層,....

為什要區(qū)分AGND和DGND?搞清楚模數(shù)、數(shù)模轉(zhuǎn)換中的AGND和DGND

目前的信號處理系統(tǒng)一般需要混合信號器件,例如模數(shù)轉(zhuǎn)換器 (ADC)、數(shù)模轉(zhuǎn)換器 (DAC)和快速數(shù)字....

SoC(System on chip)與NoC(network-on-chip)

平均通信效率低。SoC中采用基于獨(dú)占機(jī)制的總線架構(gòu),其各個功能模塊只有在獲得總線控制權(quán)后才能和系統(tǒng)中....

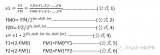

奇偶校驗器的設(shè)計方法和特點

奇偶校驗是一種簡單、實現(xiàn)代價小的檢錯方式,常用在數(shù)據(jù)傳輸過程中。對于一組并行傳輸?shù)臄?shù)據(jù)(通常為8比特....

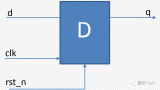

RTL設(shè)計規(guī)范有哪些?一個RTL用例設(shè)計介紹

D觸發(fā)器結(jié)構(gòu)如下圖所示,先有時鐘上升沿,然后才有D的值賦給Q,沒有上升沿Q值保持不變,時序邏輯在時鐘....

在Zynq裸機(jī)設(shè)計中使用視覺庫L1 remap函數(shù)的示例

本篇博文旨在演示如何在 Zynq 設(shè)計中使用 Vitis 視覺庫函數(shù) (remap) 作為 HLS ....

初識IBIS模型

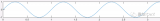

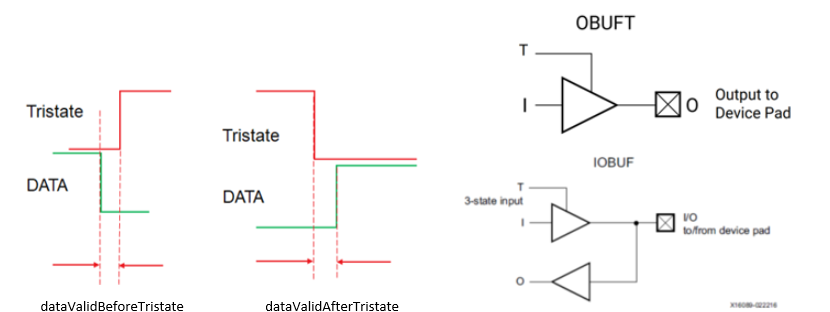

半導(dǎo)體LSI的EDA模型之一是"IBIS模型",完整稱為Input/OutputBuffer Inf....

調(diào)用HLS的FFT庫實現(xiàn)N點FFT

在HLS中用C語言實現(xiàn)8192點FFT,經(jīng)過測試,實驗結(jié)果正確,但是時序約束不到100M的時鐘,應(yīng)該....

從Xilinx FFT IP核到FPGA實現(xiàn)OFDM

筆者在校的科研任務(wù),需要用FPGA搭建OFDM通信系統(tǒng),而OFDM的核心即是IFFT和FFT運(yùn)算,因....

FPGA基于線性迭代法的除法器設(shè)計

FPGA實現(xiàn)除法的方法有幾種,比如直接用/來進(jìn)行除法運(yùn)算,調(diào)用IP核進(jìn)行除法運(yùn)算,但這兩種方式都有個....

AMD加大投資FPGA

AMD宣布計劃在四年內(nèi)投資高達(dá) 1.35 億美元,在愛爾蘭實現(xiàn)持續(xù)增長。

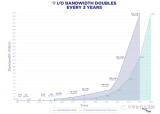

PCIe 7.0標(biāo)準(zhǔn)新進(jìn)展,速度達(dá)到16GB/秒/單通道

隨著PCI Express 6.0 于去年初完成,PCI-SIG 迅速開始著手開發(fā)下一代 PCIe ....

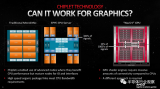

AMD帶領(lǐng)GPU進(jìn)入Chiplet時代 RDNA3架構(gòu)深入解讀

11月3日,AMD 透露了其 RDNA 3 GPU 架構(gòu)和 Radeon RX 7900 系列顯卡的....

System Verilog的概念以及與Verilog的對比

Verilog模塊之間的連接是通過模塊端口進(jìn)行的。 為了給組成設(shè)計的各個模塊定義端口,我們必須對期望....