AMD第二代Versal自適應(yīng)SoC的主要特色

AMD 第二代 AMD Versal AI Edge 和 Versal Prime 系列助力 AI ....

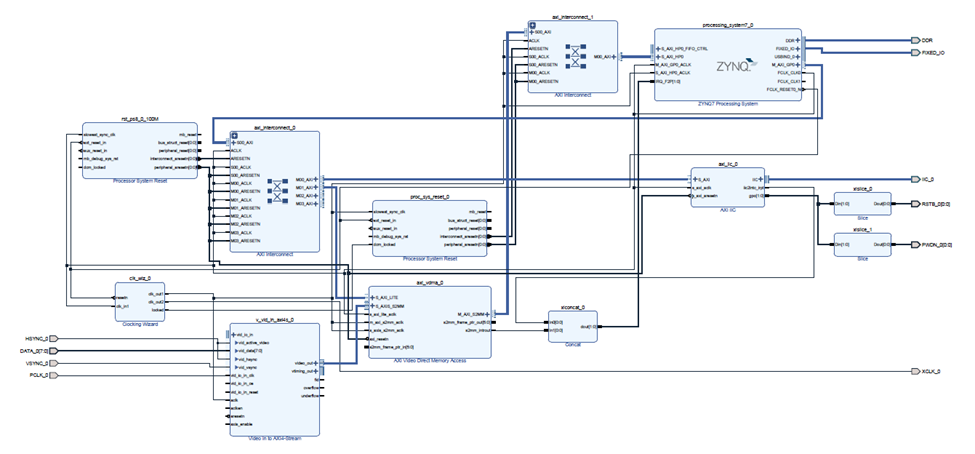

基于VDMA的遠(yuǎn)程圖像采集系統(tǒng)參考設(shè)計

本文參考設(shè)計基于 AMD ZYNQ 7000 Device, 使用 VDMA 做原始圖像采集系統(tǒng),在....

AMD Versal自適應(yīng)SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

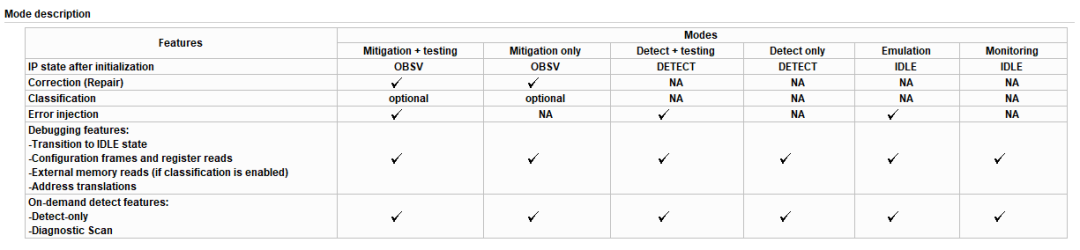

本文將從硬件設(shè)計和驅(qū)動使用兩個方面介紹基于 CPM5 QDMA 的 AMD Versal 自適應(yīng) S....

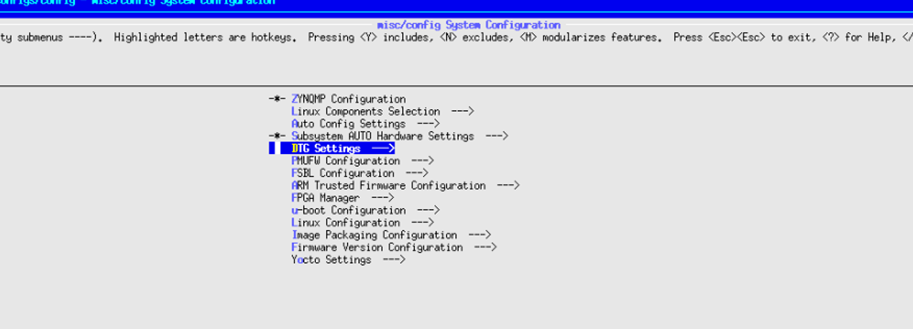

Multi-Scaler IP的Linux示例以及Debug(下)

設(shè)置好 2022.2 Petalinux 環(huán)境。使用 2022.2 ZCU06 BSP,創(chuàng)建 Pet....

AMD Vitis?設(shè)計工具中的Libraries新功能介紹

AMD Vitis? 2023.2 設(shè)計工具是 Vitis 設(shè)計工具變化較大的一個版本,設(shè)計流程和界....

AMD Versal? Adaptive SoC CPM PCIE PIO EP設(shè)計CED示例

本文可讓開發(fā)者們看懂 AMD Vivado Design Tool 2023.2 中的“AMD Ve....

在Windows 10上創(chuàng)建并運(yùn)行AMD Vitis?視覺庫示例

本篇文章將演示創(chuàng)建一個使用 AMD Vitis? 視覺庫的 Vitis HLS 組件的全過程。此處使....

NoC DDRMC LPDDR4上運(yùn)行AMD Versal? Adaptive SoC DCMAC設(shè)計示例

注釋:默認(rèn) DCMAC 設(shè)計示例不包含 NoC DDRMC

SWDT在AMD Versal? Adaptive SoC中的應(yīng)用案例分享

系統(tǒng)看門狗定時器(System WatchDog Timer)通常用于嵌入式系統(tǒng),可以有效的防止軟件....

第二代AMD Versal?器件助力AI驅(qū)動型嵌入式系統(tǒng)實現(xiàn)單芯片智能性

隨著嵌入式 AI、視頻和控制應(yīng)用取得爆發(fā)式增長,在嚴(yán)格的占板面積和功耗限制下,對于借助異構(gòu)處理能力加....

AMD Vitis? Embedded嵌入式軟件開發(fā)套件的功能和特性概述

Vitis Embedded 是一款獨(dú)立的嵌入式軟件開發(fā)套件,主要用于為 AMD 自適應(yīng) SoC 和....

全新AMD Spartan UltraScale+FPGA低成本系列解決方案

在構(gòu)建嵌入式應(yīng)用的過程中,硬件設(shè)計人員長期以來面臨著艱難的取舍,為推動產(chǎn)品快速上市,他們必須在成本、....

如何在下載Bitstream后自動觸發(fā)ILA采集

在硬件調(diào)試時,經(jīng)常需要用 ILA 采集一些 FPGA 內(nèi)部或者對外的初始化信號,然而在下載完 Bit....

AMD Vitis? Libraries Vision L3 Isppipeline U50流程示例

Vitis Vision 庫是一組 90 多個內(nèi)核,基于 OpenCV 計算機(jī)視覺庫,針對 AMD ....

AMD Vivado Design Suite 2023.2的優(yōu)勢

由于市場環(huán)境日益復(fù)雜、產(chǎn)品競爭日趨激烈,為了加快推出新型自適應(yīng) SoC 和 FPGA 設(shè)計,硬件設(shè)計....

使用PCIE更新AMD ZYNQ的QSPI Flash參考設(shè)計

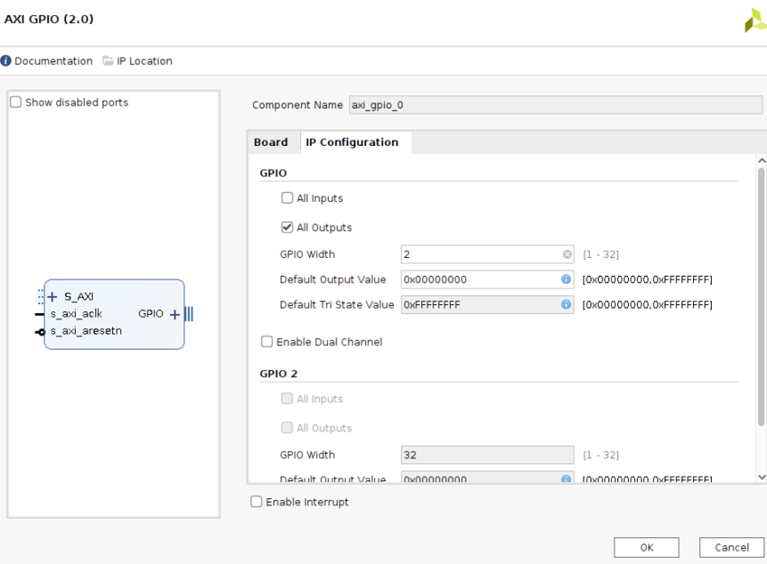

AMD ZYNQ 7000 的 S_AXI 端口提供了外設(shè)訪問 PS 內(nèi)部外設(shè)控制器的接口,這其中包....

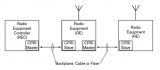

CPRI的數(shù)據(jù)幀結(jié)構(gòu)與初始化流程

CPRI 是無線通信里的一個標(biāo)準(zhǔn)協(xié)議,連接 REC 和 RE 的通信。AMD 有提供 CPRI IP....

為多個Vivado?工程復(fù)用遠(yuǎn)程IP高速緩存

在設(shè)計周期中,您可保留多個版本的工程,這些工程使用相同的 IP 和相同的配置。重新運(yùn)行整個工程會導(dǎo)致....