在Vivado中利用Report QoR Suggestions提升QoR

Report QoR Suggestions (RQS) 可識別設(shè)計問題,并提供工具開關(guān)和可影響工具....

淺談Vitis AI 3.5發(fā)布亮點(diǎn)

Vitis AI 平臺是為 AMD 器件、板卡及 Alveo 數(shù)據(jù)中心加速卡提供的一款綜合 AI 推....

視覺L1重映射函數(shù)Zynq baremetal設(shè)計實(shí)例

這篇博客展示了在 AMD Zynq 設(shè)計中,如何用 Vitis Vision Library 中的函....

如何在IBER眼圖上添加模板

標(biāo)準(zhǔn)協(xié)議的規(guī)范中一般都對眼圖模板都有詳細(xì)的規(guī)定,使用 IBERT 完成眼圖掃描后,通過設(shè)置一些參數(shù),....

在Vitis中通過PSU DDR執(zhí)行MicroBlaze應(yīng)用

MicroBlaze CPU 是可修改的拖入式預(yù)設(shè) 32 位/64 位 RISC 微處理器配置系列。

如何解決MPSoC萬兆以太網(wǎng)應(yīng)用中UDP接收丟包問題

本文介紹如何使能 Linux 網(wǎng)絡(luò)協(xié)議棧中的 RFS(receive flow steering)功....

Vitis? Model Composer 2023.1現(xiàn)已更新

Vitis Model Composer 是一個基于模型的設(shè)計工具,不僅可在 MathWorks M....

如何在Vivado硬件管理器內(nèi)讀取各項監(jiān)控值?

在 Vivado 內(nèi),以 Versal 器件為目標(biāo)創(chuàng)建一個示例,此示例將以 VCK190 開發(fā)板為目....

使用QEMU啟動Versal VCK190

本篇博文涵蓋了有關(guān)使用 PetaLinux 命令行來對 Versal Adaptive SoC 的 ....

XRT工具之Xbmgmt的使用方法

XRT 自2021.1更新后,原有的 XRT Tool指令發(fā)生了一些變化。包括xbmgmt,xclb....

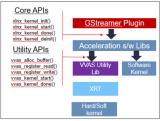

閑談Vitis AI|DPU在UltraScale平臺下的軟硬件流程(1)

本篇中,我想跳過一些細(xì)枝末節(jié), 先簡單介紹 AMD Xilinx Vitis AI 在 Zynq 這....

縮短MultiBoot流程中的回跳 (Fallback)時間

MultiBoot 是 FPGA 遠(yuǎn)程更新配置文件時一種非常普遍的應(yīng)用--為了確保安全,我們通常需要....

如何在設(shè)計中例化和使用多個BSCANE2模塊

本文對如何在一個工程里例化和使用多個BSCANE2模塊做一個簡單說明。

Versal GTY仿真:初始化,復(fù)位和速率變更

本篇博文側(cè)重于提供 Versal GTY 仿真示例、演示 GTY 如何解復(fù)位以及如何執(zhí)行速率變更。

在Versal中通過NoC從PS-APU對AXI BRAM執(zhí)行基本讀寫操作

本篇博文旨在演示如何通過 NoC 從 Versal 應(yīng)用處理單元 (APU) 訪問 AXI BRAM....

Vitis?統(tǒng)一軟件平臺2022.2最新更新

控制內(nèi)核在 AI 引擎陣列中的相對布局,從而提升性能,提高利用率。

AMD XILINX全新推出了Vivado ML Editions 2022.2版

智能設(shè)計運(yùn)行 (IDR) 是基本無需用戶干預(yù)的一鍵式時序收斂流程。在 2022.2 版中,我們首次為....

修改UG1209中介紹的USB BOOT啟動步驟

需要注意的是,要在 board preset 的基礎(chǔ)上減少外設(shè)的使用以防啟動鏡像過大,原因會在鏡像制....

如何使用Vivado 2022.1版本工具鏈實(shí)現(xiàn)ZCU102 USB啟動(上)

本文依據(jù) Vivado 2022.1 版本工具鏈的特性,對 UG1209( 最新版本為 2020.....

用Petalinux工具鏈幫助創(chuàng)建一個最小的Xen系統(tǒng)

在使用 Xen dom0-less 的時候,會有一個問題產(chǎn)生: 可以用 'xl'....