“更快”是每個系統(tǒng)設計師必備的詞匯,基于FPGA的設計亦是如此。如果您經(jīng)常試圖從FPGA設計中最大化地發(fā)掘每個MHz的性能,那么無疑Xilinx剛發(fā)布的一個白皮書您一定會非常感興趣。它的題目是“利用賽靈思All Programmable FPGA 和 SoC 實現(xiàn)高速無線電設計(Enabling High-Speed Radio Designs with Xilinx All Programmable FPGAs and SoCs”。如果您正在設計高速無線電蜂窩系統(tǒng)等,您就該看下這份白皮書。但其中的指南和技巧遠不只適用于無線設計,它還適用于使用可編程邏輯設計的各個高速系統(tǒng)。

白皮書指出的宗旨是“如果符合一些簡單的設計原則,高速無線設計可以很容易地建立在7系列FPGA架構上。Xilinx公司已經(jīng)創(chuàng)建了典型無線數(shù)據(jù)路徑的設計范例,表明中速級(-2)器件上使用的幾乎100%的 slice資源都支持500 MHz以上的時鐘頻率。

然而,這個白皮書中的內(nèi)容適用于所有數(shù)據(jù)路徑設計。

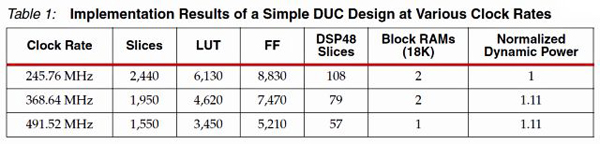

白皮書中的示例架構是單天線路徑DUC (數(shù)字上變頻器)架構,支持三種不同的時鐘速率: 245.76 MHz、368.64 MHz、和491.52 MHz。該設計利用Xilinx System Generator工具中的IP (FIR編譯器)、結構元件(如,DSP48基元的實例化)、接口VHDL代碼等進行構建。白皮書顯示DUC設計按照三個時鐘速率實現(xiàn)的關鍵的利用率指標:

首先需要注意的是,一般來說DSP48 slice數(shù)與時鐘速率成反比。快RAM資源也按照階躍函數(shù)隨時鐘速率降低。這在無線電信號處理設計中較常見,其中塊RAM基本上用來按照相對高的采樣率存儲大量函數(shù)運算的系數(shù)集合,例如,DDS(直接數(shù)字合成器)的正弦/余弦值,峰值抵消脈沖產(chǎn)生器中的CFR (波峰因數(shù)衰減)系數(shù),或DPD (數(shù)字預失真)模型中的非線性函數(shù)抽樣。

該分析不象邏輯資源那樣簡單。當時鐘頻率從368.64轉換至491.52 MHz(1.33時鐘比) ,按照比例LUT和FF的數(shù)據(jù)量分別減少了1.34和1.44倍。將時鐘速率從245.76放大一倍至491.52 MHz,這些數(shù)據(jù)減少了1.8倍和1.7倍。這種非線性行為基本上是為執(zhí)行信號處理控制邏輯,不需要按照時鐘頻率進行線性放大。

信號采樣率也影響資源利用率。比如,采樣速率為25 Msamples/sec的濾波器帶寬在250 MHz運行時與帶寬在500 MHz運行時相比所需的邏輯資源略降低兩倍。采樣速率為500 Msamples/sec的多相實現(xiàn)帶寬在250 MHz運行時與帶寬在500 MHz時相比,所需的邏輯資源增加兩倍。對邏輯資源使用的一階估計是時鐘頻率增加x倍相當于邏輯利用率減少0.85至1.1倍。

這些設計數(shù)據(jù)加上白皮書內(nèi)的更多數(shù)據(jù)顯示在設計基于FPGA的高性能系統(tǒng)時的常用建議:

? 適當?shù)牧魉€程序當然是設計高速程序的關鍵因素。

? 需要構建一個以上塊RAM(block RAM,)的存儲時,可通過選擇最大限度地減少數(shù)據(jù)復用和資源利用的配置優(yōu)化速度。舉例來說, 存儲16位數(shù)據(jù)的16K存儲器最好使用16K × 1位的塊RAM進行構建,而不是1K × 16位的塊RAM。

? DSP slice邏輯本質(zhì)上可支持較高的時鐘速率。邏輯電平與數(shù)據(jù)路由路徑的數(shù)量限制了速度,因此在構建高速設計時應在每一個或兩個LUT電平上插入一個寄存器。

? 定義合理的層次結構,按照邏輯分區(qū)將設計劃分成相應的功能模塊。這種層次結構提供便于在層次邊界寄存輸出的方法,從而限制特定模塊的關鍵路徑。這樣分析和修復在單一模塊中定位的時序路徑就很容易。實際上,定位超高時鐘速度時,應在層次結構的一些層級使用多個寄存器級,以優(yōu)化時序并為后端工具留下更多設計空間。好的設計層次結構應該將相關的邏輯集成在一起,使得區(qū)域分組和邏輯壓縮更為有效。

? 建立適當?shù)膶哟谓Y構可在多個模塊時獲取可重復結果。

? 在模塊級應用實現(xiàn)屬性,可令代碼簡單并具可擴展性,該屬性可傳播該模塊中聲明的所有信號。

? 良好的時鐘管理和時鐘分配方法至關重要。

? 盡可能減少獨立主時鐘數(shù)量。

? 將時鐘元件放在設計層次結構的頂層,以便在多個模塊共享時鐘,這將減少所需的時鐘資源,提高時序性能,并降低資源和功率利用率。

? 在不相關時鐘域之間使用適當?shù)脑偻郊夹g。

? 同樣的,必須定義足夠多的重置策略。一般情況下,不需要重置每個寄存器。重置寄存器不需要創(chuàng)建高扇出 nets,原因是那樣會降低時序性能,提高路由復雜性。只有在重置絕對必要的時候再進行重置。

? 最小化復位網(wǎng)絡的大小。

? 避免全局復位。

? 優(yōu)選同步復位,實際上對DSP48邏輯片和塊RAM是強制的。

? 限制時鐘“使能”的使用。實際上這條規(guī)則難以實現(xiàn),原因是在多周期實現(xiàn)中時鐘“使能”通常需要評估數(shù)據(jù)樣本或操作符輸出。實現(xiàn)有效的降低功耗技術很有效。在任何情況下,必須適當寄存時鐘使能信號以刪除高扇出 nets。

因此,如果您正在開發(fā)基于FPGA的高速設計,即使不是數(shù)字射頻應用,您有必要盡快下載和閱讀上述白皮書以開始您的設計——“利用賽靈思All Programmable FPGA 和 SoC 實現(xiàn)高速無線電設計”。

-

賽靈思

+關注

關注

33文章

1795瀏覽量

132132 -

DDS

+關注

關注

22文章

671瀏覽量

154065 -

數(shù)字預失真

+關注

關注

3文章

24瀏覽量

13699

發(fā)布評論請先 登錄

高速無線設計的“白皮書”

高速無線設計的“白皮書”

評論