重定時概述

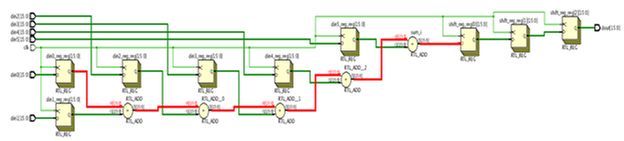

重定時是一種順序優(yōu)化技術,旨在不會影響電路的輸入/輸出行為的前提下在組合邏輯之間移動寄存器,以提高設計性能。圖 1 所示電路的關鍵路徑使用了一個 6 輸入加法器。以紅色突出顯示的路徑是對整個電路的性能起限制作用的路徑。

圖 1:寄存器到寄存器路徑設計示例:使用 6 個輸入加法器邏輯

通過將加法器輸出上的寄存器重定時到電路的組合邏輯,可以提升這里所示電路的性能。

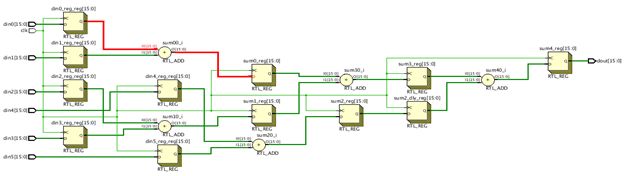

電路的整體時延為 4。圖 2 顯示移動寄存器使邏輯最小化的一種方法。將輸出寄存器移動到邏輯錐中被稱為后向重定時。完成此操作后,關鍵路徑將減少為只使用一個 2 輸入加法器。

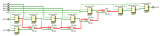

圖 2:寄存器到寄存器路徑設計示例:通過應用反向重定時使用一個 2 輸入加法器

注意:在上述示例中,寄存器的數量改變了。

圖 1 使用了 9 條不同的寄存器總線。圖 2 使用了 12 條不同的寄存器總線。這樣做的原因是,當執(zhí)行向后重定時時,即當它從輸出移動到輸入時,門的兩個輸入一定各有一個寄存器。

有兩種不同類型的重定時:后向重定時和前向重定時。后向重定時從門的輸出中移除寄存器,并在同一個門的輸入處創(chuàng)建新的寄存器。前向重定時完全相反,它從門的輸入端移除寄存器,并在輸出端創(chuàng)建一個新的寄存器。

要執(zhí)行后向重定時操作,組合邏輯必須僅驅動寄存器,而不是扇出到其他邏輯。要執(zhí)行前向重定時操作,門的每個輸入必須由具有相同控制邏輯的寄存器驅動。圖 3 顯示的是采用前向或后向重定時的同一個電路。

圖 3:前向重定時或后向后重定時的與門

全局重定時與局部后重定時

在 Vivado 綜合中,有兩種啟用重定時的方式:“全局”和“局部”。

全局重定時對整個設計進行重定時,并根據設計時序在大型組合邏輯結構中移動寄存器。

它會對設計中的所有邏輯進行分析,并在最壞情況的路徑中移動寄存器,以便設計能夠跑得更快。為了完成此操作,設計必須在 .xdc 文件中含有準確的時序約束。使用 synth_design 命令行中或 Vivado GUI 中綜合設置下的 -retiming 開關啟用全局重定時。 此外,此功能還可以與綜合中的 BLOCK_SYNTH 功能一起使用,作用于您設計中的特定模塊。

局部重定時是指用戶明確告訴工具使用 retiming_forward/retiming_backward RTL 屬性執(zhí)行重定時時的邏輯。

在執(zhí)行局部重定時時應小心,由于這種重定向不是時序驅動的,工具會完全按照要求進行操作。

如需了解更多有關使用重定時的信息,請參閱《Vivado Design Suite 用戶指南:綜合》 (UG901)。

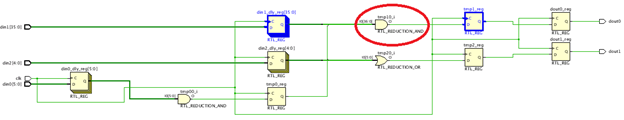

分析日志文件中的消息,圖 4 顯示的是可以改善邏輯層次的重定時示例。該結構的關鍵路徑有 3 個來自 37 位的與門的邏輯層次。源寄存器被稱為 din1_dly_reg,目標寄存器被稱為 tmp1_reg,在 tmp1_reg 后面還有一個邏輯層次為 0 的額外寄存器。

這是重新定時的理想途徑,因為我們可以把一個有 3 個邏輯層次的路徑(后跟邏輯層次為 0 的路徑)切換到有 2 個邏輯層次的路徑(后跟一個有 1 或 2 個邏輯層次的路徑)。

圖 4:可以向后重定時的電路

綜合日志文件類似于以下內容:

INFO: [Synth 8-5816] Retiming module "test"

Effective logic levels on critical path before retiming is: 3

Total number of crtical paths = 30

Optimizing at the module level

Optimizing locally to improve critical paths (may not reduce worst delay)

Effective logic levels on critical path after retiming is: 2

Total number of crtical paths = 30

Numbers of forward move = 0, and backward move = 1

Retimed registers names:

tmp1_reg_bret

tmp1_reg_bret__0

INFO: [Synth 8-5816] Retiming module "test" done

從此日志文件中,您可以看到重新定時之前和之后報告的邏輯層次,以及創(chuàng)建的新寄存器的名稱。當綜合從重定時創(chuàng)建新寄存器時,它會對后向重新定時的寄存器使用后綴“bret”、對前向重定時的寄存器使用“fret”。

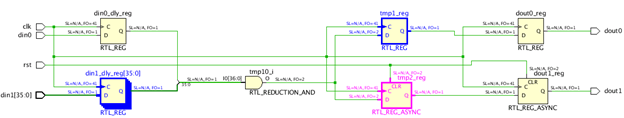

圖 5 中顯示的電路展示的是不兼容的寄存器元件會讓重定時變?yōu)榉欠ú僮鳌T摻Y構使用的仍是一個名為 din1_dly_reg 的啟動寄存器,通過一個 37 位的與門,產生 3 個邏輯層次,然后最后是一個名為 din1_dly_reg 的寄存器。此外,與門還有另一個以粉紅色突出顯示的寄存器扇出。

圖 5:無法重定時的電路示例

由于以粉色突出顯示的寄存器的存在,此示例無法重新定時。該寄存器采用了異步復位,而 tmp1_reg 沒有采用異步復位。由于兩個寄存器的控制集不相同,因此它們無法后向重定時到與門邏輯。此示例中的日志文件會顯示以下內容:

INFO: [Synth 8-5816] Retiming module "test"

Effective logic levels on critical path before retiming is: 3

Total number of crtical paths = 60

Optimizing at the module level

Cannot find a feasible solution:

backward propagation for flip-flop tmp1_reg:FD along instance tmp1_i_1:LUT2 fails due to incompatible flip-flops

Optimizing locally to improve critical paths (may not reduce worst delay)

Effective logic levels on critical path after retiming is: 3

Total number of crtical paths = 60

Numbers of forward move = 0, and backward move = 0

Retimed registers names:

tmp1_reg_bret

tmp1_reg_bret__0

INFO: [Synth 8-5816] Retiming module "test" done

日志文件內含有關不兼容觸發(fā)器的消息,并且之前和之后的邏輯層次不會改變。

在以下情況下不能進行重定時:

寄存器上加有時序異常約束(多周期路徑、可忽略路徑、最大延遲)。

存器有保留類型的屬性(DONT_TOUCH、MARK_DEBUG)。

帶有不同控制集的寄存器。

寄存器驅動輸出或由輸入驅動(除非設計被標記為 out-of-context)。

重定時無法提升反饋循環(huán)中的關鍵路徑的示例

當路徑的源寄存器和目標寄存器相同時,重定時優(yōu)化有可能無法改善邏輯層次。

例如:

寄存器“dout_reg”的關鍵路徑以紅色突出顯示。它通過一個減位與運算符,并在同一寄存器的復位引腳處結束。減位與運算符將基于我們采用的寬度(即 16 位)占用 2 個邏輯層次。

下面的屏幕截圖顯示綜合對關鍵路徑的性質的描述。

它還提到了作為關鍵路徑一部分的單元名稱。

INFO: [Synth 8-5816] Retiming module "test"

Effective logic levels on critical path before retiming is: 2

Total number of crtical paths = 192

Optimizing at the module level

Cannot find a feasible solution:

Worst path is a self-loop from dout_reg[14] to dout_reg[14]

Optimizing locally to improve critical paths (may not reduce worst delay)

Effective logic levels on critical path after retiming is: 2

Total number of crtical paths = 192

Numbers of forward move = 0, and backward move = 0

-

電路

+關注

關注

173文章

6022瀏覽量

174486 -

寄存器

+關注

關注

31文章

5423瀏覽量

123418

發(fā)布評論請先 登錄

Vivado綜合操作中的重定時(Retiming)

如何在Vivado 2016.1中進行寄存器平衡/寄存器重定時?

如何為管道設計插入寄存器并進行重定時?

Vivado 全局重定時vs 局部重定時

基于vivado的fir ip核的重采樣設計與實現(xiàn)

Vivado 2017.1和Vivado 2016.4性能對比分析

Tcl在Vivado中的基礎應用

Vivado中的重定時概述和應用

Vivado中的重定時概述和應用

評論