UART是一種通用串行數據總線,用于異步通信。該總線雙向通信,可以實現全雙工傳輸和接收。在嵌入式設計中,UART用于主機與輔助設備通信,如汽車音響與外接AP之間的通信,與PC機通信包括與監控調試器和其它器件,如EEPROM通信。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1643文章

21967瀏覽量

614263 -

寄存器

+關注

關注

31文章

5421瀏覽量

123398 -

uart

+關注

關注

22文章

1268瀏覽量

103294

發布評論請先 登錄

相關推薦

熱點推薦

FPGA的IP軟核使用技巧

,可以嘗試對IP軟核進行優化。例如,可以調整參數配置、優化布局布線、修改代碼等。

在調試過程中,可以利用FPGA開發工具提供的調試功能,如邏輯分析儀、波形查看

發表于 05-27 16:13

FPGA實戰演練邏輯篇42:寄存器電路的設計方式

寄存器電路的設計方式本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 上一章節中也已經基本介紹

發表于 06-26 11:53

FPGA實戰演練邏輯篇55:VGA驅動接口時序設計之2源同步接口

VGA驅動接口時序設計之2源同步接口本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 好,有了

發表于 07-29 11:19

UART寄存器介紹與中斷操作詳解

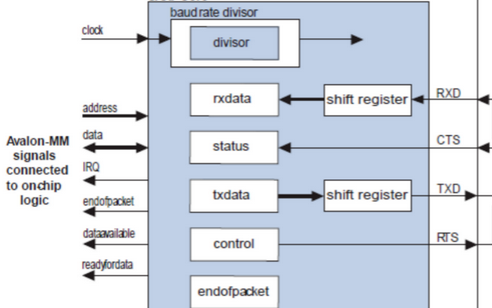

簡介 UART核提供了一個Avalon存儲器映射(Avalon-MM)的接口,這個接口使得Avalon-MM的主要周邊設備(例如Nios II處理器)通過讀和寫數據、控制

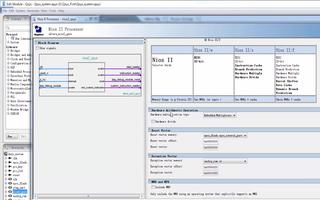

FPGA之軟核演練篇:UART的寄存器描述、配置選項與應用實例

FPGA之軟核演練篇:UART的寄存器描述、配置選項與應用實例

評論