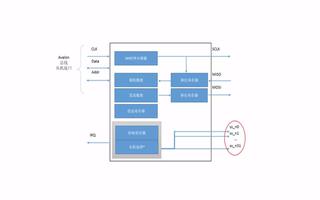

SPI是一種高速、高效率的串行接口技術。通常由一個主模塊和一個或多個從模塊組成,主模塊選擇一個從模塊進行同步通信,從而完成數據的交換。SPI是一個環形結構,通信時需要至少4根線(事實上在單向傳輸時3根線也可以)。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

SPI

+關注

關注

17文章

1804瀏覽量

95881 -

串行接口

+關注

關注

3文章

388瀏覽量

44206 -

IP核

+關注

關注

4文章

338瀏覽量

50788

發布評論請先 登錄

相關推薦

熱點推薦

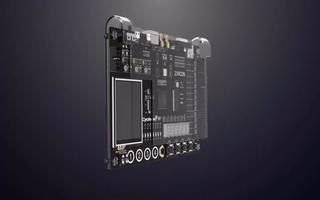

【鋯石A4 FPGA試用體驗】鋯石科技-A4 FPGA開發板開箱鑒賞-您將得到的是一門技術

全家福開啟說明書與光盤包裝盒,包含以下附件:鋯石科技-A4 FPGA開發板引導手冊一本鋯

發表于 07-29 16:33

【鋯石A4 FPGA試用體驗】初識鋯石A4 FPGA開發板

` 本帖最后由 jinglixixi 于 2017-8-3 11:14 編輯

期待中的鋯石A4 FPGA開發板終于如期而至了,欣喜中快速

發表于 08-03 11:12

【鋯石A4 FPGA試用體驗】鋯石A4智能家庭娛樂系統-結項報告

` 本帖最后由 超級開發板 于 2017-10-8 10:45 編輯

今天,我們來進行基于鋯石A4 FPGA

發表于 09-28 08:58

鋯石FPGA A4_Nano開發板視頻:LED的IP核應用

利用IP核設計電子系統,引用方便,修改基本元件的功能容易。具有復雜功能和商業價值的IP核一般具有知識產權,盡管IP

鋯石FPGA A4_Nano開發板視頻:內置IP核SPI的理論原理講解

SPI是串行外設接口(Serial Peripheral Interface)的縮寫,是一種高速的,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,節約了芯片的管腳,同時為PCB的布局上節省空間,提供方便,正是出于這種簡單易用的特性,越來越多的芯片集成了這種通信協議.

鋯石FPGA A4_Nano開發板視頻:內置IP核SystemID的講解

System ID用來在區域內唯一標識主機或路由器。在設備的實現中,它的長度固定為48bit(6字節)。一般情況下,我們采用設備的router-id轉換為System ID。

鋯石FPGA A4_Nano開發板視頻:內置IP核JTAG-UART的講解

JTAG UART是要自己添加的一個IP核,通常用來是實現PC和Nios II系統間的串行通信接口,它用于字符的輸入輸出,在Nios II的開發調試過程中扮演了重要的角色。

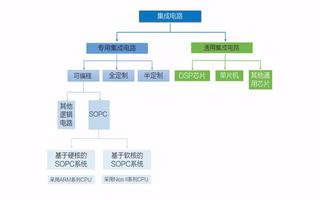

鋯石FPGA A4_Nano開發板視頻:什么是Qsys?如何構建一個Qsys系統?

視頻中進一步介紹了Nios II處理器的體系結構、Qsys豐富多彩的內置IP,以及Avalon總線接口規范,然后我們又以Avalon總線接口規范為基礎,進一步定制了開發板所有外設的

鋯石FPGA A4_Nano開發板視頻:內置IP核之Interval Timer的應用實戰講解

利用IP核設計電子系統,引用方便,修改基本元件的功能容易。具有復雜功能和商業價值的IP核一般具有知識產權,盡管IP

鋯石FPGA A4_Nano開發板視頻:內置IP核SPI的應用實例講解

鋯石FPGA A4_Nano開發板視頻:內置IP核SPI的應用實例講解

評論