聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

存儲器

+關注

關注

38文章

7636瀏覽量

166420 -

DDR

+關注

關注

11文章

731瀏覽量

66397 -

仿真

+關注

關注

51文章

4240瀏覽量

135314

發布評論請先 登錄

相關推薦

熱點推薦

利用.func命令運行仿真的方法

在上篇 LTspice 系列文章中,我們分享了如何利用ISO模型進行電源線瞬態電傳導干擾測試,本文將介紹使用 .func 命令中的指定常數以有效運行仿真并進行參數分析的方法。更多參數分

Verilog 電路仿真常見問題 Verilog 在芯片設計中的應用

在現代電子設計自動化(EDA)領域,Verilog作為一種硬件描述語言,已經成為數字電路設計和驗證的標準工具。它允許設計師以高級抽象的方式定義電路的行為和結構,從而簡化了從概念到硅片的整個設計流程

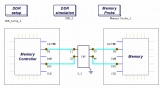

DDR5內存的工作原理詳解 DDR5和DDR4的主要區別

的數據傳輸速率、更大的容量和更低的功耗。 2. DDR5內存工作原理 DDR5內存的工作原理基于雙倍數據速率技術,即在每個時鐘周期內傳輸兩次數據。DDR5內存通過提高數據傳輸速率、增加數據預取和優化功耗

wms智能倉儲管理系統標準化流程

wms智能倉儲管理系統標準化流程的標準化流程通常包括以下幾個主要步驟: 需求分析:與客戶充分溝通,了解其倉儲管理需求和業務流程,確定系統功能

DDR Inline ECC在Jacinto7 SoC中的應用

電子發燒友網站提供《DDR Inline ECC在Jacinto7 SoC中的應用.pdf》資料免費下載

發表于 09-27 11:04

?0次下載

DDR4尋址原理詳解

)的尋址原理是計算機內存系統中至關重要的一個環節,它決定了數據如何在內存中被有效地存儲和訪問。DDR4的尋址原理復雜而高效,以下將詳細闡述其關鍵要素和工作流程。

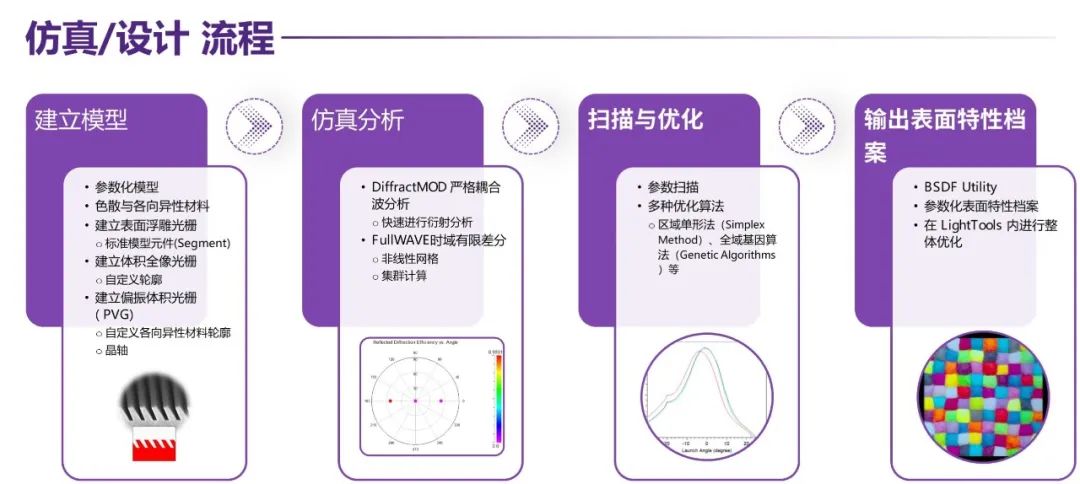

使用新思科技波動光學軟件RSoft進行光柵仿真/設計的流程

增強現實(AR)眼鏡使用戶能夠在現實世界的環境中疊加數字圖像,可廣泛應用于教育、醫療、導航、游戲和娛樂等領域。為了設計更輕巧的AR眼鏡,利用超緊湊的衍射光波導元件成為其中一種具有潛力的方案,其中關鍵

基于FPGA的DDR3多端口讀寫存儲管理設計

今天給大俠帶來《基于FPGA的DDR3多端口讀寫存儲管理設計》,話不多說,上貨。

摘要

為了解決視頻圖形顯示系統中多個端口訪問DDR3時出現的數據存儲沖突問題,設計了一種基于

發表于 06-26 18:13

RFID資產管理系統在現代企業中的應用

RFID資產管理系統利用RFID技術實現資產信息的全面數字化和智能化管理,提升管理效率和資產利用率。系統可實時跟蹤資產,優化盤點

利用高級仿真解決設計流程中管理DDR問題

利用高級仿真解決設計流程中管理DDR問題

評論