CMOS開關的性能已經提升至已經突破1-GHz阻隔,并且現在能夠與GaAs開關競爭。

高性能RF開關是關鍵構建模塊之一在現代無線通信系統中需要。對于高頻應用,例如移相器,可切換濾波器,雷達系統的發射器和接收器,從大型裝置到防撞雷達,人們都非常關注具有低插入損耗,端口間隔離度高,低失真和低電流消耗的開關。從基站到手機的汽車和通信系統。

傳統上,只有少數工藝可用于開發良好的寬帶/ RF開關。砷化鎵(GaAs)FET,PIN二極管和機電繼電器已占據市場主導地位,但標準CMOS正在嶄露頭角。

GaAs因其低導通電阻,低關斷電容和高線性度而廣受歡迎。在高頻率。隨著CMOS工藝幾何尺寸的不斷縮小,CMOS開關的性能已經提高到可以突破1 GHz的勢壘,現在能夠與GaAs開關競爭。 CMOS開關旨在最大限度地提高帶寬,同時保持低成本,是低成本,低功耗應用中昂貴的GaAs開關的替代品。

本文介紹了與寬帶交換機相關的主要規范,用于寬帶交換的傳統方法以及CMOS交換機技術的優勢。它還展示了新型CMOS開關在低功耗,高頻應用中如何能夠勝過GaAs開關。這應該說服您,CMOS寬帶開關是電纜調制解調器,MRI掃描儀,xDSL調制解調器,下一代無繩電話以及航空工業中需要工作頻率高達1 GHz甚至更高的應用的理想解決方案。

寬帶交換機基礎

寬帶交換機旨在滿足高達1 GHz及更高頻率的設備傳輸需求。為這些類型的應用選擇器件完全取決于它們在頻率上的表現。有兩種重要的方法可以描述RF開關的性能:閉合狀態下的插入損耗和開路狀態下的隔離。

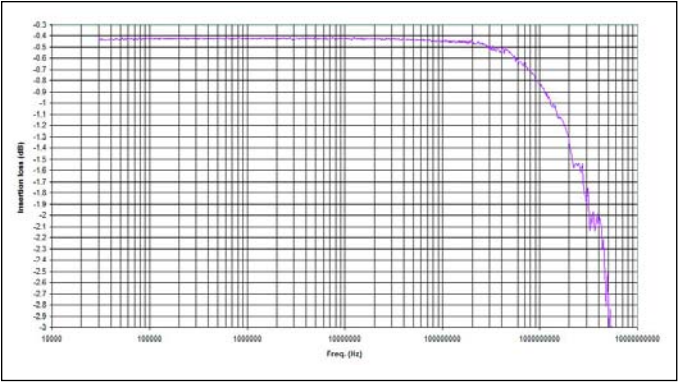

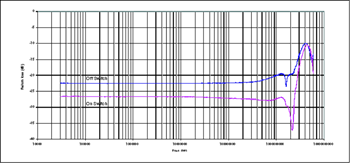

插入損耗是輸入之間的衰減當開關打開時,開關的輸出端口和輸出端口。低插入損耗對于需要較低總噪聲系數的系統至關重要。由于開關是信號路徑中的第一個組件之一,因此最小可接收信號非常重要。圖1顯示了ADG919的插入損耗與頻率的典型曲線。

該圖顯示插入損耗小于0.5 dB至100 MHz,1 dB時為0.8 dB,以及2 GHz時為1.5 dB。這與許多GaAs開關相當,典型值在1 GHz時為0.7 dB至1 dB。

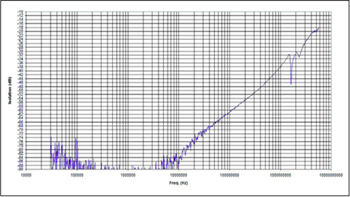

斷開隔離定義為開關關閉時開關輸入和輸出端口之間的衰減。圖2顯示了斷開隔離與頻率的典型圖。大多數寬帶開關都需要高隔離度,并且通常是確定器件是否適合特定應用的關鍵規范。

該圖表明開關隔離度優于70 dB以上大約80 MHz,1 GHz時為37 dB,2 GHz時大約為20 dB。這種關斷隔離規范的性能比許多GaAs開關高出約10 dB /十倍。 1 GHz的典型GaAs開關值介于25和40 dB之間。 1 GHz時30 dB的通道間隔離確保了通道之間的串擾最小。

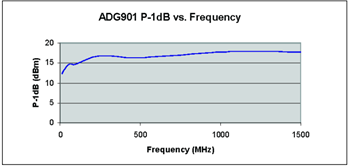

另外兩個重要的RF開關規格與交換機可以處理的功率水平有關。第一個是1 dB壓縮點,P 1dB ,這是開關插入損耗比其低電平值增加1 dB的RF輸入功率電平。 P 1dB 衡量開關在扭曲或壓縮信號之前可以處理多少功率,因此是RF功率處理能力的衡量標準。接下來,當緊密間隔的音調通過開關時,開關的非線性導致產生假音調。輸入三階交調截點IIP3是這些假音調中的功率的度量,并且與開關引起的失真量直接相關。圖3顯示了P 1dB 壓縮點與頻率的關系。在這種情況下,1GHz下的P 1dB 是17dBm。此開關在900 MHz時的IIP3為33 dBm,非常適合中等功率,高頻應用,包括采用GPS或其他增強功能的蜂窩手機中的IF切換。

傳統交換解決方案:

1、引腳二極管

PIN二極管基本上是無線電和微波頻率的電流控制電阻。 PIN二極管通常用于切換RF信號,因為它們在導通時是高度線性的并且表現出非常好的失真特性。通過在P型和N型硅區域之間放置高電阻率本征(I)區域來制造PIN二極管。 PIN二極管的電阻值僅由正向偏置的直流電流決定,因此可用于開關功能。當PIN二極管正向偏置時,電子和空穴從P區和N區注入I區。電子和空穴不會立即重新組合;相反,存儲有限電荷,導致I區的電阻率降低并允許傳導。對于不同的偏置電流,獲得的典型電阻值在0.1歐姆(1 A)至10歐姆(1μA)左右。

因此,使用PIN二極管時的第一個缺點是它們需要大量的DC功率以實現低電阻率和低插入損耗。當它們用于便攜式設備(例如PDA和手持式儀表)時,這是一個巨大的缺點,因為電池壽命與功耗成正比。當使用單串聯或并聯PIN二極管時,在較高頻率下也難以實現超過30 dB的隔離。為了獲得更高的隔離級別,必須以串聯 - 分流器組合連接兩個或更多個二極管。這會增加插入損耗。

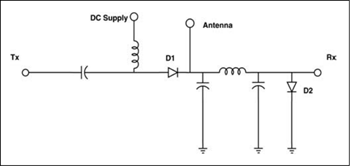

典型的發送/接收(TX / RX)PIN二極管開關原理圖如圖4所示。它由兩個二極管組成,一些隔直電容,一個電感饋送DC正向偏置控制信號,以及一些分立元件以產生四分之一波長線。如果需要切換額外的RF端口,則需要更多串聯二極管,這會導致插入損耗增加。在該應用中增加插入損耗的效果是雙重的。在TX側,功率放大器和天線之間的每分貝分貝都意味著TX信號需要更多放大,從而縮短電池壽命。在RX側,插入損耗的增加將降低接收信號強度,降低整體信噪比(SNR)和接收器靈敏度。

PIN的另一個限制二極管是指它們需要一個外部驅動器來控制TX / RX開關的開關速度和可以使用的接口電平。

2、 GaAs開關

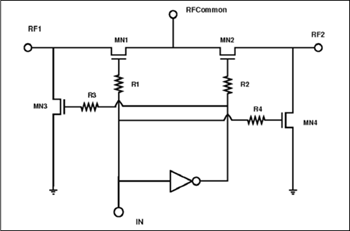

近年來,GaAs開關由于其低DC功耗(與PIN二極管相比)而在寬帶開關市場占據主導地位。 GaAs開關由作為電壓控制電阻器的晶體管陣列組成。 GaAs晶體管是三端器件;柵極電壓(V g )控制其他兩個端子之間的電阻。為了增加RF端口之間的隔離,它們可以串聯或作為分流器件接地。與PIN二極管不同,串聯放置多個晶體管實際上有助于RF功率處理和線性度,對插入損耗幾乎沒有影響。典型的TX / RX開關原理圖如圖5所示。這里,晶體管以串聯 - 并聯配置連接,以獲得最佳的插入損耗和隔離性能。這種配置的缺點是MN1 / MN4和MN2 / MN3的互補切換要求高邏輯電平和低邏輯電平同時可用,這增加了控制電路的復雜性,從而增加了成本。

MMIC GaAs開關可從各種公司獲得。全部使用N溝道耗盡型FET作為基本開關器件。這些設備顯示的特性如下:

V g = 0 - >開啟

V g =負 - >關閉(Pinchoff)

Pinchoff定義為通道變為高阻抗的電壓。這通常發生在-3V的V g ,這取決于所使用的工藝。開關輸入端的RF電平可以調制V g ,從而隨著開關導通電阻的變化而產生失真產物。使用高控制電壓將降低這種影響,但僅以產生大約+ 2V至-8V的電壓來控制開關。 GaAs工藝不提供互補器件,因此需要更多電流才能創建CMOS技術中易于使用的逆變器邏輯功能。 GaAs開關的這種固有的責任使它們難以集成到使用正低壓電源的大多數現代電子系統中。 GaAs開關制造商通過添加與開關的RF引腳串聯的隔直電容來解決這個問題。這有效地使管芯相對于DC接地浮動,這允許用正控制電壓控制開關。然而,缺點是DC阻塞電容器限制了開關可以處理的帶寬,因此限制了它們在寬帶系統中的使用。電容器本身相對便宜,但額外的印刷電路板面積和制造成本會顯著增加整體開關成本。此外,與開關串聯的任何組件都會增加插入損耗并對系統SNR產生直接影響。電感或路徑長度的任何增加都會降低器件的性能,從而給系統設計人員帶來額外的問題和需要克服的問題。

如前所述,GaAs開關的控制信號需要從外部來源。有很多方法可以做到這一點;最簡單和最常見的是增加外部CMOS驅動器IC。這種額外的IC不僅消耗功率,還增加了PC板面積和組裝成本。最近,GaAs開關制造商推出了多芯片模塊(MCM),它將CMOS / BiCMOS驅動器芯片和GaAs開關芯片封裝成一個大型BGA封裝。這些MCM工作得很好,但主要缺點是整體解決方案成本高,由兩個芯片的單獨成本組成,并且由于更大的封裝和芯片互連而增加了組裝成本。

CMOS拯救

正如摩爾定律[1]預測的那樣,標準CMOS工藝幾何尺寸不斷減小。開放CMOS的市場之一是射頻/微波IC領域。隨著晶體管長度的減小,CMOS實現了低導通電阻,低關斷電容以及高達1 GHz甚至更高的良好線性度。 RF開關也是如此,因為現在可以使用帶有1 GHz,3 dB帶寬的CMOS開關。

與GaAs開關類似,CMOS開關使用NMOS FET,它們基本上用作電壓控制電阻。這些設備顯示的特性如下:

V gs > V t - >開啟

V gs t - >關閉

V t 定義為閾值電壓,高于此閾值電壓,在源極和漏極之間形成導電溝道終端。 FET可以采用互鎖指狀布局,以減少源極和漏極之間的寄生電容,從而提高高頻隔離度。

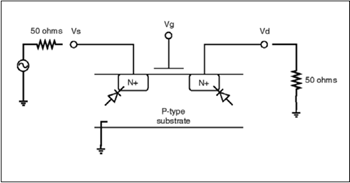

如前所述,CMOS開關適用于許多低功耗應用。由于兩個原因,它們的功率處理能力降低了:第一,如圖6所示的固有NMOS結構由P型襯底中的兩個N型材料區域組成,這導致在兩者之間形成寄生二極管。 N和P區域。當偏置為0 VDC的AC信號放置在晶體管的源極上,并且Vgs使晶體管導通時,寄生二極管可以在輸入波形的負半周期的某些部分正向偏置。一旦輸入正弦波低于約-0.6 V,二極管將開始導通。這將導致輸入信號被壓縮。在低頻時,輸入信號在較長的時間段內低于-0.6 V電平,因此對1 dB壓縮點(P 1dB )具有更大的影響。第二種機制是分流NMOS器件在應該關閉時部分導通。如前所述,NMOS晶體管處于截止狀態,其中V gs t 。在分流裝置的源極上有交流信號時,波形的負半周期將有一個時間,其中V gs ≥V t ,從而部分開啟分流裝置。這將導致輸入波形通過將其部分能量分流到地而進行壓縮。當開關在低頻(<30 MHz)和高功率(> 10 dBm)下使用時,可以通過對RF輸入信號施加小的DC偏壓(~0.5 V)來克服這兩種機制。與GaAs開關不同,CMOS開關不需要隔直電容。

CMOS的優點

使用CMOS設計寬帶寬有許多關鍵優勢開關。以下各節重點介紹了主要優勢和關鍵的高性能規格。

成本:當今成本驅動型市場中最重要的優勢是CMOS工藝比GaAs工藝,可降低芯片成本。 CMOS開關使用正電壓控制,不需要隔直電容。另一方面,GaAs晶體管是負電壓控制器件。這排除了使用CMOS驅動器,需要在RF輸入上使用隔直電容,并導致整體解決方案成本的增加。 CMOS開關比GaAs同類產品更便宜,更易于使用。

單引腳控制接口: CMOS開關具有單引腳控制接口,可實現最大的電路布局效率,使移動無線系統等許多應用受益。這是可能的,因為CMOS允許將驅動器/開關控制電路集成到與開關相同的芯片上,從而有效地減少了控制引腳的數量。 CMOS技術提供的控制接口具有簡單的單引腳控制,與許多GaAs RF開關實現的互補控制信號形成對比。例如,對于SPDT(單刀雙擲)開關,GaAs器件需要兩條控制線,而CMOS器件只需要一條。

簡易系統集成: CMOS開關技術的片上驅動器可以與TTL和CMOS邏輯電平連接,允許器件與其他CMOS / BiCMOS IC(如微控制器)輕松集成。 CMOS和LVTTL兼容的控制輸入在許多應用中提供了非常簡單的接口。

無需在CMOS開關的RF輸入上增加隔直電容,消除了對帶寬減少的擔憂或減少系統性能的影響 - 上一節中描述的原因。

減小封裝尺寸:驅動器/開關控制電路的簡單集成具有小封裝尺寸的額外優勢。 CMOS芯片的整體尺寸更小,允許CMOS器件以更小的封裝組裝,其引腳數量低于GaAs制造商提供的MCM。標準的SPDT開關引腳數可以從用于CMOS解決方案的適度8引腳封裝到用于GaAs解決方案的20引腳。

對于SP4T器件,這種節省空間的情況更為明顯。 CMOS器件采用微型16引腳3 mm×3 mm LFCSP(引腳架構芯片級封裝)套件。 GaAs SP4T產品可能需要負電壓或正/負電壓電源,以及多達8條控制線。它們采用24引腳10.65 mm×15.6 mm寬體SOIC(小外形)或28引腳12.57 mm×12.57 mm PLCC(塑料引線芯片載體)封裝。

更低的功耗: CMOS開關的極低功耗使其成為便攜式應用的理想選擇。

可用的CMOS RF開關可在1.65 V至2.75 V范圍內工作電源的典型電流消耗小于1μA,顯著低于等效GaAs解決方案的電流消耗。

其他CMOS開關性能亮點:匹配也非常有用CMOS開關。圖7顯示了開/關開關的回波損耗與頻率的典型曲線圖。該圖顯示,對于關斷開關,S 11 值為10 dB時為27 dB,1 GHz時為26 dB,關閉開關時為1 dB時為20 dB,1 GHz時為20 dB。這是相對于端口處的入射功率的反射功率量。回波損耗大,表明匹配良好。 CMOS開關具有額外的靈活性,可選擇反射(0歐姆)或吸收(50歐姆)版本,允許開關與應用匹配。例如,ADG918是一個吸收(或匹配)SPDT開關(2:1 Mux),具有50歐姆端接分流支腳,ADG919是具有直接分流接地的反射SPDT開關。對于阻抗匹配最關鍵的應用,吸收開關將是優選的。與前面描述的CMOS開關的隔離性能類似,CMOS工藝規定的回波損耗比許多GaAs開關高出約10 dB /十倍。

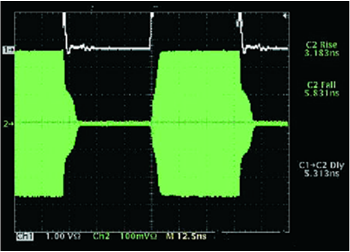

開關時間也很好,帶CMOS開關典型的開關時間為5 ns,比許多GaAs器件快10倍。圖8顯示了典型ADG901的5 ns開關時間。在極端溫度條件下,該器件的時序規格最大為8 ns,而許多GaAs開關的微秒級則為微秒。

結論

CMOS開關提供了比GaAs器件更簡單的整體解決方案,適用于高頻開關要求,還具有成本更低的優勢。

ADG9xx系列寬帶CMOS開關的3 dB頻率大于3 GHz,在1 GHz時的插入損耗非常低,為0.8 dB,1 GHz時的隔離度大于37 dB。這些特性使這些器件非常適用于DC至1 GHz及更高頻率的許多應用。這些開關為GaAs RF開關提供了主要的CMOS挑戰,是低功耗,高性能,高頻開關應用的最佳解決方案。

-

CMOS

+關注

關注

58文章

5995瀏覽量

238119 -

無線通信

+關注

關注

58文章

4712瀏覽量

144862 -

RF

+關注

關注

65文章

3171瀏覽量

168526

發布評論請先 登錄

CMOS交換機技術的優勢及應用介紹

CMOS交換機技術的優勢及應用介紹

評論