今天我們來介紹一下如何修復ECO階段的Noise Violation. 首先,我們也來介紹一下什么是Noise。

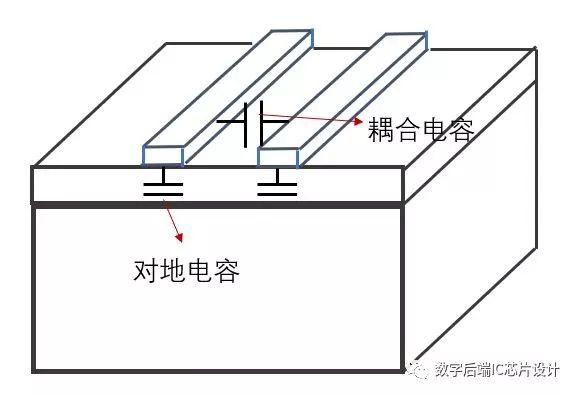

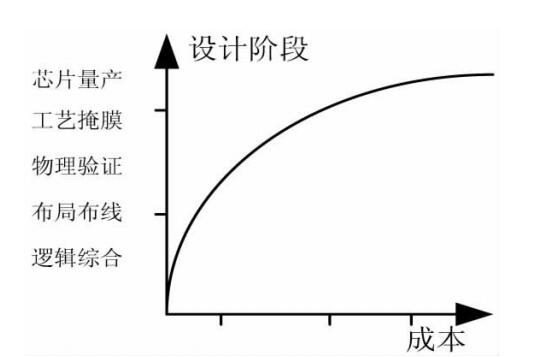

網(wǎng)上資料很多,大致整理一下,noise(噪聲)也稱為crosstalk(串擾),signal integrity(信號完整性分析),是隨著芯片特征尺寸變小后引發(fā)的現(xiàn)象。主要指工藝金屬層線變窄,間距變小以后,導致線與線之間的耦合電容(coupling capacitance)增大,接地電容變小(如下圖所示)。而Noise的大小與耦合電容成正比,與接地電容成反比。所以導致Noise的影響變大。

那么在后端PR中,noise對我們的影響,主要分為兩大類:信號的延遲(delay)和毛刺(glitch)。這兩類問題都會對芯片的性能產(chǎn)生影響。

Noise與信號延遲

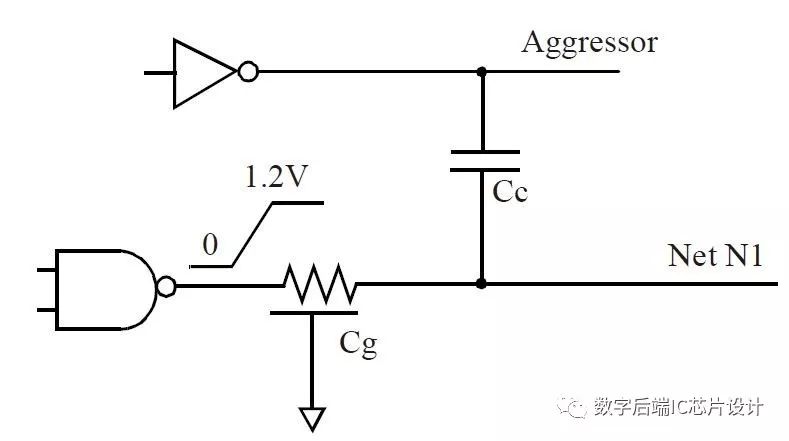

首先我們來講下noise對信號延遲的影響,在分析noise時,我們將產(chǎn)生noise信號源的網(wǎng)絡稱為侵害網(wǎng)絡(aggressor net或attacker),受到串擾的網(wǎng)絡稱為受害網(wǎng)絡(victim net)。當aggressor的信號在0 和1之間電平變換時,victim上會產(chǎn)生相應的串擾噪聲,這種轉(zhuǎn)換噪聲能使victim的信號轉(zhuǎn)換變慢或變快。如果victim受到相同方向跳變的aggressor,會造成它的delay變小;如果victim受到相反方向跳變的aggressor,會造成它的delay變大。

如下圖所示:Net N1作為victim,與Aggressor有Cc的耦合電容。假設Net N1正在0~1發(fā)生跳變。如果aggressor也在發(fā)生0~1的跳變,那么它的上升沿會耦合到N1上面,會造成N1的delay變小;如果aggressor正在發(fā)生1~0的跳變,那么它的下降沿作用到N1上時,該信號轉(zhuǎn)換變慢,會造成它的delay變大。

Noise雖然會對信號延遲產(chǎn)生影響,惡化時序。但是,如果在它影響下,時序依然可以signoff,那么我們可以不必去修復它。

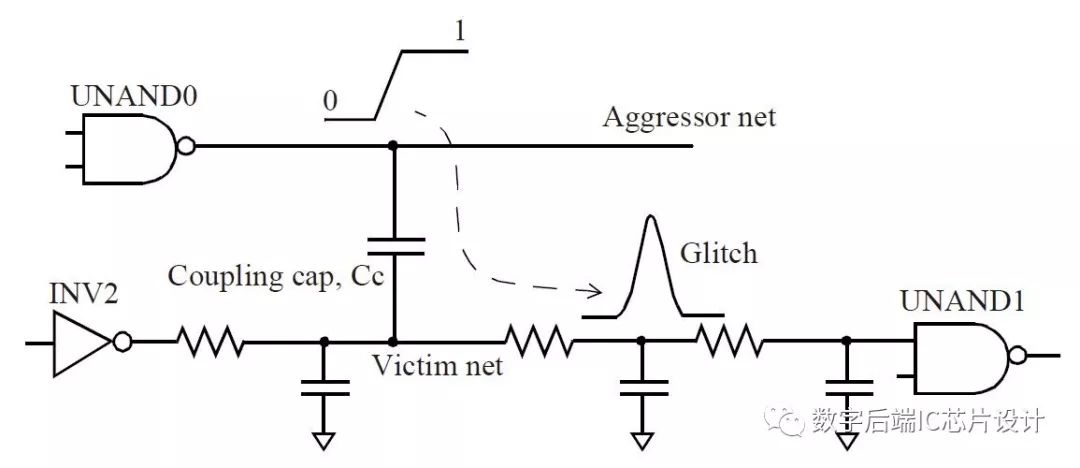

Noise與毛刺

Noise引發(fā)的另一種現(xiàn)象,我們稱為毛刺(Glitch)。如下圖所示,當victim net受到aggressor net跳變影響時,就會有毛刺信號通過耦合電容引入。

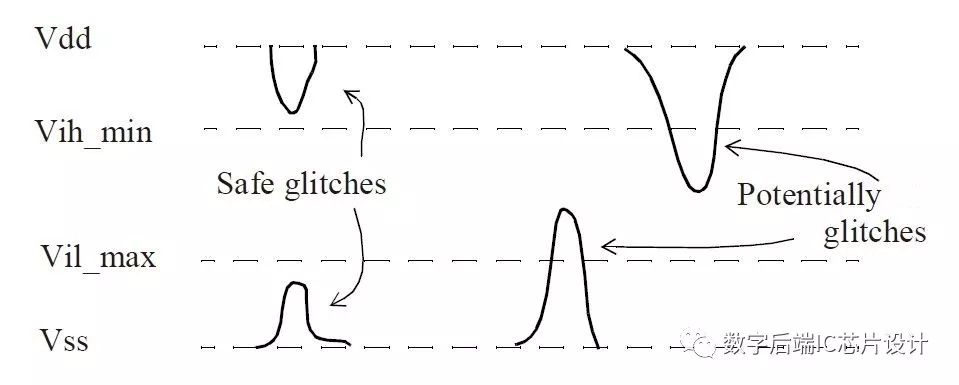

如下圖所示,有時候,這個毛刺信號比較小,可以忽略;但是,當毛刺信號足夠高而且持續(xù)時間較長,這就有可能導致邏輯功能發(fā)生變化,破壞了門電路所保存的狀態(tài),使得電路發(fā)生故障。因此,在最后timing signoff中,noise引起的glitch是我們必須要修復的violation。

那么,在后端PR中,如何來修復Glitch呢?

有很多方法,下面列舉幾種;

(1)降低aggressor net的驅(qū)動能力

aggressor net的驅(qū)動能力越強,Glitch的量級就越大。

(2)增強victim net的驅(qū)動能力

victim net驅(qū)動能力越弱的話,Glitch的量級也會越大。使用髙驅(qū)動單元可提髙潛在victim net的門限,從而降低victim net的受害程度。

(3)保護victim net

將victim net和aggressor net之間的間距加大,或者采用屏蔽線shielding都是保護victim net的一些好方法。

(4)給victim net插入Buffer

插buffer是后端修復violation的萬能手段。它也是是處理noise時一項非常有效的修復技術。通過插入buffer將長線打斷能有效降低victim net上的耦合電容,從而降低noise的影響。

-

信號完整性

+關注

關注

68文章

1445瀏覽量

96734 -

Noise

+關注

關注

0文章

19瀏覽量

11450

原文標題:愁緒千萬端,擾亂不成眠——如何修復Noise?

文章出處:【微信號:IC_Physical_Design,微信公眾號:數(shù)字后端IC芯片設計】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

FPGA編譯在place步驟顯示“unusual high hold time violation detected”

ADC Input Noise: The Good,The

如何解決“access violation at address”錯誤

汽車eco模式使用技巧_eco模式真能省油嗎

Uber聯(lián)合創(chuàng)始人發(fā)行加密貨幣Eco 希望Eco能夠復蘇虛擬貨幣

我們?nèi)绾蝸?b class='flag-5'>修復setup violation?

如何來手動修復max transition和max capacitance

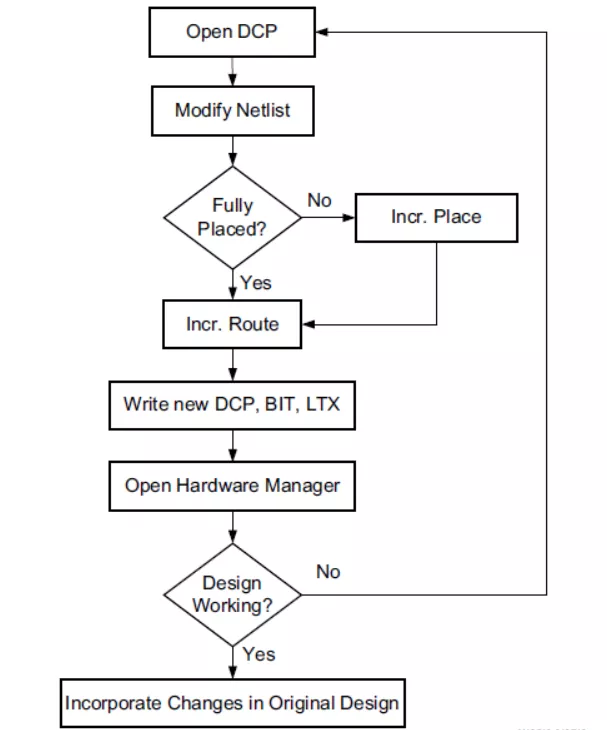

如何在Vivado中執(zhí)行工程變更命令 (ECO)

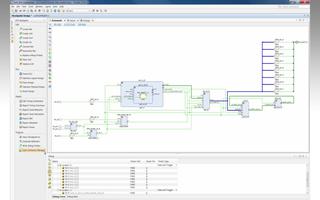

圖形界面介紹:GUI上的按鍵是Violation Browser

ECO技術在SoC芯片設計中的應用

詳解Xilinx FPGA的ECO功能

什么是DFT友好的功能ECO呢?

解析什么是DFT友好的功能ECO?

如何修復ECO階段的Noise Violation

如何修復ECO階段的Noise Violation

評論