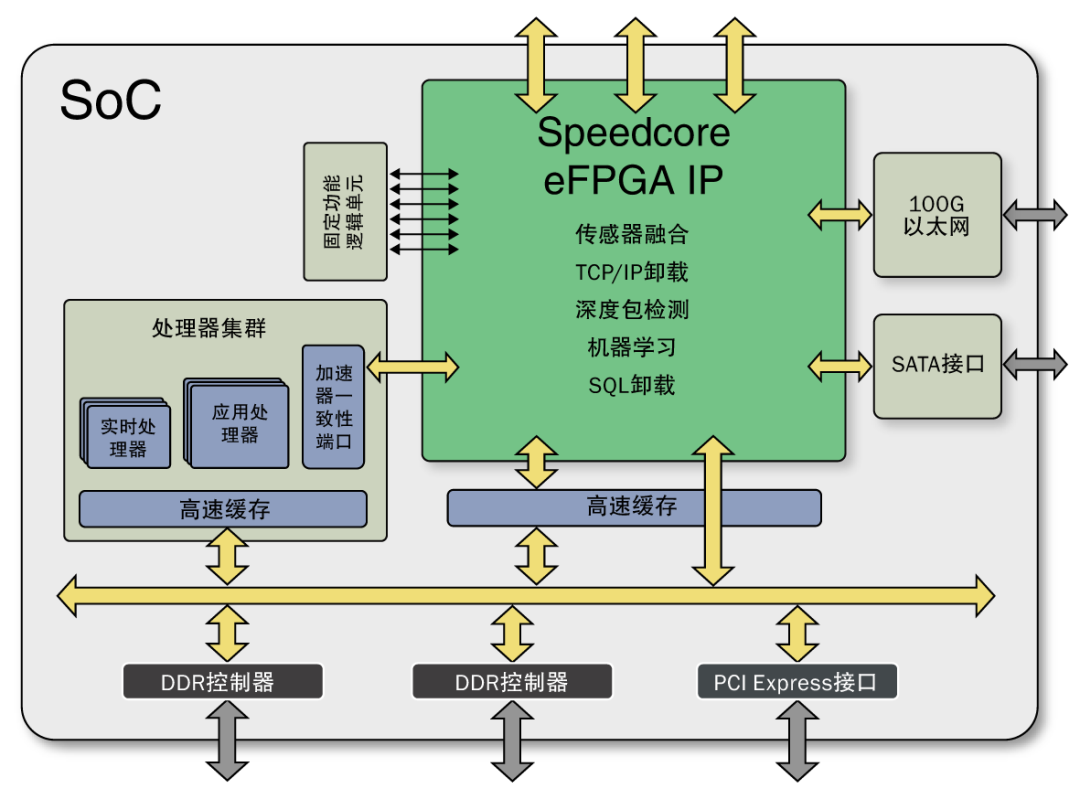

2016年,Achronix推出的Speedcore成為首款向客戶出貨的嵌入式FPGA(eFPGA)IP,使客戶將FPGA功能集成到他們的SoC中成為可能。由于Speedcore IP是專為計(jì)算和網(wǎng)絡(luò)加速應(yīng)用而設(shè)計(jì)的,并基于Speedster22i FPGA系列相同的高性能架構(gòu),采用Speedcore作為硬件加速器的方案被廣泛應(yīng)用到數(shù)據(jù)中心和通信基礎(chǔ)設(shè)施等領(lǐng)域。據(jù)了解,eFPGA IP授權(quán)業(yè)務(wù)在過去兩年間快速增長(zhǎng),2017年,已經(jīng)占到Achronix FPGA整體營(yíng)收的20%,而2018年,憑借其顯著的功耗和成本優(yōu)勢(shì),eFPGA IP授權(quán)業(yè)務(wù)比重進(jìn)一步提高。

本月,Achronix宣布推出第四代嵌入式FPGA產(chǎn)品Speedcore Gen4 eFPGA IP。較前代產(chǎn)品,Speedcore Gen4將性能提高了60%、功耗降低了50%、芯片面積減少65%,同時(shí)保留了原有的Speedcore eFPGA IP的功能,即可將可編程硬件加速功能引入廣泛的計(jì)算、網(wǎng)絡(luò)和存儲(chǔ)應(yīng)用,實(shí)現(xiàn)接口協(xié)議橋接/轉(zhuǎn)換、算法加速和數(shù)據(jù)包處理。

圖:Speedcore 7t較前代產(chǎn)品性能顯著提升

據(jù)Achronix市場(chǎng)營(yíng)銷副總裁Steve Mensor介紹,創(chuàng)新的架構(gòu)使這些性能提升成為可能。與上一代Speedcore產(chǎn)品相比,新的Speedcore Gen4架構(gòu)實(shí)現(xiàn)了多項(xiàng)創(chuàng)新,從而可將系統(tǒng)整體性能提高60%。其中查找表的所有方面都得到了增強(qiáng),以支持使用最少的資源來實(shí)現(xiàn)各種功能,從而可縮減面積和功耗并提高性能。其中的更改包括將ALU的大小加倍、將每個(gè)LUT的寄存器數(shù)量加倍、支持7位函數(shù)和一些8位函數(shù)、以及為移位寄存器提供的專用高速連接。

圖:Achronix市場(chǎng)營(yíng)銷副總裁Steve Mensor

Speedcore Gen4的路由架構(gòu)也借由一種獨(dú)立的專用總線路由結(jié)構(gòu)得到了增強(qiáng)。此外,在該路由結(jié)構(gòu)中還有專用的總線多路復(fù)用器,可有效地創(chuàng)建分布式的、運(yùn)行時(shí)可配置的交換網(wǎng)絡(luò)。這為高帶寬和低延遲應(yīng)用提供了最佳的解決方案,并在業(yè)界首次實(shí)現(xiàn)了將網(wǎng)絡(luò)優(yōu)化應(yīng)用于FPGA互連。

圖:Speedcore Gen4架構(gòu)為高性能總線提供了專用路由

易用性也是eFPGA的特色之一,降低了客戶集成FPGA加速器的門檻。客戶通過定制其邏輯、RAM和DSP資源需求,Achronix接下來就會(huì)為其配置滿足其需求的Speedcore IP,Speedcore查找表(LUT)、RAM單元模塊和DSP64單元模塊可以像樂高積木一樣進(jìn)行組合,以便為特定的應(yīng)用創(chuàng)建優(yōu)化的可編程功能。

根據(jù)艾瑞咨詢的數(shù)據(jù),2020年全球人工智能市場(chǎng)規(guī)模約1190億人民幣,未來10年,人工智能將會(huì)是一個(gè)2000億美元的市場(chǎng),空間非常巨大。

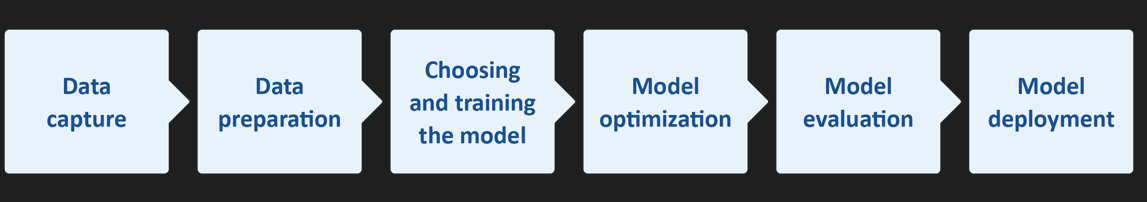

在人工智能領(lǐng)域,傳統(tǒng)的芯片計(jì)算架構(gòu)已無(wú)法支撐深度學(xué)習(xí)等大規(guī)模并行計(jì)算的需求,這就需要新的底層硬件來更好地儲(chǔ)備數(shù)據(jù)、加速計(jì)算過程。其中,F(xiàn)PGA等用于性能加速的硬件、神經(jīng)網(wǎng)絡(luò)芯片、傳感器與中間件,則是支撐人工智能的前提。新的Speedcore Gen4可謂最佳的人工智能/機(jī)器學(xué)習(xí)加速器。Achronix機(jī)器學(xué)習(xí)處理器(MLP)利用了人工智能/機(jī)器學(xué)習(xí)處理的特定屬性,并將這些應(yīng)用的性能提高了300%。這是通過多種架構(gòu)性創(chuàng)新來實(shí)現(xiàn)的,這些創(chuàng)新可以同時(shí)提高每個(gè)時(shí)鐘周期的性能和操作次數(shù)。

MLP是一個(gè)完整的人工智能/機(jī)器學(xué)習(xí)計(jì)算引擎,支持定點(diǎn)和多個(gè)浮點(diǎn)數(shù)格式和精度。每個(gè)機(jī)器學(xué)習(xí)處理器包括一個(gè)循環(huán)寄存器文件,它用來存儲(chǔ)重用的權(quán)重或數(shù)據(jù)。各個(gè)機(jī)器學(xué)習(xí)處理器與相鄰的機(jī)器學(xué)習(xí)處理器單元模塊和更大的存儲(chǔ)單元模塊緊密耦合,以提供最高的處理性能、每秒最高的操作次數(shù)和最低的功率分集。這些機(jī)器學(xué)習(xí)處理器支持各種定點(diǎn)和浮點(diǎn)格式,包括Bfloat16、16位、半精度、24位和單元塊浮點(diǎn)。用戶可以通過為其應(yīng)用選擇最佳精度來實(shí)現(xiàn)精度和性能的均衡。

為了補(bǔ)充機(jī)器學(xué)習(xí)處理器并提高人工智能/機(jī)器學(xué)習(xí)的計(jì)算密度,Speedcore Gen4查找表(LUT)可以實(shí)現(xiàn)比任何獨(dú)立FPGA芯片產(chǎn)品高出兩倍的乘法器。領(lǐng)先的獨(dú)立FPGA芯片在21個(gè)查找表可以中實(shí)現(xiàn)6x6乘法器,而Speedcore Gen4僅需在11個(gè)LUT中就可實(shí)現(xiàn)相同的功能,并可在1 GHz的速率上工作。

GSMA智庫(kù)發(fā)布的最新的全球物聯(lián)網(wǎng)市場(chǎng)報(bào)告顯示,包括連接、應(yīng)用、平臺(tái)與服務(wù),到2025年全球物聯(lián)網(wǎng)市場(chǎng)規(guī)模將達(dá)到1.1萬(wàn)億美元。數(shù)十億物聯(lián)網(wǎng)設(shè)備的出現(xiàn),將給傳統(tǒng)網(wǎng)絡(luò)和計(jì)算基礎(chǔ)設(shè)施帶來壓力。固定和無(wú)線網(wǎng)絡(luò)帶寬的急劇增加,加上處理能力向邊緣等進(jìn)行重新分配。這種新的處理范式意味著每秒將有數(shù)十億到數(shù)萬(wàn)億次的運(yùn)算。傳統(tǒng)云和企業(yè)數(shù)據(jù)中心計(jì)算資源和通信基礎(chǔ)設(shè)施無(wú)法跟上數(shù)據(jù)速率的指數(shù)級(jí)增長(zhǎng)、快速變化的安全協(xié)議、以及許多新的網(wǎng)絡(luò)和連接要求。傳統(tǒng)的多核CPU和SoC無(wú)法在沒有輔助的情況下獨(dú)立滿足這些要求,因而它們需要硬件加速器,通常是可重新編程的硬件加速器,用來預(yù)處理和卸載計(jì)算,以便提高系統(tǒng)的整體計(jì)算性能。經(jīng)過優(yōu)化后的Speedcore Gen4 eFPGA已經(jīng)可以滿足這些應(yīng)用需求。

Steve Mensor告訴21IC記者,現(xiàn)有已量產(chǎn)的Speedcore架構(gòu),Achronix可在6周內(nèi)為客戶配置并提供Speedcore eFPGA IP和支持文件。而最新采用臺(tái)積電7nm工藝節(jié)點(diǎn)的Speedcore Gen4將于2019年上半年投入量產(chǎn),芯片設(shè)計(jì)企業(yè)現(xiàn)已可以聯(lián)系A(chǔ)chronix,以獲得支持其特定需求的Speedcore Gen4實(shí)例。此外Achronix還將于2019年下半年提供用于臺(tái)積電16nm和12nm工藝節(jié)點(diǎn)的Speedcore Gen4 eFPGA IP。據(jù)Steve Mensor預(yù)測(cè),憑借Speedcore Gen4 eFPGA的功耗和成本優(yōu)勢(shì),人工智能/機(jī)器學(xué)習(xí)和高數(shù)據(jù)帶寬應(yīng)用的爆炸式需求將推動(dòng)其在邊緣計(jì)算、5G、網(wǎng)絡(luò)加速和計(jì)算加速等領(lǐng)域被廣泛采納,2019年,eFPGA IP授權(quán)業(yè)務(wù)有望達(dá)到Achronix FPGA整體營(yíng)收的50%甚至更多。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21949瀏覽量

613724 -

硬件加速

+關(guān)注

關(guān)注

0文章

29瀏覽量

11263

發(fā)布評(píng)論請(qǐng)先 登錄

Banana Pi 發(fā)布 BPI-AI2N & BPI-AI2N Carrier,助力 AI 計(jì)算與嵌入式開發(fā)

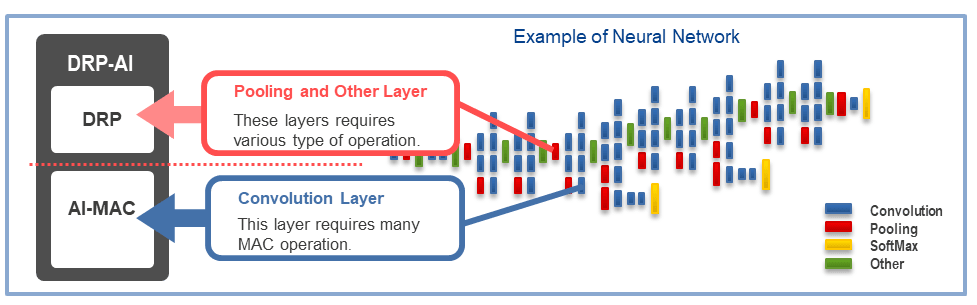

嵌入式AI加速器DRP-AI 詳細(xì)介紹

FPGA+AI王炸組合如何重塑未來世界:看看DeepSeek東方神秘力量如何預(yù)測(cè)......

當(dāng)我問DeepSeek AI爆發(fā)時(shí)代的FPGA是否重要?答案是......

FPGA在AI方面有哪些應(yīng)用

芯華章推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

國(guó)產(chǎn)EDA公司芯華章科技推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

Achronix與BigCat Wireless建立戰(zhàn)略合作伙伴關(guān)系

Achronix Speedcore eFPGA的特性和功能

SiFive發(fā)布MX系列高性能AI加速器IP

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺(tái)

嵌入式系統(tǒng)的未來趨勢(shì)有哪些?

AI普及給嵌入式設(shè)計(jì)人員帶來新挑戰(zhàn)

Achronix新一代嵌入式FPGA IP為AI/ML和網(wǎng)絡(luò)硬件加速應(yīng)用帶來更高性能

Achronix新一代嵌入式FPGA IP為AI/ML和網(wǎng)絡(luò)硬件加速應(yīng)用帶來更高性能

評(píng)論