了解如何為UltraScale +設(shè)計(jì)添加額外的安全級(jí)別。 該視頻演示了如何防止差分功耗分析(DPA),以在比特流配置之上增加額外的安全性。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

賽靈思

+關(guān)注

關(guān)注

33文章

1795瀏覽量

132119 -

功耗

+關(guān)注

關(guān)注

1文章

832瀏覽量

32508 -

設(shè)計(jì)

+關(guān)注

關(guān)注

4文章

820瀏覽量

70372

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

正點(diǎn)原子AU15開(kāi)發(fā)板資料發(fā)布!板載40G QSFP、PCIe3.0x8和FMC LPC等接口,性能強(qiáng)悍!

正點(diǎn)原子AU15開(kāi)發(fā)板資料發(fā)布!板載40G QSFP、PCIe3.0x8和FMC LPC等接口,性能強(qiáng)悍!

正點(diǎn)原子AU15開(kāi)發(fā)板搭載Xilinx Artix UltraScale+ 系列FPGA

發(fā)表于 05-30 17:04

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

。Ultrascale+采用16ns,有3個(gè)系列:Artix,Kintex,Virtex。不僅是工藝制程方面,在其他方面也存在較大改進(jìn),如時(shí)鐘資源與架構(gòu),本文將重點(diǎn)介紹Ultrascale的時(shí)鐘資源與架構(gòu),Ultrascale+

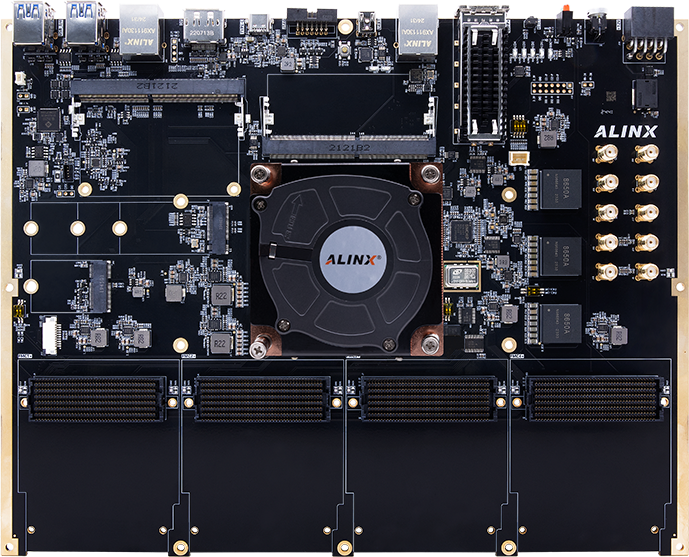

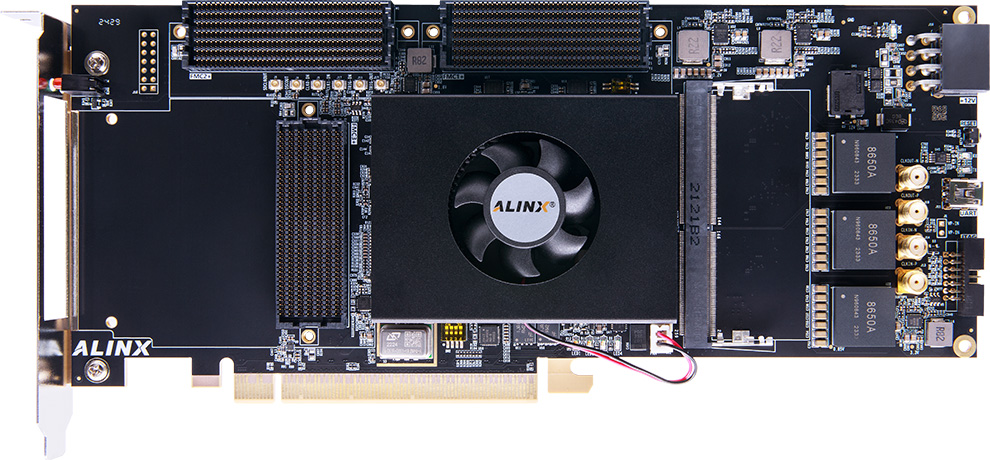

AI 應(yīng)用場(chǎng)景全覆蓋!解碼超高端 VU+ FPGA 開(kāi)發(fā)平臺(tái) AXVU13F

「AXVU13F」 Virtex UltraScale+ XCVU13P + Jetson Orin NX? 繼發(fā)布 AMD Virtex UltraScale+ FPGA PCIE3.0 開(kāi)發(fā)平臺(tái)

Zynq UltraScale+ MPSoC數(shù)據(jù)手冊(cè)

電子發(fā)燒友網(wǎng)站提供《Zynq UltraScale+ MPSoC數(shù)據(jù)手冊(cè).pdf》資料免費(fèi)下載

發(fā)表于 12-30 14:37

?2次下載

ALINX 發(fā)布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 綜合開(kāi)發(fā)平臺(tái)

ALINX 正式發(fā)布 AMD Virtex UltraScale+ 系列 FPGA PCIe 3.0 綜合開(kāi)發(fā)平臺(tái)?AXVU13P! 這款搭載 AMD 16nm 工藝 XCVU13P 芯片的高性能

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評(píng)估套件

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評(píng)估套件可快速啟動(dòng)汽車(chē)、工業(yè)、視頻和通信應(yīng)用設(shè)計(jì)。AMD/Xilinx MPSoC ZCU102 評(píng)估套件采用

LMK04821EVM時(shí)鐘無(wú)法鎖定怎么解決?

用CLKIN0 作輸入,輸入為61.44MHZ 時(shí),LOCK燈是亮,把頻率改為30.72MHZ,同步修改RDIVIDER 值,為什么無(wú)法鎖定,對(duì)CLKIN0 的頻率有嚴(yán)格要求嗎

另外:PLL2

發(fā)表于 11-12 06:46

12G-SDI高清視頻開(kāi)發(fā)案例,讓4K視頻采集更便捷!基于Xilinx MPSoC高性能平臺(tái)

本帖最后由 Tronlong創(chuàng)龍科技 于 2024-10-29 10:35 編輯

本文主要介紹基于Xilinx UltraScale+ MPSoC XCZU7EV的12G-SDI高清視頻開(kāi)發(fā)

發(fā)表于 10-29 10:09

UCD31xx器件中的CPU鎖定機(jī)制

電子發(fā)燒友網(wǎng)站提供《UCD31xx器件中的CPU鎖定機(jī)制.pdf》資料免費(fèi)下載

發(fā)表于 10-15 10:18

?0次下載

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

電子發(fā)燒友網(wǎng)站提供《為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電.pdf》資料免費(fèi)下載

發(fā)表于 09-25 10:54

?0次下載

通過(guò)VCO即時(shí)校準(zhǔn)顯著縮短鎖定時(shí)間

電子發(fā)燒友網(wǎng)站提供《通過(guò)VCO即時(shí)校準(zhǔn)顯著縮短鎖定時(shí)間.pdf》資料免費(fèi)下載

發(fā)表于 08-28 09:32

?0次下載

安川伺服參數(shù)鎖定了怎么解開(kāi)

的注意事項(xiàng)。 1. 了解伺服參數(shù)鎖定的原因 在嘗試解除鎖定之前,首先需要了解導(dǎo)致參數(shù)鎖定的原因。通常,參數(shù)鎖定可能是由于以下原因: 安全原因

一個(gè)更適合工程師和研究僧的FPGA提升課程

設(shè)計(jì);

● UltraFast 設(shè)計(jì)方法;

● 使用UltraScale和UltraScale+架構(gòu)進(jìn)行設(shè)計(jì);

● FPGA 功耗最優(yōu)化;

● 使用 Vivado Design Suite 4

發(fā)表于 06-05 10:09

UltraScale+的安全鎖定

UltraScale+的安全鎖定

評(píng)論