在本演示視頻中,兩個Xilinx FPGA之間以25 Gbps傳輸?shù)臄?shù)據(jù)模式,該模式跨越由Amphenol / FCI PCI Express CEM連接器和跟蹤卡組成的通道。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關注

關注

1645文章

22049瀏覽量

618361 -

連接器

+關注

關注

99文章

15387瀏覽量

140492 -

賽靈思

+關注

關注

33文章

1797瀏覽量

132350

發(fā)布評論請先 登錄

相關推薦

熱點推薦

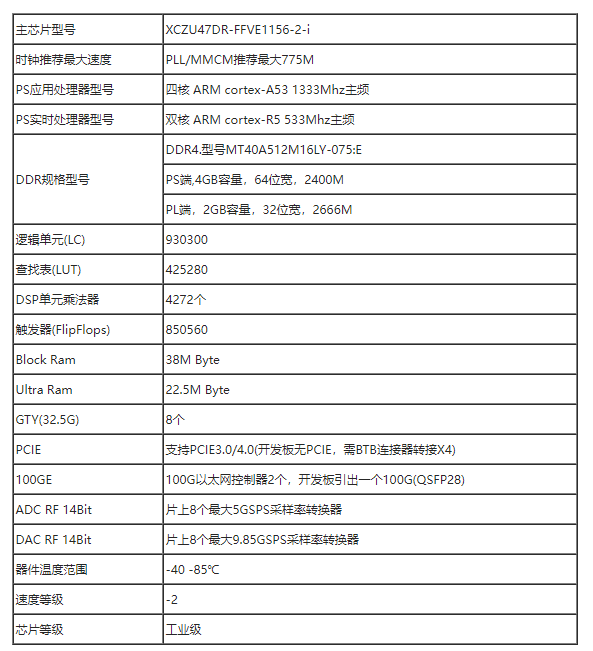

高速數(shù)據(jù)采集卡設計:887-基于 RFSoC 47DR的8T8R 100Gbps 軟件無線電光纖前端卡

一、 板卡概述 ? ? ?板卡使用Xilinx最新的第三代RFSOC系列,單顆芯片包含8路ADC和DAC,64-bit Cortex A53系列4核CPU,Cortex-R5F實時處理核,以及大容量FPGA。對主機接口采用100Gbps

聊聊高速PCB設計100Gbps信號的仿真

這些影響因素會變得更加敏感,所以我們需要花更多的時間來調整這些參數(shù),在25Gbps速率下,長孔和短孔用同樣的尺寸參數(shù)影響不大,但到了100Gbps以上,不同層需要不同的過孔參數(shù),這樣就會多出更多的建模

發(fā)表于 03-17 14:03

ST25DV64與HR11 NFC模塊之間如何實現(xiàn)數(shù)據(jù)傳輸?

主要目的:實現(xiàn)在兩個NFC模塊之間進行數(shù)據(jù)傳輸

在網(wǎng)絡上搜索了一下,大概有以下方式:

1、使用FTM模式;

2、使用NDFF協(xié)議,比較復雜,目前只是想實現(xiàn)簡單的兩個模塊之間讀寫

發(fā)表于 03-10 08:00

xilinx FPGA IOB約束使用以及注意事項

采用了IOB約束,那么就可以保證從IO到達寄存器或者從寄存器到達IO之間的走線延遲最短,同時由于IO的位置是固定的,即存在于IO附近,所以每一次編譯都不會造成輸入或者輸出的時序發(fā)生改變。 二、為什么要使用IOB約束 考慮一個場景,當你用FPGA寫了一個spi模塊,將時鐘、

ADS6149采樣率250Mhz,后級接Xilinx FPGA,輸入1Mhz正弦波,在FPGA接口采樣得到異常采樣點,為什么?

將ADS6149配置為測試模式,配置輸出ramp波形,在FPGA內(nèi)部做ramp數(shù)據(jù)檢測,測試半小時,無錯誤數(shù)據(jù)。

將ADS6149配置為測試模式

發(fā)表于 12-25 07:57

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】+04.SFP之Aurora測試(zmj)

于芯片(FPGA)與芯片(FPGA)之間通信,它用于使用一個或多個收發(fā)器在設備之間傳輸數(shù)據(jù),其連

發(fā)表于 11-14 21:29

25G SFP28 BIDI光模塊介紹

,CPRI/eCPRI,IEEE802.3CC 25GBASE-LR以太網(wǎng)等標準,廣泛應用于數(shù)據(jù)中心、城域網(wǎng)、無線網(wǎng)絡、傳輸網(wǎng)絡等。

產(chǎn)品特征

最大速率高達25.78Gbps,采用

發(fā)表于 11-11 10:23

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

Xilinx7系列FPGA集成了新一代PCI Express集成塊,支持8.0Gb/s數(shù)據(jù)速率的PCI Express 3.0。本文介紹了7系列FP

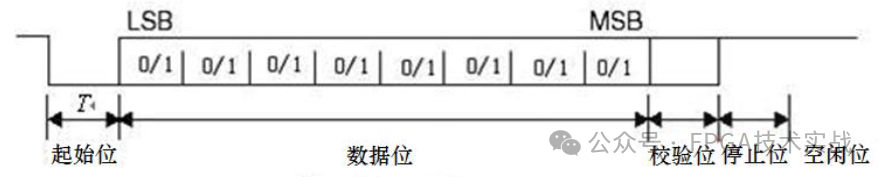

UART通信協(xié)議介紹和數(shù)據(jù)傳輸工作流程

UART是一種通用串行數(shù)據(jù)總線,用于異步通信。該總線雙向通信,可實現(xiàn)全雙工傳輸和接收。UART通常用來實現(xiàn)與PC之間數(shù)據(jù)通信,命令和控制信息的傳輸等。本文我們

明明我說的是25G信號,你卻讓我看12.5G的損耗?

子的:

在截取的這一串數(shù)據(jù)信號中,時鐘信號通過上升和下降沿對數(shù)據(jù)信號進行采樣。對于高速信號來說,每一位的“1”或者“0”的位寬的倒數(shù)就是我們的速率25Gbps。那問題來了,時鐘信號的上升和下降沿都對

發(fā)表于 10-23 09:11

以太網(wǎng)的傳輸介質和工作模式

以太網(wǎng)是一種廣泛應用的局域網(wǎng)(LAN)技術,它通過特定的傳輸介質和工作模式,在多個設備之間高效地傳輸數(shù)據(jù)。本文將從以太網(wǎng)的

SDIO支持哪些數(shù)據(jù)傳輸模式?

1、當 SDIO 時鐘頻率為 25 MHZ 時,總線速度可達多少? 還是 832MBPS?

2、SDIO 支持哪些數(shù)據(jù)傳輸模式? --1 位、2 位、3 位或 4 位?

3、哪個 SDIO 引腳具有中斷功能? --DAT[0]?

發(fā)表于 07-22 06:37

Xilinx 7系列FPGA PCB設計指導

引言: 從本文開始,我們陸續(xù)介紹下有關7系列FPGA通用PCB設計指導,重點介紹在PCB和接口級別做出設計決策的策略。由于FPGA本身也屬于數(shù)字集成電路,文章中的大部分設計策略及概念也

發(fā)表于 07-19 16:56

如何使用FX3同步從屬fifo模式通過FPGA傳輸傳感器數(shù)據(jù)?

我們正試圖使用 FX3 同步從屬 fifo 模式通過 FPGA 傳輸傳感器數(shù)據(jù)。

USB type-C 接口需要選擇一個多路復用器來決定使用哪一邊的 USB。 因此,我們考慮使用 FX

發(fā)表于 07-17 08:04

Xilinx FPGA之間的25Gbps傳輸數(shù)據(jù)模式介紹

Xilinx FPGA之間的25Gbps傳輸數(shù)據(jù)模式介紹

評論