摘要:

針對Canny邊緣檢測算法在實時圖像處理過程中運算耗時長、數據運算量大的缺點,研究了利用Vivado HLS實現Canny邊緣檢測算法的硬件加速方法。該方法由FPGA的邏輯資源生成算法對應的RTL級硬件電路,實現算法硬件加速。實驗結果表明,該方法能快速實時檢測圖像邊緣,有效降低FPGA設計圖像算法的難度,可以應用到實時視頻圖像處理中。

0 引言

邊緣檢測是圖像特征提取、目標識別的基礎,圖像邊緣提取的好壞直接影響后續處理的難易度和準確度。在眾多邊緣提取算法中,Canny邊緣提取算法由于其良好的檢測效果在圖像處理中得到廣泛應用。而現階段的工業視覺檢測中,圖像處理多為PC平臺或者ARM平臺,在這些平臺下,Canny邊緣檢測由于計算量大、耗時長,對平臺本身性能要求也很高。FPGA憑借高速并行性的特性,在進行圖像處理時能很好地保證系統的實時性,因此越來越多開發人員使用FPGA進行圖像處理[1-3]。但在現有的文獻中,有些受FPGA的歷史功能設計局限,過多地關注FPGA底層設計,有些采用中值濾波、改進高斯濾波模板進行Canny邊緣檢測,設計周期較長,硬件加速效果不明顯。武漢科技大學彭習武等采用了Xilinx公司的Vivado HLS(高層次綜合)實現改進的Sobel邊緣檢測[4],取得了較好的實時檢測效果,但需選擇不同的結構元素對不同的目標圖像進行膨脹腐蝕,算法占用硬件資源較多。本文采用Vivado HLS實現Canny邊緣檢測硬件加速實現方法,研究通用性好、設計周期短、硬件資源消耗少的FPGA加速算法。

1 Canny算法基本原理

Canny邊緣檢測[5]算法是CANNY J于1986年提出的,算法目標是在圖像中找到最佳邊緣。其主要步驟為:

(1)圖像高斯濾波:對原始圖像進行高斯濾波,降低輸入圖像中的噪聲對后續圖像處理的干擾,有效提升算法抗噪能力。

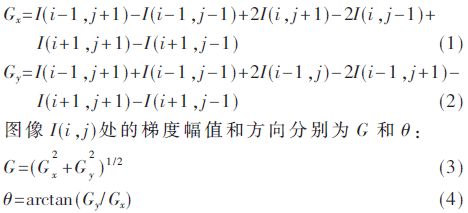

(2)梯度計算:選擇Sobel的水平與垂直方向3×3窗口模板算子與圖像陣列進行計算,原始圖像為I(i,j),得到水平與垂直方向的偏導數,水平、垂直方向梯度偏導數分別為Gx和Gy:

(3)非極大值抑制:遍歷圖像,若像素點的幅值大于其梯度方向的幅值,則可能為邊緣點;否則不是邊緣,對其進行抑制。

(4)雙閾值處理:通過設定閾值Th、Tl(一般情況下Tl=0.4Th),抑制后的圖像像素梯度值大于Th的是邊緣點,小于Tl的一定不是邊緣點,如果處于兩者之間,判斷當前像素的鄰域像素中是否有邊緣點,若有,則為邊緣點,否則就不是邊緣。

2 Vivado HLS實現方式

Vivado HLS是Xilinx公司推出的加速數字系統設計開發工具,直接使用C、C++或SystemC開發的高層描述來綜合數字硬件,替代用VHDL或Verilog實現FPGA硬件設計[6],實現設計的功能和硬件分離,不需要關心低層次具體細節,具有很強的靈活性,有效降低數字系統設計開發周期。Vivado HLS在算法優化指標和FPGA硬件設計方式指標是一致的:(1)面積,算法硬件資源使用的數量;(2)速度,硬件電路處理數據的速率。一般的設計是對兩者之間的特殊需求進行優化,得到合理的方案。

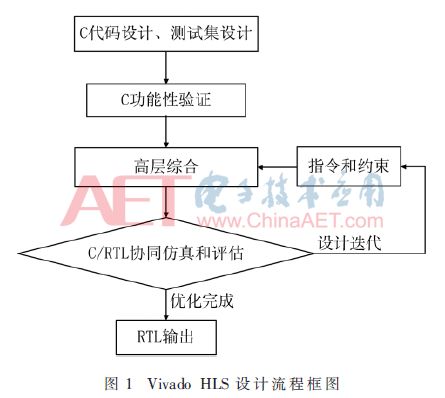

2.1 Vivado HLS設計流程

Vivado HLS設計流程如圖1所示。C代碼設計和C測試集設計是HLS設計流程的輸入;C功能性驗證能確保代碼功能的完整性;高層綜合能產生所需的各個設計文件;C/RTL協同仿真可以進行預期值與輸出的對比;設計迭代是通過不斷地調整指令得到預期需要的優化設計,在不改變C代碼的情況下,由優化指令轉化成小面積高吞吐率的RTL電路[7];最后RTL電路被綜合成FPGA邏輯模塊。

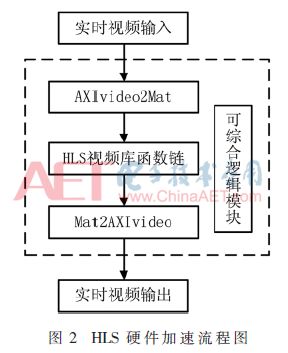

2.2 Vivado HLS圖像實時加速

Vivado HLS圖像實時加速設計的方式如圖2所示。

視頻流進入FPGA后,由AXI4-Stream協議將數據流轉換為HLS視頻庫下的hls::Mat格式,在進行對應的圖像FPGA加速處理后,將hls::Mat格式重新轉換為AXI4-Stream數據流。

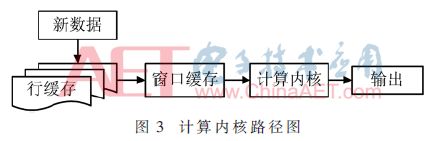

Vivado HLS提供了以下幾個方面功能對圖像視頻處理建模[8]:(1)內存行緩存(Memory Line Buffer);(2)內存窗口緩存(Memory Window Buffer);(3)視頻數據支持格式類型;(4)視頻函數庫。HLS內存行緩存實質是能存儲多行像素數據的多維移位寄存器[9],而窗口緩存是行緩存的一個子集,這兩種存儲結構一般被綜合為Block RAM,并且行緩存的寬度決定了圖像算法能進行硬件加速的最大圖像寬度。Vivado HLS對一幀圖像像素的遍歷是通過創建上述兩種緩存實現的,圖3是遍歷圖像像素的計算內核路徑。Vivado HLS下圖像處理基于視頻流訪問,因此,基于隨機存儲訪問的圖像處理方式需要進行轉換,綜合為FPGA處理下的圖像數據流處理方式,實現圖像算法的硬件加速。

3 Vivado HLS實現Canny邊緣檢測

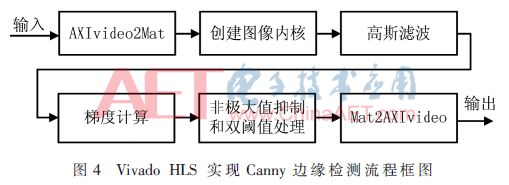

根據Vivado HLS設計流程,Canny邊緣檢測的硬件加速實現流程如圖4所示。

3.1 圖像數據流輸入

圖像數據通過AXI4-Stream輸入到Canny邊緣檢測IP,由AXIvideo2Mat將數據流轉換為hls::Mat類型,完成Canny邊緣檢測IP的硬件加速設計。

3.2 圖像計算內核創建

創建類型為hls::Window、大小為1×3和3×3的窗口緩存,以及類型為hls::LineBuffer、大小為3×1 920的行緩存。將圖像像素寫入第一行行緩存,每寫入一次新的圖像數據,讀出對應行緩存的數據到1×3的窗口緩存,同時3×3的窗口緩存右移,把1×3的窗口緩存數據寫入3×3的窗口緩存的第一列,每一行行緩存寫滿時,當前行緩存數據移位寫入下一行。通過上述方式,由3×3窗口緩存構成的計算內核完成圖像的遍歷。

3.3 圖像濾波

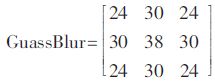

考慮到濾波器窗口太大圖像邊緣會被過度平滑,選擇高斯濾波器為3×3的濾波窗口,σ值為1.5,由于模版系數歸一化后均為小數,對于FPGA而言,需要增加硬件資源消耗實現浮點類型,因此,將模板系數全部乘以256后取整,對于實際處理而言,這種近似值產生的誤差不會對濾波效果產生很大影響,實際模板系數為:

將濾波模板GuassBlur與計算內核進行卷積,卷積后的結果右移8位(除以256),移位操作不會消耗FPGA的DSP資源,節約了FPGA資源,由上述的移位運算后,完成圖像數據的高斯濾波。

3.4 梯度計算

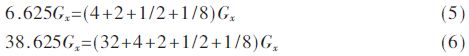

創建3×3濾波后的圖像計算內核窗口,將計算內核分別與Sobel的水平與垂直方向3×3窗口算子卷積,求得水平、垂直方向梯度偏導數Gx和Gy大小,由于硬件實現平方根需要的資源較多,故通過Gx和Gy的絕對值之和求梯度G的幅值。對于梯度的方向θ=arctan(Gy/Gx),硬件實現較為困難,需要消耗很多硬件資源,一般是比較像素領域窗口,對于3×3窗口而言,求其領域8個方向,由于對稱性,只需要求得4個方向,0°、45°、90°和135°,即把梯度Gy的值與Gxtan22.5°和Gxtan67.5°比較,同時判斷GyGx乘積的正負性,可求得梯度的方向θ值的大小。為節約硬件資源可以采取對Gy左移4位,Gxtan22.5°左移4位,取值約為6.625Gx,Gxtan67.5°左移4位,約為38.625Gx,即:

通過簡單移位判斷大小和正負性,得到梯度方向θ的近似值。

3.5 非極大值抑制和雙閾值處理

定義位寬為2位的寄存器,4個方向對應寄存器值0,1,2,3,將該寄存器與存儲梯度值G寄存器組合輸出到新創建的圖像行緩存,并創建新的3×3計算內核,通過計算內核窗口判斷圖像數據的方向,進行極大值抑制。計算內核中心點與對應梯度方向的像素點、高閾值Th、低閾值Tl進行比較,若計算內核中心點最大則為圖像強邊緣點;若計算內核中心點大于梯度方向,處于Tl和Th之間,為弱邊緣點;其他情況均不是圖像的邊緣點。

創建新的行緩存寫入上述圖像邊緣數據,由新的3×3計算內核做進一步處理:若計算內核中心點是強邊緣點輸出255;若計算內核是弱邊緣點,判斷其八鄰域是否存在強邊緣點,不存在強邊緣點則輸出0,存在則輸出255,同時把中心點值改變為強邊緣點值;其他情況直接輸出0。

3.6 圖像數據流輸出

處理后的數據通過AXIvideo2Mat將hls::Mat格式重新轉為AXI4-Stream數據流,圖像數據通過上述的處理完成Canny邊緣檢測的硬件加速。

3.7 指令優化迭代

采用Vivado HLS提供的模塊優化指令如inline、pipeline、dataflow以及對循環展開的unroll等,完成算法硬件加速的優化,達到硬件資源消耗和算法處理速度之間的平衡。一般的優化為串行方式和并行方式兩種,串行優化方式使用硬件資源少,并行優化方式處理速率高[4]。為獲得良好的硬件加速效果,選擇并行優化方式,具體措施為:(1)對模塊內部循環展開;(2)循環、模塊內部流水化處理;(3)模塊之間流水化處理。為驗證本方案的資源占用情況,選取文獻[4]進行對比分析,在保證運算速度基本相同的情況下,選取并行方案對硬件資源使用情況列于表1。從表1可以看出,本文邊緣檢測算法的硬件資源使用少。

4 邊緣檢測效果與速度驗證

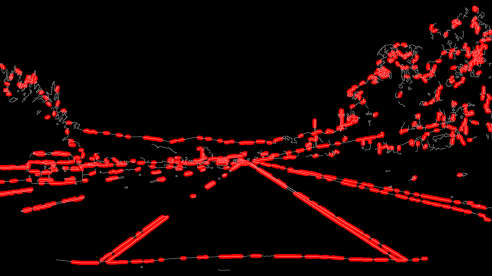

以Zedboard開發板為算法驗證平臺,開發板FPGA芯片型號為xc7z020484-1,圖像由開發板PS端輸入到FPGA算法IP中,通過HDMI將原始圖像和處理后圖像輸出到顯示屏。

圖5(a)為512×512測試圖像;圖5(b)為PC進行的Canny邊緣檢測圖像;圖5(c)為FPGA驗證的圖像;PC的主頻為2.3 GHz,對應的圖5(b)處理時間約為10 ms左右;FPGA的時鐘頻率為100 MHz,圖5(c)處理時間約為3 ms。

由圖5(c)和圖5(b)處理時間的對比可知,圖5(c)算法處理時間不到圖5(b)的1/3,說明加速效果明顯。從文獻[1]中可知,在相同系統時鐘下處理512×512的圖像,時間約為20 ms,遠小于圖5(c)的處理速度。因此,Vivado HLS實現的Canny邊緣檢測算法能在較復雜的情況下檢測到圖像邊緣,且運算速度快。

5 結論

由Vivado HLS進行FPGA圖像算法硬件加速設計方式,既避免了傳統FPGA圖像算法開發中過于關注底層細節,又能有效地縮短開發周期。通過仿真與FPGA驗證,采用Vivado HLS實現的Canny邊緣檢測算法能在較復雜的情況下檢測到圖像邊緣,運算速度快,資源消耗少,可以應用到實時視覺檢測中。

-

圖像處理

+關注

關注

27文章

1325瀏覽量

57709 -

邊緣檢測

+關注

關注

0文章

94瀏覽量

18375

原文標題:【學術論文】基于Vivado HLS的Canny算法實時加速設計

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于Canny邊緣檢測算子的圖像檢索算法

用OpenCV和Vivado HLS加速基于Zynq SoC的嵌入式視覺應用開發

【Z-turn Board試用體驗】+ 基于Z-turn的圖像邊緣檢測系統(三)

關于canny算子邊緣檢測的問題

【KV260視覺入門套件試用體驗】 硬件加速之—使用PL加速FFT運算(Vivado)

【KV260視覺入門套件試用體驗】硬件加速之—使用PL加速矩陣乘法運算(Vitis HLS)

基于Canny 法的紅外小目標邊緣檢測方法

Canny圖像算法仿真驗證原理與實現

python中用Canny邊緣檢測和霍夫變實現車道線檢測方法

Vivado HLS實現Canny邊緣檢測硬件加速實現方法

Vivado HLS實現Canny邊緣檢測硬件加速實現方法

評論