1、引言

現代通信系統要求通信距離遠、通信容量大、傳輸質量好。作為其關鍵技術之一的調制解調技術一直是人們研究的一個重要方向。從模擬調制到數字調制,從二進制發展到多進制調制,雖然調制方式多種多樣,但都是朝著使通信系統更高速、更可靠的方向發展。一個系統的通信質量,很大程度上依賴于所采用的調制方式。因此,對調制方式的研究,將直接決定著通信系統質量的好壞。

復雜可編程邏輯器件(CPLD)結合了專用集成電路和DSP的優勢,既具有很高的處理速度,又具有一定的靈活性。因此,基于CPLD的數字調制系統的研究具有重要的實際意義。本文論述了如何用CPLD實現PSK數字調制系統的方法,其實現步驟包括:1.研究PSK調制系統的原理及設計方法;2.根據各個系統的總體功能與硬件特點,設計總體框圖;3.根據VHDL語言特點,對系統進行VHDL建模;4.根據VHDL模型,進行具體VHDL語言程序設計;5.對設計的程序進行波形仿真與硬件調試。

2、調制解調系統的原理

載有基帶信號的高頻正弦波信號稱為載波,數學上準確表示正弦波時,經常采用振幅A、角頻率 和相位 三要素,即

y(t)=A cos( t + ) (2-1)

根據基帶信號的值,改變三要素中的任何一種,就有了3種基本的調制方式:數字信號對載波振幅調制稱為振幅鍵控,即ASK(Amplitude Shift Keying);對載波頻率調制稱為頻移鍵控,即FSK(Frequency Shift Keying);對載波相位調制稱為相移鍵控(相位鍵控),即PSK(Phase Shift Keying)。

由于PSK系統抗噪聲性能優于ASK和FSK,而且頻帶利用率較高,所以,在中、高速數字通信中被廣泛采用。

本文只對PSK調制方式加以論述。

3、系統的總體方案設計

3.1 CPSK系統設計

CPSK由發送端的調制模塊與接收端的解調模塊構成,其系統框圖如圖3-1所示。在發送端,對于調制模塊,首先產生兩種不同相位的載波信號f1和f2,再通過一個二選一選通開關來選擇載波信號,其中具體的載波信號由輸入的基帶信號來決定。這些信號處理都在CPLD中實現,輸出的即為CPSK調制信號,最后通過信道發送到接收端。對于解調模塊,調制信號先由位同步提取電路提取出載波同步信號,然后由載波同步信號來控制計數器的啟動與停止,分別對調制信號來計數,最后通過一個判決電路來判斷輸入的調制信號是‘0’ 還是‘1’,輸出的即為解調的基帶信號。

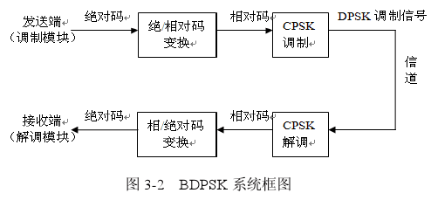

3.2 DPSK系統設計

DPSK信號應用較多,但由于它的調制規律比較復雜,難以直接產生,目前DPSK信號的產生較多地采用碼變換加CPSK調制而獲得。這種方法是把原基帶信號經過絕對碼——相對碼變換后,用相對碼進行CPSK調制,其輸出便是DPSK信號。同樣,對于DPSK信號的解調,則要經過相對碼——絕對碼變換。其系統框圖如圖3-2所示。

4 、基于VHDL的PSK系統電路設計及實現

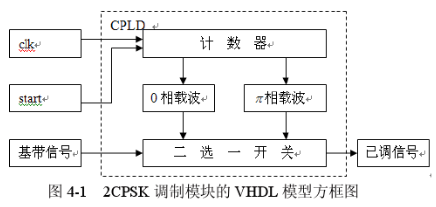

4.1 2CPSK調制模塊

2CPSK調制模塊的VHDL模型方框圖如圖4-1所示,其模型主要由計數器和二選一開關等組成。計數器對外部時鐘信號進行分頻與計數,并輸出兩路相位相反的數字載波信號;二選一開關的功能是:在基帶信號的控制下,對兩路載波信號進行選通,輸出的信號即為CPSK信號。圖中沒有包括模擬電路部分,輸出信號為數字信號。

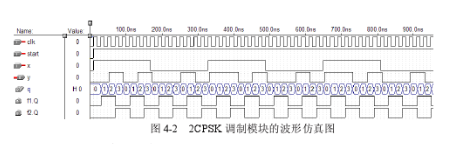

其波形仿真圖如圖4-2所示。其中載波信號f1、f2是通過系統時鐘clk分頻得到,且滯后系統時鐘一個clk周期;調制輸出信號y滯后載波一個clk周期,滯后系統時鐘2個clk周期。

圖4-2 2CPSK調制模塊的波形仿真圖

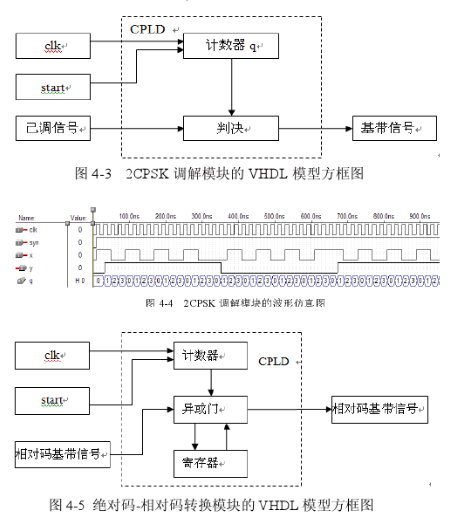

2CPSK解調模塊的VHDL模型方框圖如圖4-3所示。圖中的計數器q輸出與發端同步的0向數字載波。判決器的工作原理是:把計數器輸出的0相載波與數字CPSK信號中的載波進行邏輯“與”運算,當兩比較信號在判決時刻都為“1”時,輸出為“1”,否則輸出為“0”,以實現解調的目的。圖中沒有包含模擬電路部分,調制信號為數字信號。

其波形仿真圖如圖4-4所示。當q=0時,根據x的電平來進行對相位的判決;其中輸出信號y滯后輸入信號x一個clk周期。

4.3 絕對碼-相對碼轉換模塊

絕對碼——相對碼之間的關系為

由此,可得到絕對碼—相對碼轉換模塊的VHDL模型方框圖,如圖4-5所示。圖中的計數器與圖4-3中的計數器相同,異或門與寄存器共同完成絕/相變換功能。

相對碼—絕對碼轉換模塊與此類似,此處就不加以論述。

5、系統調試總結

本課題研究并追蹤了通信領域和EDA設計領域的兩項關鍵技術——調制解調技術和可編程邏輯技術,所有設計工作都是在一塊CPLD實驗開發板上完成的,選用了Altera公司型號為EPM7128SLC84-7作為主芯片的。其中輸入信號由單片機提供,經過CPLD處理后,輸出信號的波形可通過示波器觀察。但由于調制系統與解調系統的測試是分開進行的,這樣勢必有不直觀性,并且未能考慮到實際

系統中的不定因素。而以上這些,是本設計將來要進一步改善與發展的地方。

論文創新點:論文采用自上而下的開發方式,通過復雜可編程邏輯器件(CPLD)設計實現調制解調系統,以直接提高通信系統質量。

責任編輯:gt

-

cpld

+關注

關注

32文章

1257瀏覽量

171500 -

仿真

+關注

關注

52文章

4286瀏覽量

135841

發布評論請先 登錄

可編程邏輯器件

PLD可編程邏輯器件

可編程邏輯器件基礎及應用實驗指導書

什么是PLD(可編程邏輯器件)

基于可編程邏輯器件的數字電路設計

基于可編程邏輯器件的PSK數字調制系統的設計及波形仿真與硬件調試

基于可編程邏輯器件的PSK數字調制系統的設計及波形仿真與硬件調試

評論