引言:

隨著集成電路深亞微米時代的到來,集成電路的規模不斷擴大,促進了系統級芯片 SoC(Systems-on-a-Chip)的發展和應用。通常一個 SoC芯片的規模在幾百萬門至幾千萬門左右,面對如此高的復雜度,驗證成為 SoC設計中最困難、最具挑戰性的課題之一。VMM(Verification Methodology Manual)驗證方法學采用 SystemVerilog語言,引入了斷言、抽象化、自動化及重用機制,指導驗證工程師搭建基于事務的可重用的層次化驗證平臺,可以很容易地實現定向測試、隨機測試、數據自檢查等功能,減少了測試案例的復雜度,提高了驗證生產率,減少了總的驗證代碼量,縮短了產品的面市時間。

1基于事務的驗證

基于事務的驗證是當前采用的主要驗證技術。簡單來說事務就是在接口上的操作。事務可以是抽象的和高層次的,例如可靠地發送一個TCP包,也可以是物理層面上的,例如在APB內連接上的寫周期。基于事務的驗證讓用戶不必關注底層的細節,在抽象級別更高的事務級上進行驗證,從而提高了驗證效率。

驗證環境中的組件稱為事務處理器。它是一個靜態的對象,它自主地生成、處理或者監視事務。傳統的總線功能模型即是一種低層次的事務處理器,它將事務級激勵轉換成被測設計對象接口上的引腳信號躍變或者相反。而更高層次的事務處理器只有事務級接口。事務處理器根據設計對象中所使用的協議來處理事務,被測設計對象所產生的響應從引腳信號的躍變轉換回事務級的響應形式。這樣就可以做到在事務級上核對響應是否正確,檢查出響應不相符的時候,就進一步在信號/引腳級上加以查看,從而將錯誤定位出來。

2 VMM驗證方法學

VMM是一種基于 SystemVerilog的驗證方法學。它最大程序地利用了 SystemVerilog的面向對象編程的優點,通過一系列機制提高了驗證的生產率。

2.1層次化驗證模型

VMM采用了易于驗證重用的分層式測試平臺結構。每一層即建立在其他層之上的又具有一定的獨立性,使得驗證平臺在不同的項目之間使用時,即使改變某一層的功能也不會影響其他層的重用,這樣就大大提高了驗證的重用性。

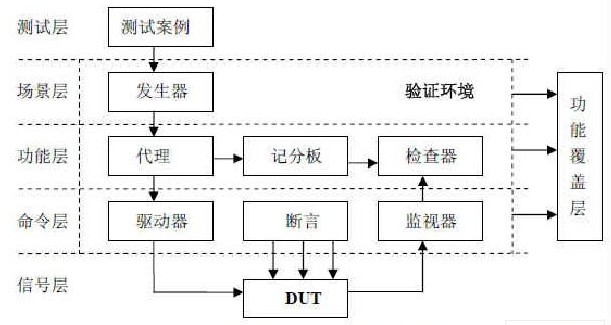

可以看出 VMM推薦的層次化驗證平臺從底至上被分成信號層、命令層、功能層、場景層以及測試層。其中的驗證組件包括發生器、代理、驅動器、監視器、檢查器、記分板以及斷言。

信號層包括待測設計DUT與接口。命令層在信號層之上,向下通過信號層接口與待測設計相連,向上通過事務級通道與功能層通信,一般包括驅動器(Driver)、監視器(Monitor)和斷言(Assertion)。驅動器將來自上層的事務轉化為信號級激勵輸入給DUT,監視器用來監視接口信號的變化并轉化為事務傳遞給上層的檢查器。功能層位于命令層之上,是高層次操作的抽象,相互之間通過事務級通道通信。這一層主要包括代理(Agent)、檢查器(Checker)和記分板(Scoreboard)。代理的作用是接收上層傳來的高層事務,如DMA的讀寫等,并且將這些高層事務轉換成單獨的命令向驅動器提供。驅動器在接收到代理發出的命令后,就會生成相應的激勵數據。記分板用來動態預測設計的響應,施加給DUT的激勵同時施加給記分板,記分板中的轉換函數把輸入的激勵全部轉換成最后響應的形式,并保存在數據結構中,以傳遞給檢查器,記分板還對所有的事務進行紀錄與統計,記錄執行的事務個數,成功失敗的事務個數,是否某一事務被遺漏等。檢查器通過將監視器傳來的數據與記分板中存儲的預測響應進行比較來判斷待測功能是否正確。場景(Scenario)層在功能層之上,主要是用來生成具有一定關系的隨機事務的序列。最上層是測試層,他被用來配置不同的測試案例,定義不同的約束條件。在整個驗證工程中,功能覆蓋率由仿真工具自動生成,測試者根據功能覆蓋率來調整測試平臺,修改測試案例直到覆蓋率達到1O0% ,便可以認為驗證過程結束。

為了充分利用SystemVerilog語言面向對象編程的優點,上述驗證組件都用類(class)來實現,以提高可重用性,整個驗證平臺具有統一的框架,結構也變得清晰,更容易維護。

2.2 提高驗證生產率的機制 VMM方法學通過 4個不同的機制提高了項目驗證的生產率。這四個機制為別為 :斷言、抽象化、自動化和重用。

斷言是檢查待測設計中信號行為是否正確的觀察器,它是用描述性語言來實現的。通過在設計模塊內部與其對外接口的關鍵位置上設置功能檢查,不需要編寫獨立的測試代碼,便能從測試平臺的外觀察到這些關鍵監視點所發生的情況,可以有效地提高觀察和定位設計錯誤的能力。

傳統的總線功能模型使的我們很難添加或結合新的協議層,而事務處理器的層次化形成了遞歸層次的抽象化,通過事務處理器的層次化來突破總線功能模型的限制。

在驗證中, 需要產生激勵來驅動設計。在時間有限的仿真過程中, 定向測試只能驗證芯片的典型行為 , 而不能驗證所有可能的行為, 這是定向測試的主要缺陷。而隨機化激勵可以僅用幾行代碼就能產生大量的激勵數據 , 通過為設計提供隨機激勵信號來擴大驗證的測試空間。當隨機激勵源不能生成所需的激勵信號時,或者所需的激勵不能用無側重的隨機信號源來產生時,驗證者可以對隨機化過程施加約束,讓它生成的隨機化的激勵更多地落在我們感興趣的區域或者邊界內, 可更快地達到功能覆蓋率的要求。

VMM對驗證環境的層次進行了明確的定義,反映了設計所處理數據不同的抽象層次,每一層建立在其他層之上又具有一定的獨立性,即使改變某一層的功能也不會影響其他層的重用,這樣就大大提高了驗證的重用性,可有效減少要編寫的測試案例的復雜度,驗證環境無須修改即可被盡可能多的測試案例重用,避免了重復編寫功能相同的模塊。

3 應用實例

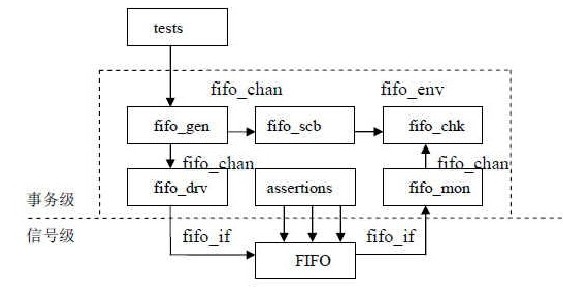

下面通過一個例子來介紹如何用 VMM建立基于事務的層次化驗證平臺,待測模塊 DUT為一個 FIFO。驗證平臺的頂層結構如圖 2所示:

由于設計較為簡單,因此這里未實現場景層的功能模塊。上圖中各個驗證組件都是用類實現的。下面自上而下介紹各個驗證組件的功能與實現。

(1) 事務定義 fifo_tr

事務 fifo_tr繼承自 VMM的基類 vmm_data,因此也繼承了 vmm_data定義的一些方法,如 copy(), compare()等。fifo_tr包括兩個成員變量 kind和 data,前者定義事務的類型是讀還是寫,后者定義讀寫的數據。

(2) 事務通道 fifo_chan

fifo_chan由 VMM定義的宏 `vmm_channel()產生,用來在事務級驗證組件之間傳輸特定的事務。與 SystemVerilog定義的 mailbox結構相比,通道是強類型的,即每種通道只能傳輸特定的事務,避免了錯誤情況的發生。

(3) 接口 fifo_if

fifo_if是驅動器與 FIFO之間的通信接口,它封裝了 FIFO的 Pin,屬于信號層,驅動器通過接口來將激勵輸入給 DUT。

(4) 發生器 fifo_gen

fifo_gen繼承自 VMM的基類 vmm_xactor,它的核心是一個無限循環,用來產生隨機的事務,如讀事務或寫事務,并將該事務通過通道傳輸給驅動器 fifo_drv.

(5) 驅動器 fifo_drv

fifo_drv繼承自 VMM的基類 vmm_xactor,它的功能是接收來自上層發生器 fifo_gen的事務 fifo_xactn,通過分析將其轉化為信號級的信號,作為激勵輸入給待測設計 FIFO,它的構造器包含兩個重要的參數,一個是輸入通道,用來與發生器通信,另一個是輸出接口,用來與 FIFO通信。

(6) 監視器 fifo_mon

fifo_mon繼承自 VMM的基類 vmm_xactor,它的功能是監視 FIFO的信號變化,將設計的實際響應傳遞給檢查器 fifo_chk.與驅動器類似,它的構造器也包含兩個重要的參數,一個是輸入接口,用來與 FIFO相連,監視接口信號的變化,另一個是事務級通道,用來與檢查器通信。

(7) 檢查器 fifo_chk

fifo_chk繼承自 VMM的基類 vmm_xactor,用來檢查事務是否正確得到執行。具體是將監視器傳來的信息與記分板傳來的預測結果進行比較以判斷待測功能的正確性。

(8) 計分板 fifo_scb

計分板繼承自 VMM的基類 vmm_xactor,用來對輸入激勵產生預測響應,并對已發生的事務進行紀錄與統計,比如總共進行了多少個讀事務或寫事務,哪些已經完成,哪些被掛起,哪條事務正確的得到執行,哪條事務執行過程中出錯了等等。

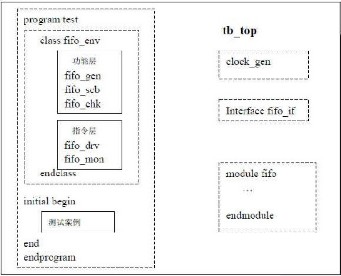

(9) 斷言 assertions 斷言用來檢驗 FIFO的違例情況,如在滿的情況下寫 FIFO,空的情況下讀 FIFO等,這些可以通過斷言檢查出來。以上介紹的驗證組件組成的驗證平臺的框架可用圖 3表示如下 :

頂層模塊 tb_top由 DUT、測試程序 (program)、接口與時鐘發生器組成。測試程序中例化了驗證環境 fifo_env,驗證環境將所有必需的事務處理器進行例化,測試案例只用程序(program)塊中的一個 initial塊來實現,這樣做可以避免設計、斷言和驗證環境出現競爭冒險,并且只使用一個 initial塊使得測試案例的執行是單線程的,這樣可以更容易的理解所要完成的測試案例的每個步驟。

4 總結

在越來越高的抽象層次上進行驗證是歷史不斷發展的趨勢。本文以 FIFO驗證平臺為例運用面向對象的思想介紹了怎樣利用VMM驗證方法學建立基于事務的層次化驗證平臺,簡單介紹了每個層次驗證組件的功能與實現,給出了總的驗證平臺的框架。該驗證平臺具有很高的重用性,增強了程序可讀性,降低了驗證平臺的維護成本、體現了VMM驗證方法學的優越性。

-

處理器

+關注

關注

68文章

19807瀏覽量

233558 -

協議

+關注

關注

2文章

614瀏覽量

39829 -

語言

+關注

關注

1文章

97瀏覽量

24438

發布評論請先 登錄

RAKsmart服務器SEO優化優勢分析

芯片失效分析的方法和流程

渦扇發動機吞鳥適航完整性評定方法及驗證

Triton編譯器的優勢與劣勢分析

英諾達發布全新靜態驗證產品,提升芯片設計效率

遙感影像分析的方法與步驟

材料失效分析方法匯總

無損檢測方法的種類與優勢

SSR的優勢和劣勢分析

想要驗證ADC,DAC的SNR和DR指標,可否推薦實際相應的測試方法?

基于場景的自動駕駛驗證策略

Lint靜態驗證工具如何助力IC設計

機器學習中的交叉驗證方法

國產光電耦合器優勢分析

大規模 SoC 原型驗證面臨哪些技術挑戰?

VMM驗證方法學的優勢及應用案例分析

VMM驗證方法學的優勢及應用案例分析

評論