引言

WiMAX ( Wordwide Interoperability for Mi-crowave Access)是代表空中接口滿足IEEE 802.16標準的寬帶無線通信系統(tǒng)。其中IEEE標準在2004年定義了空中接口的物理層(PHY),即802.16d協(xié)議。該協(xié)議規(guī)定數據傳輸采用突發(fā)模式,調制采用OFDM技術。在接收端,為了正確解調,必須找到符號的起始位置,因此,必須進行定時估計。如果定時不正確,就可能引起嚴重的碼間干擾。由于頻偏估計是在定時估計之后進行,如果定時估計不準確,也會影響頻偏的估計性能,從而導致整個OFDM系統(tǒng)性能下降。因此,必須在短時間內對接收數據進行快速準確的定時同步。

目前常用的定時算法多采用計算序列的相關性。由于計算復雜,其硬件資源消耗非常龐大,所以,目前OFDM系統(tǒng)中的同步算法以軟件方法為主,已有的硬件方法由于消耗資源太大而無法將同步模塊和接收部分的其他模塊集成在一片芯片中。本文參考IEEE 802.16d物理層幀結構,提出了一種低復雜度的幀同步和定時同步聯合算法,該算法可在FPGA上利用較少資源來實現。

1 OFDM中的符號定時同步算法

對于定時同步算法的研究,總體上可以分為兩類:第一類是依靠OFDM固有的結構,如利用OFDM符號周期性前綴CP的方法,這通常被稱作循環(huán)前綴同步方法;第二類是利用OFDM中插入導頻或者訓練符號的方法。在兩類同步方法中,第一類方法中最具代表性的是Beek提出的最大似然估計法,其優(yōu)點是不需要額外的開銷,可以提高通信的效率,但其缺點是估計的時間較長,而且對頻偏和噪聲比較敏感;第二類方法中最具代表性的是Schmidl和Cox提出的利用PN序列相關性的SCA算法,這一種算法受頻偏的影響較小,而且估計的時間相對比較短,非常適合用于突發(fā)通信系統(tǒng)。

2 適合802.16d的定時同步算法

IEEE 802.16d定義了一組特殊的訓練符號,以用于同步和信道估計。這組特殊的訓練符號包括短訓練序列和長訓練序列兩部分,其中短訓練序列包括4個重復的64點數據加上循環(huán)前綴(CP);長訓練序列包括兩個重復的128點數據加上循環(huán)前綴。在發(fā)射端,若干OFDM符號再加上短訓練序列和長訓練序列,所構成的幀頭經過發(fā)送濾波器和A/D轉換,再通過上變頻后,即可發(fā)送到信道中。而在接收端,則利用幀頭的訓練序列來進行同步。為了使定時同步不受頻偏的影響,同時可以在較短時間內完成,本文采用SCA算法。該算法又可細分為延時自相關算法和本地序列互相關算法兩類。

2.1 延時自相關法

通常選用短訓練序列來進行定時同步。假設接收到的基帶數字序列為rn,n是該序列的序號,然后將接收序列經過兩個滑動窗口R和P,其中R是接收信號和接收信號延時的互相關系數,P是互相關系數窗口期間接收信號的能量,此窗口的值可用于判決的歸一化,它和接收功率的絕對值是獨立的,其公式如下:

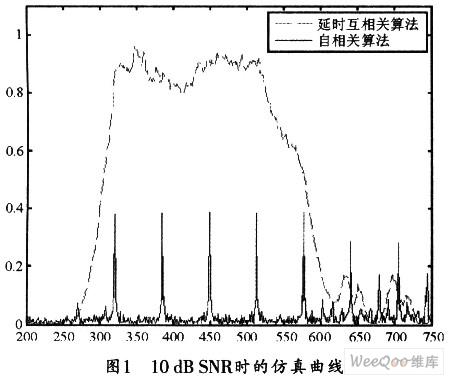

式中,N為窗口長度,N=64,即短訓練序列的周期,d在窗內滑動時,可同時計算M(n)的值。當沒有包含前導字結構的信號出現時,得到的M(n)值通常非常小(遠小于1),而當有前導字結構的信號出現時,相應的M(n)值迅速升高,并將出現一個臺階,對應的峰值接近于1。由于M(n)值升高需要一個時間范圍,因此該算法并不能精確定時,只適合粗略的檢測幀是否到達。圖1所示的虛線即表示信號出現時M(n)曲線的變化情況。

2.2 互相關法

由于IEEE 802.16d協(xié)議中的前導字具有良好的互相關特性,故可用已知的訓練序列和接收序列做滑動互相關。當已知的訓練序列和接收的訓練序列恰好對齊時,便會產生一個峰值,峰值對準的位置正是訓練符號的起始點。因此,可以通過尋找互相關的峰值位置來做精確的定時同步。算法公式如下:

式中,c(n)為短訓練符號在本地的復制樣本,N為短訓練符號的樣值點數。當已知的訓練序列和接收訓練序列恰好對齊時,也會產生一個峰值,其仿真曲線如圖1中的實曲線所示。該算法的缺點是易受頻偏的影響。

根據以上分析,并從算法性能上考慮,若采用延遲自相關法,幀到達時會出現一個峰值平臺,該方法并不能確定幀到達的準確時刻;而采用與本地序列互相關算法又容易受到頻偏的影響而導致定時偏差。

3 算法改進

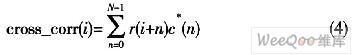

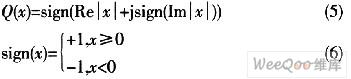

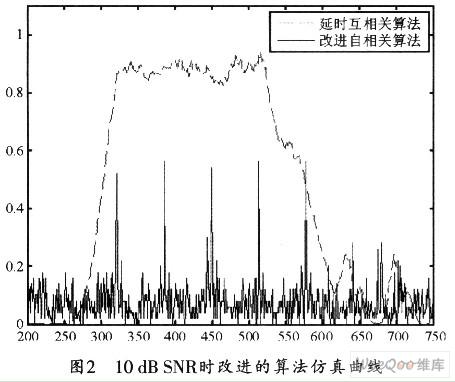

針對上述算法的不足,可對其加以改進,以保證同時具有良好的性能和硬件實現的可行性。改進算法是將兩種算法結合起來進行聯合估計,首先確定一個幀到達的大致平臺,再在這個平臺內找到互相關峰值,如果各個峰值間隔相等,那么可根據最后一個峰值來判斷下一個符號的開始。這種聯合估計的辦法在軟件仿真時具有良好的性能,但若要在硬件上實現則比較困難。因為在延時自相關算法中,計算M(n)的值雖然可采用迭代算法,每次計算只需1次復數運算和若干加法運算;但在自相關計算中,假設接收信號被定點化為16位整數,那么計算一次自相關的值需要16位數據的64次復數乘法,顯然,所需要的硬件資源開銷非常大,而且會影響系統(tǒng)的運行速度。這在硬件上,因資源消耗太大而無法實現。為了兼顧算法的估計精度和實現的復雜性,有必要將算法做進一步改進。即對接收數據進行二階量化以得到d[n]=Q[r(n)],其中Q表示復數量化器,見下式:

利用這種改進的自相關算法和延時自相關算法進行聯合估計的仿真曲線如圖2所示。

將圖1和圖2進行對比可知,這種對接收數據二階量化的方法會損耗算法的性能,但是,由于幀的大致位置已被限制在一定范圍之內,因此,只需根據峰值就可以確定下一個OFDM符號的準確位置。這種方法既能保證估計精度,又能滿足硬件資源利用率的要求。

4 基于FPGA的實現

4.1 自相關延時模塊的FPGA實現

為了進一步簡化運算,也可以不進行算法中的歸一化運算,而直接計算R(n)的值,并將公式簡化為:

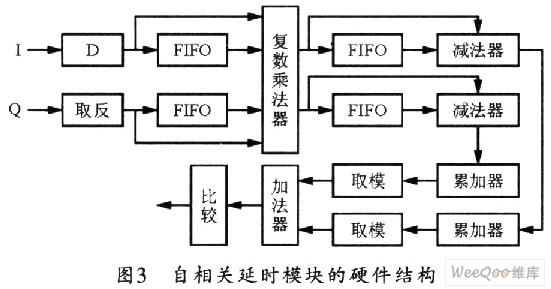

圖3所示是自相關延時模塊的硬件組成結構。它主要由FIFO延時單元、復數運算器、加法器、取模模塊組成。其中復數乘法器可直接使用IP核來實現,這比直接使用四個實數乘法器和兩個加法器更節(jié)省資源。

將接收端經過下變頻的I路和Q路數據分為兩路送入模塊,I路比Q路數據應多延時一個時鐘周期,這是為了和Q路數據保持相同的時延,此后再進入FIFO經過64個時鐘周期的延時。Q路數據首先進行取相反數運算。這是因為復數共軛運算相當于先取相反數再做復數乘法。把相減的結果送入FIFO進行延時,并將送入系統(tǒng)的復數與做減法和延時64個時鐘周期的復數進行復數乘法運算。由于兩路數據都是16位定點化整數,經過運算后會成為33位,為了節(jié)省資源,可將所得結果的高5位和低12位截去,而這并不會影響運算的精度。經過復數乘法運算的實部和虛部再分別經過64個時鐘周期的FIFO延時,并將延時前后的數據做減法運算,然后對計算的結果做累加運算。累加器輸出的結果經過取模模塊后,即可得到實部和虛部的絕對值,然后將兩部分結果相加,再將相加結果與門限值比較,超過門限則將標志位置高。但應注意門限值的選取會影響幀檢測的范圍,由于采用的是聯合檢測方法,應適當擴大門限范圍,本設計設定的門限值為峰值的1/4。

4.2 互相關模塊的FPGA實現

互相關模塊主要由匹配運算單元、取模器和加法器組成。改進的算法只對輸入數據的符號位與本地序列的符號位進行相關運算,并規(guī)定輸入符號為正取值為1,輸入符號為負取值為-1,接著根據輸入數據的符號和本地序列的符號構成的16種輸入做全排列,將所有可能的相關運算值算好存放在運算模塊中,這樣就可以根據輸入數據的符號來選擇相關運算的結果。這等效于把復數相關運算簡化為數據選擇器來實現。

圖4所示為互相關模塊的FPGA實現框圖,其中I、Q兩路數據進入模塊后,可取出其最高位存入移位寄存器,然后與本地序列做匹配運算。匹配運算模塊由64個數據選擇器和126個加法器組成,加法運算采用6級流水線來實現,這樣,可使系統(tǒng)的運算速率更高。

4.3 仿真結果分析

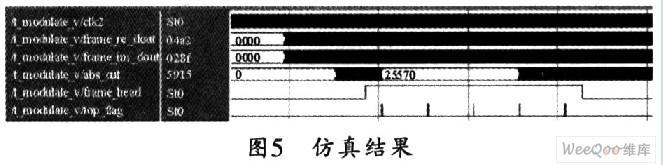

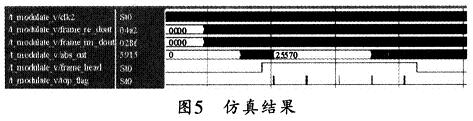

系統(tǒng)中的各模塊可采用Verilog HDL語言設計,并可使用Xilinx公司集成設計環(huán)境ISE中的ModelSim SE 6.0來完成仿真,仿真結果如圖5所示。其中frame_re_dout和frame_im_dout為送入系統(tǒng)的實部和虛部數據,abs_out為延時自相關算法中取模相加的結果,frame_head為采用延時自相關算法使數據升高時得到的一個峰值平臺,top_flag為改進自相關算法計算所得的峰值。圖中的自相關平臺內有5個峰值,這與MATLAB仿真結果相符。最后采用Xilinx公司VirtexⅡpro系列xc2vp30器件進行實現。總共邏輯單元使用率為8%,系統(tǒng)最高工作頻率為236.373 MHz 。

5 結束語

本文在研究基于802.16d的OFDM定時同步算法的基礎上提出了一種改進的算法,并在FPGA上完成了其硬件電路設計。仿真結果表明該算法在保持了原算法優(yōu)秀性能的同時,可節(jié)省硬件資源,有利于把同步模塊和接收部分其他模塊集成在單芯片中。同時,該算法也可推廣到具有相似前導字結構的802.1 1a等協(xié)議中。

-

FPGA

+關注

關注

1643文章

21963瀏覽量

614094 -

數據傳輸

+關注

關注

9文章

2003瀏覽量

65684 -

無線通信

+關注

關注

58文章

4709瀏覽量

144854

發(fā)布評論請先 登錄

802.16e技術淺析

如何定時同步算法改進及實現FPGA?

求一種基于802.16d的低復雜度的幀同步和定時同步聯合算法

IEEE802.16接收機檢測模塊的FPGA 實現

OFDM系統(tǒng)定時同步算法的改進

高階QAM定時同步算法的MATLAB仿真及FPGA實現

適用于802.16d標準的智能化5.8GHZ雙向功率放大器

適用于5G系統(tǒng)的PSS定時同步改進算法

在FPGA上實現基于802.16d的定時同步算法改進方案

在FPGA上實現基于802.16d的定時同步算法改進方案

評論