FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。隨著通信技術的飛速發展,為滿足高速數字電路和數字信號處理等對時鐘管理、信號完整性、高速寬帶接口的要求,高速處理器與通信的融合日趨緊密,高速處理器、可編程邏輯器件和高速存儲器成為設計的關鍵。Virtex- ⅡPro 系列FPGA 將可編程邏輯結構和高速處理器集成在同一芯片內部,直接的連接克服了利用總線在FPGA 和附加外部處理器之間接口的瓶頸。

Virtex-II Pro 簡介

Virtex- ⅡPro 系列最大容量的FPGA 目前能提供多達5 萬個邏輯單元具有超過10 Mb 的RAM;556 個乘法單元12 個數字時鐘管理單元以及24個集成3. 125 GbPs 的Rocket IOTM 收發器最大可提供1 200 個IO 引腳, 支持CMOS、SSTL 、HSTL 、LVDS、GTL 和3. 3V PCI 信號標準。Virtex - II Pro 系列FPGA 支持多達4 個運行頻率高達300 MHz 的PowerPC 405 處理器。PowerPC405 采用嵌入式300 MHz哈佛(Harvard) 結構的RISC 核具有五級數據通道流水線、硬件乘除單元、32 個32 位通用寄存器、16 KB指令Cache 和16 KB 數據Cache 、1 KB~16MB 可變頁尺寸組成存儲器管理單元(MMU) 和專用的片內存儲器接口。

PowerPC405 處理器由IBM CoreConnect 技術支持,CoreConnect 是運行在100~133 MHz 的64 位總線,為了使系統設計靈活性達到最大,CoreConnect 結構是作為軟IP 核在Virtex - ⅡPRO FPGA 中實現的。CoreConnect 總線結構有2 個主要總線組成,處理器局部總線(PLB) 和片內外設總線(OPB) 。這些總線可以用來分別連接高速和低速外設到PowerPC處理器。此外,設備控制寄存器總線對通用外設器件寄存器的進行管理和控制。

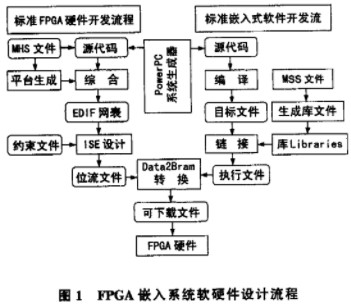

EDK(Embedded Development Kit) 是Xilinx 公司提供的嵌入開發工具,用于在FPGA 內部集成多種不同的IP 核,可方便地規劃、設計并生成整個片上系統的硬件和軟件結構。通過編寫硬件描述文件(MHS) 來設置FPGA 內部硬件系統,主要包括定制嵌入處理器PowerPC405、外圍設備IP 核、設定外部存儲器和其他外設的地址空間、管理外圍設備的控制信號及中斷信號。EDK 的硬件生成平臺根據用戶編輯的MHS 文件生成相應的VHD 文件,原理圖文件等,同時支持系統仿真。EDK工具提供了大量可供使用的IP 核, 包括SDRAM,DDRRAM,UARTController ,10/ 100 M以太網MAC ,總線仲裁器等,使FPGA 可方便地與其他外圍器件連接。EDK 實現FPGA 片內軟、硬件設計過程如圖1 所示。

應用系統結構

數據糾錯譯碼接入設備要求對同步傳輸的數據進行幀同步、解擾、糾錯譯碼處理并對處理后的數據進行網絡接入。在以太網接入部分,要求對解碼后的數據進行IP 協議封裝,然后使用數據鏈路層協議對協議包進行以太網幀的封裝,最終通過網口接入局域網。

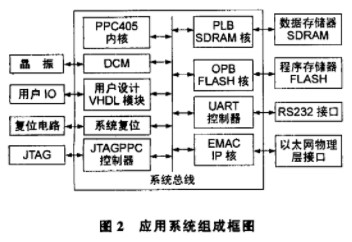

在對Virtex - II 系列FPGA 充分理解和研究的基礎上,根據系統設計需求,進行系統硬件的設計。本設計采用了VII - Pro 系列的XC2VP7FG456 芯片,在芯片內部設計嵌入了一個PowerPC405 處理器IP核。應用系統由XC2VP7FG456 芯片及其上電復位電路, 系統時鐘電路、內存電路、程序存儲電路、PROM電路、以太網PHY接口電路和RS - 232 接口電路、JTAG接口、LVPECL 電平接口電路組成。系統組成框圖如圖2 所示。

由于FPGA 可允許PowerPC 硬IP 核心分布在Virtex 結構中的任何位置,設計時需要綜合考慮系統的設計要求,合理地指定FPGA 各個管腳的信號。考慮到輸入輸出標準的不同,FPGA 芯片劃分了8 個不同的Bank ,每個Bank 可支持不同的I/ O 特性。在設計過程中,盡量把同一特性的外圍芯片管腳連接到FPGA 芯片的同一Bank 的IO 管腳。同時,為了方便進行調試,可將FPGA 芯片內部不可測內部狀態引到空余管腳。

應用系統實現

1.系統時鐘

參考時鐘由外部晶振產生,通過FPGA 芯片全局時鐘管腳接入到FPGA 內部數字時鐘管理模塊(DCM) 和時鐘分配樹。DCM 支持超過400 MHz 的時鐘輸出,提供了一個可保證精確50/ 50 占空比的零延遲時鐘緩沖。同時提供了精確控制90 ,180 ,270 相移的能力,實現對時鐘信號的綜合,支持24~420 MHz間的精確頻率產生。在FPGA 內部,DCM統一分配時鐘信號,將DCM 的時鐘輸出設置為PowerPC 的系統時鐘,并提供給PLB ,OPB 總線仲裁器。

2.外部存儲器

PPC405 的PLB 總線支持高性能的高速存儲器,如DDR RAM,SDRAM 等。OPB 總線支持通用的存儲電路, 如EPROM, SRAM, FALSH 和外部寄存器等低速的存儲器。在本設計中采用了2 片MT48V8M16 高速同步SDRAM, 構成PowerPC405處理器數據總線寬度32 位,容量為32 MB 的外部數據存儲區。在編輯MHS 文件時, 選擇加入PLBSDRAM核,在其中配置存儲器地址總線和數據總線寬度,指定存儲區的起始地址。程序存儲器除選用OPB 總線外,其余設置與數據存儲器類似。

3.以太網接口

在FPGA 內部集成10/ 100 MEthernet MAC 核。外接BCM5221 以太網物理層芯片,該芯片適用于IEEE802. 3 物理層的應用,然后通過網絡變壓器后接入以太網。在編輯MHS 文件時,選擇加入以太網MAC 層內核。

4.RS232 接口

根據需要,在FPGA 內部集成UART 控制器,外接RS232 電平轉換器,連接到計算機的串口,用作應用程序的調試信息輸出。在MHS文件中可配置串口的波特率,數據位寬度,奇偶校驗等設置。

5.在線可編程PROM

FPGA 是基于門陣列方式為用戶提供可編程資源的,其內部邏輯結構的形成是由配置數據決定的。這些配置數據通過外部控制電路或微處理器加載到FPGA 內部的SRAM 中,由于SRAM 的易失性,每次上電時,都必須對FPGA 進行重新配置。在實際應用時,采用2 片XC18V04 PROM,用以存放FPGA 的配置數據流。通過硬件跳線將FPGA 設置為串行主模式配置方式,在FPGA 每次上電后,自動將配置數據從PROM讀入到SRAM中,實現內部結構映射。

6.JTAG端口

JTAG端口用于進行FPGA 配置信息的下載,編程PROM。在VII - Pro 中嵌入PowerPC 內核時,還可進行應用程序代碼的下載和調試。為方便軟件代碼的調試,除FPGA 專用配置管腳TCK,TMS ,TDO ,TDI外,還可在FPGA 芯片上指定4 個普通I/ O 管腳,內部配置連接PowerPC 內核的JTAG 接口, 用于PowerPC 內核的調試,軟件代碼跟蹤調試。在這種模式下,軟件代碼可單獨下載到PowerPC 內核進行軟件的調試。在利用JTAG引腳配置FPGA 時,需要注意:JTAG配置引腳最好接上拉電阻,在配置期間INIT 引腳要接地。

FPGA簡介

目前以硬件描述語言(Verilog 或 VHDL)所完成的電路設計,可以經過簡單的綜合與布局,快速的燒錄至 FPGA 上進行測試,是現代 IC 設計驗證的技術主流。這些可編輯元件可以被用來實現一些基本的邏輯門電路(比如AND、OR、XOR、NOT)或者更復雜一些的組合功能比如解碼器或數學方程式。在大多數的FPGA里面,這些可編輯的元件里也包含記憶元件例如觸發器(Flip-flop)或者其他更加完整的記憶塊。

系統設計師可以根據需要通過可編輯的連接把FPGA內部的邏輯塊連接起來,就好像一個電路試驗板被放在了一個芯片里。一個出廠后的成品FPGA的邏輯塊和連接可以按照設計者而改變,所以FPGA可以完成所需要的邏輯功能。

FPGA一般來說比ASIC(專用集成芯片)的速度要慢,無法完成復雜的設計,而且消耗更多的電能。但是他們也有很多的優點比如可以快速成品,可以被修改來改正程序中的錯誤和更便宜的造價。廠商也可能會提供便宜的但是編輯能力差的FPGA。因為這些芯片有比較差的可編輯能力,所以這些設計的開發是在普通的FPGA上完成的,然后將設計轉移到一個類似于ASIC的芯片上。另外一種方法是用CPLD(復雜可編程邏輯器件備)。

FPGA芯片結構

目前主流的FPGA仍是基于查找表技術的,已經遠遠超出了先前版本的基本性能,并且整合了常用功能(如RAM、時鐘管理和DSP)的硬核(ASIC型)模塊。如圖3所示(注:圖3只是一個示意圖,實際上每一個系列的FPGA都有其相應的內部結構),FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內嵌的底層功能單元和內嵌專用硬件模塊。

總結

使用XC2VP7FG456 型FPGA 及其內部的PowerPC405 嵌入處理器開發了數據處理和網絡接入板,經電路測試,可實現傳輸速率為100 Mb/ s的同步數據接收和處理,滿足系統需要。 Virtex- ⅡPro 系列FPGA 將可編程邏輯結構和高速處理器集成在同一芯片內部,直接的連接克服了利用總線在FPGA 和附加外部處理器之間接口的重點,支持內部嵌入運行頻率高達300 MHz的PowerPC405 處理器IP 核,設計人員可以并行進行快速的硬件和軟件開發,在系統結構一級利用可編程性能所提供的優點,從而使設計投入生產所需要的時間更短。

-

處理器

+關注

關注

68文章

19885瀏覽量

235069 -

FPGA

+關注

關注

1645文章

22040瀏覽量

618181 -

局域網

+關注

關注

5文章

778瀏覽量

47157

發布評論請先 登錄

Xilinx可編程邏輯器件的高級應用與設計技巧絕版教程

XC2V1000-4FGG456C XILINX Virtex-II? 系列介紹

【下載】《FPGA上的嵌入式系統設計實例(附光盤XILINX大學合作計劃指定教材)》

Virtex-6 FPGA ML605開發評估技術方案

DS112 - Virtex- 4 系列概述

采用Virtex-7 FPGA進行DSP性能演示

詳解嵌入式軟件開發到FPGA開發

Eclypse Z7開發板讓軟件開發人員了解FPGA

采用Virtex- ⅡPro系列FPGA可進行硬件和軟件開發

采用Virtex- ⅡPro系列FPGA可進行硬件和軟件開發

評論