引言

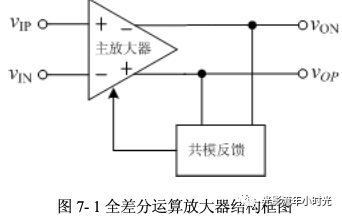

全差分運放(fully differential operation)相對于單端輸出電路來說,不僅輸出擺幅更大、共模噪聲抑制更好,還能消除高階諧波失真。然而,在高增益運放中,輸出共模電平對器件的特性和失配相當敏感,而且不能通過差模反饋來達到穩(wěn)定。因此,必須額外引入負反饋機制,即共模反饋(CMFB)來穩(wěn)定運放的共模輸出電平。共模反饋的基本原理是先通過檢測網(wǎng)絡(luò)得到輸出共模電平Vo_cn,然后將Vo_cn和一個參考電壓Vcn(一般為電源電壓的一半)相比較,再用得出的誤差信號來調(diào)節(jié)運放的偏置電流,從而達到使輸出共模信號穩(wěn)定的目的。這種方式的設(shè)計要點如下:

(1)共模信號檢測應(yīng)具有線性特性;

(2)共模反饋環(huán)路的增益必須盡可能的高;

(3)反饋環(huán)路的帶寬不能小于差模通路(在許多實際應(yīng)用中,這兩個帶寬必須一致);

(4)確保共模環(huán)路穩(wěn)定;

(5)應(yīng)引入保護機制,以避免“鎖死狀態(tài)”的出現(xiàn)(輸出保持在電源電壓的情況)。

目前已經(jīng)有了大量關(guān)于差模反饋環(huán)路穩(wěn)定性的理論研究,而對于共模反饋環(huán)路的研究卻很少。現(xiàn)有的共模反饋電路的設(shè)計更多的是通過實際經(jīng)驗、反復(fù)調(diào)試來得到穩(wěn)定環(huán)路。筆者通過對最常用的、采用一級共模反饋的兩級運放的環(huán)路進行穩(wěn)定性分析,明確得出了其穩(wěn)定條件,從而理論化了共模反饋電路的設(shè)計。然后基于這個條件,并采用Bi-CMOS工藝設(shè)計了一種低成本、高穩(wěn)定、匹配好的共模反饋電路。整個運放可應(yīng)用于一款高性能音頻CLASS-D芯片。

1共模反饋環(huán)路分析及穩(wěn)定條件

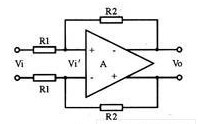

圖1所示是全差分運放的一種典型應(yīng)用電路。該電路*有三個環(huán)路:差模環(huán)路、共模反饋外環(huán)(結(jié)構(gòu)相同,由R1、R2及運放本身構(gòu)成);以及共模反饋內(nèi)環(huán)(運放內(nèi)部自帶)。只有在三個環(huán)路均穩(wěn)定的條件下,該運放才能正常工作。須特別注意的是:對于兩級運放,共模反饋外環(huán)是一個正反饋。因為信號經(jīng)過運放內(nèi)部的兩次反相后。共模信號從Vo反饋到Vi,是同相的,但對差模信號則是反相的。實際應(yīng)用中,運放的輸入端可能出現(xiàn)非常大的共模電平(使它是瞬時的),這將導(dǎo)致輸入對管關(guān)斷,輸出電平接近電源電壓。由于此時差模回路中斷,整個外環(huán)呈現(xiàn)共模正反饋。這就會使運放呈現(xiàn)“鎖死狀態(tài)”。由于這種情況很可能發(fā)生在電路的啟動過程。因此,對于共模環(huán)路的穩(wěn)定性研究很有必要。

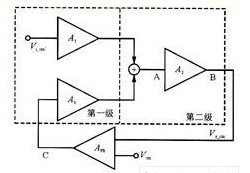

圖2所示是采用一級共模反饋的兩級運放的典型拓撲結(jié)構(gòu)。其中Vi_cm、Vo_cm一分別為運放的輸入、輸出共模信號。A1、A2為運放的第一、二級。一般對兩級運放多采用密勒補償,使A點為主極點,B點為次主極點。AFB處設(shè)定比較電平Vcm(以下稱之為共模反饋運放);Ab為共模內(nèi)環(huán)與差模第一級的相交部分。各子運放均為單級運放,并假定它們內(nèi)部的零、極點均遠遠大于帶寬。共模反饋信號通過調(diào)節(jié)運放第一級的偏置電流,可以達到穩(wěn)定第一、二級輸出共模電平的目的。這個拓撲結(jié)構(gòu)將三個環(huán)路緊密聯(lián)系起來,其共模環(huán)路完整包括了運放的第二級和運放差模通路的主、次極點,而忽略了帶寬外零極點。逐一分析三個環(huán)路,即可得出其共模環(huán)路的穩(wěn)定條件。

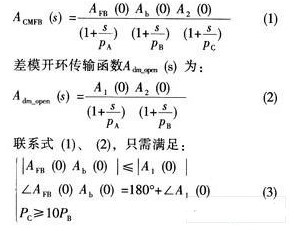

首先分析運放本身。其共模反饋內(nèi)環(huán)傳輸函數(shù)ACMFB(s)為:

即可保證在差模開環(huán)穩(wěn)定時,其共模內(nèi)環(huán)也穩(wěn)定。

繼續(xù)分析由運放構(gòu)成的環(huán)路。系數(shù)為β(一般地,β≤1),那么,輸函數(shù)Adm_loop(s)為:其共模內(nèi)環(huán)也設(shè)運放的反饋其差模環(huán)路傳輸函數(shù)Adm_loop(s)為:

即可保證共模外環(huán)的穩(wěn)定。

聯(lián)系式(3)、(5)、(1 0),可以得到該拓撲結(jié)構(gòu)共模環(huán)路的穩(wěn)定條件如下:

(1)運放的差模開環(huán)穩(wěn)定;

(2)AFB(0)、Ab(0)與A1(0)滿足相位相差180°、絕對值近似相等:

(3)共模反饋額外引入的極點不影響環(huán)路帶寬。

基于上述條件可見,共模環(huán)路無需額外補償。由于整個運放僅額外引入運放AFB,因此成本低、設(shè)計簡單,且共模內(nèi)環(huán)帶寬與差模開環(huán)相等、增益相近,故能滿足共模反饋設(shè)計要點(2)、(3)、(4)。

2低成本高穩(wěn)定的共模反饋電路

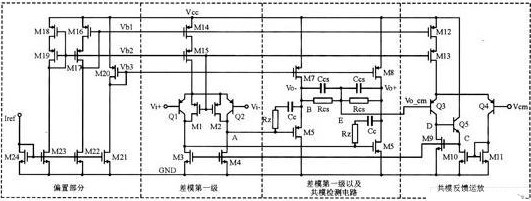

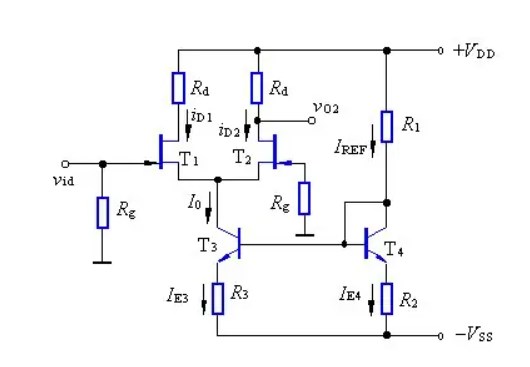

圖3是本文所設(shè)計的兩級全差分運放電路。該電路的共模反饋部分結(jié)構(gòu)新穎、成本低、匹配好,基于圖2的拓撲結(jié)構(gòu),可滿足本文提出的穩(wěn)定條件。圖3中,Iref為基準電流,兩級運放采用RZ和Cc組成密勒補償,來滿足穩(wěn)定條件(1)。為了減小失調(diào),運放的第一級和共模反饋運放采用三極管(Q1~Q4)作為輸入對管。

電路中的Ml、M2分別與Ql、Q2并聯(lián),其柵極信號Vb2隨電源電壓的升高而升高,其作用相當于在輸入級增加兩個比較器。正常工作時,M1、M2關(guān)斷,Ql、Q2處理信號,而在電源電壓較低(啟動時)以及輸入信號的共模電平高于Vb2比時,Q1、Q2關(guān)斷,M1、M2線性導(dǎo)通,以穩(wěn)定環(huán)路各級共模電平。從而有效避免了電路啟動過程鎖死狀態(tài)的出現(xiàn),滿足了設(shè)計要點(5)。

共模檢測電路由電阻Rcs并聯(lián)Ccs來完成。引人后者的目的是在高頻時既可旁路電阻的寄生電容,又可產(chǎn)生一個零點。以阻止共模增益的降低,從而滿足設(shè)計要點(1)。

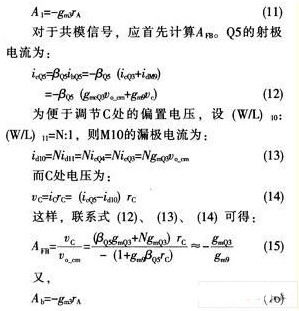

共模反饋運放在Q3、Q4、M10、Mll組成的普通電流鏡結(jié)構(gòu)基礎(chǔ)上,還額外增加了Q5和M9兩個器件。Q5作為射隨器可將原電流鏡結(jié)構(gòu)中的高阻、大電容輸出結(jié)點分隔為C、D兩點。分隔后,相對于兩級運放的主、次極點A、B,D點,其電容減小(僅有寄生電容),而C點阻抗減小(連接Q5的射極),所以,C、D兩處極點均不影響環(huán)路帶寬,可滿足穩(wěn)定條件(3)。接著比較兩者的增益,其差模第一級增益為:

聯(lián)系式(11)、(15)、(16)可見,只需Q1~Q4,M3、M4、M9、M11以及M12~M15尺寸對應(yīng)

在式(11)~(17)中,rA、rC、VA、VC分別為結(jié)點A、C處的小信號電阻值和電壓值。

式(17)表明共模環(huán)路增益與差模開環(huán)增益絕對值近似相等、相位相差180°,可滿足穩(wěn)定條件(2)。由此,本電路已可同時滿足本文提出的3個穩(wěn)定條件以及5個共模反饋設(shè)計要點。

傳統(tǒng)的共模反饋運放一般采用電流鏡和二極管作為負載。即使嚴格按照穩(wěn)定條件進行設(shè)計,由于電路的不匹配(共模反饋運放的結(jié)構(gòu)、尺寸與差模第一級不相同),將導(dǎo)致器件的短溝道效應(yīng)相異、工藝失配的差異較大,從而使得共模內(nèi)環(huán)與差模開環(huán)的增益不可避免的存在偏差,因此,傳統(tǒng)電路不能很好的滿足穩(wěn)定條件。

而本文提出的共模反饋運放電路匹配高、版圖匹配容易。由式(15)可知,運放的右半電路幾乎不影響運放的增益,且對C處偏置電壓的影響也較小(受Q5和M9組成的負反饋作用)。所以,在平衡條件下,右半部分器件的短溝道效應(yīng)及工藝失配帶來的影響可以忽略。而運放的左半邊電路以及尾電流源與差模第一級對應(yīng)匹配,因而其短溝道效應(yīng)也相近。因此只需使這部分器件的版圖采用對稱放置來設(shè)計,即可使它們的工藝匹配良好,從而確保電路嚴格滿足穩(wěn)定條件。

3仿真結(jié)果

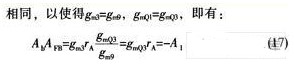

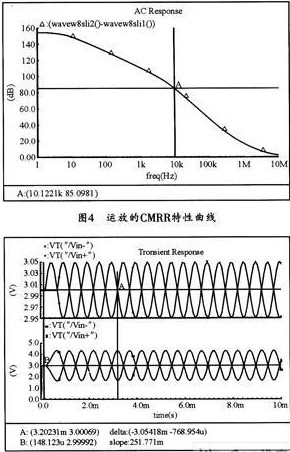

本電路的設(shè)計主要基于TSMC 0.5um BiCMOS工藝,電源電壓為6 V。所有波形均可在Spectre下仿真所得。仿真結(jié)果表明,在開環(huán)條件下,該運放的正、負端增益相同,相位相差180°,而且電路匹配良好,輸出精確平衡。圖4所示是該運放的共模抑制比(CMRR)特性曲線。由圖可見,在10kHz時,該電路的CMRR依舊高達85 dB。事實上,該運放已實際應(yīng)用于一款高性能音頻CLASS—D芯片之中。圖5是其作為積分器處理音頻數(shù)據(jù)的瞬態(tài)仿真波形,其中輸入信號是3 V共模電平,幅度為50 mV,頻率為1 kHz的正弦信號。輸出信號為頻率不變,幅度為3 V的余弦信號,其共模電平穩(wěn)定在3 V,從而表明該運放工作良好。

4結(jié)束語

本文分析了全差分運算放大器的共模反饋原理,研究了采用一級共模反饋的兩級運放拓撲結(jié)構(gòu)并得出其穩(wěn)定條件。基于這個條件,文章又提出的一種結(jié)構(gòu)新穎、電路匹配良好、輸出平衡高的共模反饋方案。整個運放現(xiàn)已用于一款高性能音頻CLASS—D芯片。經(jīng)Spectre仿真驗證,本運放工作穩(wěn)定,輸出精確平衡。

-

芯片

+關(guān)注

關(guān)注

459文章

52181瀏覽量

436185 -

運算放大器

+關(guān)注

關(guān)注

216文章

5667瀏覽量

175799 -

仿真

+關(guān)注

關(guān)注

51文章

4239瀏覽量

135309

發(fā)布評論請先 登錄

全差分運算放大器結(jié)構(gòu)框圖解析 常見的全差分運算放大器電路分析

運算放大器輸入和輸出共模與差分電壓范圍

運算放大器權(quán)威指南和基于運算放大器和模擬集成電路的電路設(shè)計及OP放大器應(yīng)用技巧100例PDF分享

運算放大器輸入和輸出共模與差分電壓范圍詳解

基于運算放大器的放大電路解析

差分運算放大器板的資料分享

基于準浮柵的低功耗差分運算放大器

一種高增益CMOS全差分運算放大器的設(shè)計

李福樂的全差分運算放大器電子書

采用CLASS—D芯片構(gòu)成全差分運算放大器的共模電路設(shè)計及仿真研究

采用CLASS—D芯片構(gòu)成全差分運算放大器的共模電路設(shè)計及仿真研究

評論