1 引 言

DAC5687是美國TI公司出品的一款雙通道、16bit高速數(shù)模轉換芯片。片內(nèi)資源豐富, 具有內(nèi)插、調制等多種功能。FPGA 因其屬于大規(guī)模在系統(tǒng)可編程專用集成電路而且具有高密度、高速度、高可靠性等特點, 因此FPGA 應用于高速多通道雷達信號模擬器可大大提高系統(tǒng)設計的靈活性和系統(tǒng)的擴展性。

本文設計的高速多通道信號模擬器系統(tǒng)可廣泛應用于通信、雷達信號的模擬產(chǎn)生, 為雷達設備, 特別是接收機設備檢修提供參考信號, 分離設備故障問題, 簡化設備檢修過程。另外, 此高速多通道信號模擬器系統(tǒng)基于CPC I總線, 具用很好的工程穩(wěn)定性和通用性。

2 系統(tǒng)概述

2. 1 系統(tǒng)組成

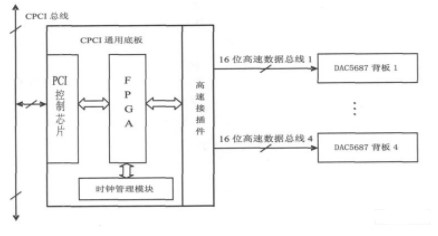

高速多通道信號模擬器采用通用CPC I底板與功能背板相結合的設計思路, 其組成如圖1所示。

圖1 高速多通道信號模擬器

采用上圖所示設計方法, 系統(tǒng)可擴展性強, 不同應用場合只需更換不同的功能背板即可。

2. 2 系統(tǒng)功能

對本文所設計的高速多通道雷達信號模擬器,由FPGA 控制時鐘管理模塊, 為四路DAC5687背板提供相參工作時鐘。同時, 利用X ilinx FPGA 提供的DDS核( IP core)產(chǎn)生信號的樣點數(shù)據(jù), 通過高速接插件將信號樣點數(shù)據(jù)傳輸?shù)紻AC5687背板, 在背板上實現(xiàn)數(shù)模轉換和信號輸出功能。

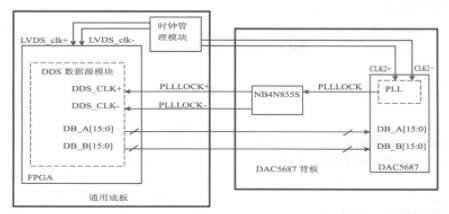

3 DAC5687功能背板電路設計

根據(jù)DAC5687的工作手冊, 結合圖1中的功能設計, 由FPGA 產(chǎn)生的A、B 兩路信號數(shù)據(jù)分別通過兩路16bit數(shù)據(jù)總線傳輸?shù)紻AC5687, LVPECL時鐘信號可以選擇與CLK1 /CLK1C 或者CLK2 /CLK2C相連接, 具體由DAC5687的時鐘工作模式?jīng)Q定。當DAC5687工作在內(nèi)部時鐘模式下, 與CLK1 /CLK1C連接; 工作在外部時鐘模式下, 與CLK2 /CLK2C 連接。另外, NB4N855S是一款電平轉換芯片 , 能將任何電平的信號轉換成為LVDS信號, 本設計中利用這款芯片將DAC5687內(nèi)部鎖相環(huán)PLL 產(chǎn)生的時鐘單端信號轉換成為LVDS 信號, 通過高速接插件傳回通用底板, 作為外部時鐘工作模式下的數(shù)據(jù)產(chǎn)生同步時鐘。

4 單端高速數(shù)據(jù)傳輸線的布線及匹配問題

4. 1 單端高速數(shù)據(jù)線的阻抗計算模型

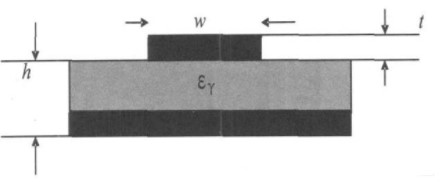

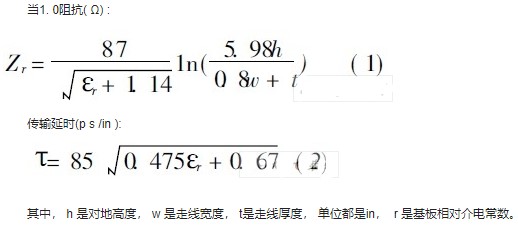

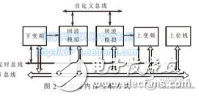

因為DAC5687芯片的兩路16bit數(shù)據(jù)總線接口都是單端的, 即每bit都只對應一根單端傳輸信號線, 并非是通常高速數(shù)據(jù)傳輸所使用的LVDS、LVPECL等差分傳輸信號線, 所以在印制電路板( PCB )設計時, 就必須考慮高速數(shù)據(jù)傳輸情況下的單端數(shù)據(jù)線布線及終端匹配問題。本設計采用微帶線阻抗計算模型和表層走線規(guī)則, 以FR4印制板為例進行分析。表層走線應采用微帶線模型, 如圖2所示。

圖2 微帶線阻抗計算模型。

例如, 當設計單根傳輸線阻抗為50Ω, 印制板為FR4, 其介電常數(shù)εr = 4. 3, 假設對地高度h =0. 0046in, 走線厚度t= 0. 00137 in (相當于銅層總量1oz )。由( 1)可以計算得到印制電路板走線寬度為0. 008in, 即8m il。

4. 2 DAC5687高速數(shù)據(jù)線的終端匹配

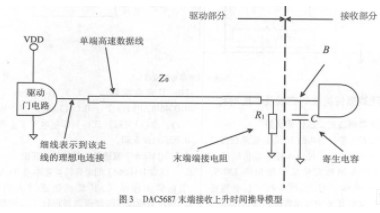

因為DAC5687的最高轉換速率是500MSPS, 采用奇偶工作模式, 其最高數(shù)據(jù)輸入的速率為250MSPS, 所以在印制電路板設計上應將單端高速數(shù)據(jù)線末端上升時間控制在< 2ns的范圍內(nèi)。計算模型 如圖3所示。

左邊部分, 即驅動部分, 由驅動門電路、傳輸線和端接電阻組成。對于印制板走線, 當連線長度小于上升沿有效長度的1 /6時, 該電路表現(xiàn)為集總系統(tǒng)特征。以FR4板材為例, 由( 2)可計算得到表層走線的上升沿有效長度約為14. 286in。所以, 只要表層走線長度小于2. 38 in 即可采用集總系統(tǒng)模型進行電路布線。但當印制電路板走線的長度大于上升沿的長度的1 /6時, 集總系統(tǒng)模型失效, 應采用分布系統(tǒng)模型討論。根據(jù)傳輸線理論, 傳輸線模型的完全響應為:

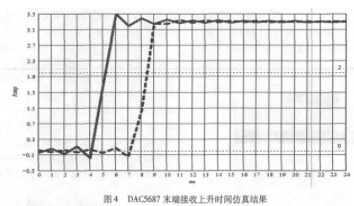

其中ZL (w ) = R1 jwC 根據(jù)電路實際參數(shù), 使用Ma thCAD進行脈沖上升時間的仿真, 其中源端阻抗(即驅動門電路的內(nèi)阻) Zs = 30Ω , Z0 = 50Ω??, C =5pF, 印制板傳輸線長度X = 4in, 傳輸線并聯(lián)電容約為CT = X·C = 12pF, 傳輸線串聯(lián)電感約為LT =X·L = 32nH, RT =X·R≈0. 02Ω結果如圖4所示。

圖4中實線表示驅動門電路的輸出脈沖上升沿波形, 虛線表示DAC5687末端接收波形。由于末端電容負載C 的影響, 振鈴明顯減少, 上升時間增加,末端上升時間仿真結果約為1. 3ns, 實測結果約為1. 5ns, 兩者基本相符。

由以上分析可得到結論, 單端高速數(shù)據(jù)總線的走線應盡可能的短, 并在終端端接匹配負載電阻, 以達到傳輸線匹配、提高數(shù)據(jù)傳輸速率的目的。

5 FPGA 設計

依托通用底板, 針對DAC5687 功能背板進行FPGA 設計。其主要功能一是使FPGA 通過DAC5687 的串行編程接口( SPI) 對DAC5687 的內(nèi)部寄存器進行設置; 二是實現(xiàn)內(nèi)部DDS 數(shù)據(jù)源與DAC5687的嚴格同步。采用VHDL或V erilog 語言編寫程序, 可以簡便實現(xiàn)上述功能。DDS 與DAC5687的接口原理如圖5所示。

圖5 FPGA與DAC5687的數(shù)據(jù)及時鐘接口框圖。

如圖所示, 時鐘管理模塊將分別給FPGA 和DAC5687提供差分工作時鐘。DAC5687利用內(nèi)部鎖相環(huán)PLL產(chǎn)生數(shù)據(jù)同步時鐘, 經(jīng)由NB4N855S變換成LVDS差分時鐘信號傳入FPGA 內(nèi)部DDS數(shù)據(jù)源, 作為數(shù)據(jù)源工作時鐘, 以保證信號樣點數(shù)據(jù)和DAC轉換工作時鐘同步。DDS數(shù)據(jù)源將產(chǎn)生的A、B兩路信號樣點數(shù)據(jù)通過印制板上的單端高速數(shù)據(jù)總線傳輸?shù)紻AC5687, 最終完成數(shù)模轉換。

6 結束語

討論了在CPC I通用底板上設計DAC5687數(shù)模轉換背板的設計方法, 解決了單端高速數(shù)據(jù)傳輸線的布線和終端匹配問題, 為高速多通道信號模擬器提供了一種解決方案。

-

FPGA

+關注

關注

1645文章

22049瀏覽量

618409 -

芯片

+關注

關注

460文章

52506瀏覽量

440828 -

總線

+關注

關注

10文章

2959瀏覽量

89754

發(fā)布評論請先 登錄

高速ADDA模塊開箱,F(xiàn)PGA專用,高速信號輸出,數(shù)模信號轉換

4個高速串行通道的AHCC2001PCI/CPCI

基于CPCI接口DSP板的雷達目標模擬器

基于DAC5687的高速多通道信號模擬器系統(tǒng)設計

使用高速DA芯片實現(xiàn)數(shù)模轉換的方法

高速數(shù)模轉換器的功能特性和作用

一種雷達回波信號模擬器的設計與實現(xiàn)

CPCI高速采集回放卡

CPCI數(shù)據(jù)總線接口的設計與實現(xiàn)

基于CPCI接口DSP板的雷達目標模擬器

CPCI數(shù)據(jù)總線接口的設計與實現(xiàn)

一種基于FPGA嵌入式系統(tǒng)的雷達信號模擬器的實現(xiàn)

基于CPCI總線和高速數(shù)模轉換芯片實現(xiàn)高速多通道信號模擬器的設計

基于CPCI總線和高速數(shù)模轉換芯片實現(xiàn)高速多通道信號模擬器的設計

評論