昨天在調(diào)試Lattice EVDK開發(fā)板上的DDR3 Demo時,遇到一個莫名其妙的問題,今天來總結(jié)一下,并與大家分享。

一、問題描述

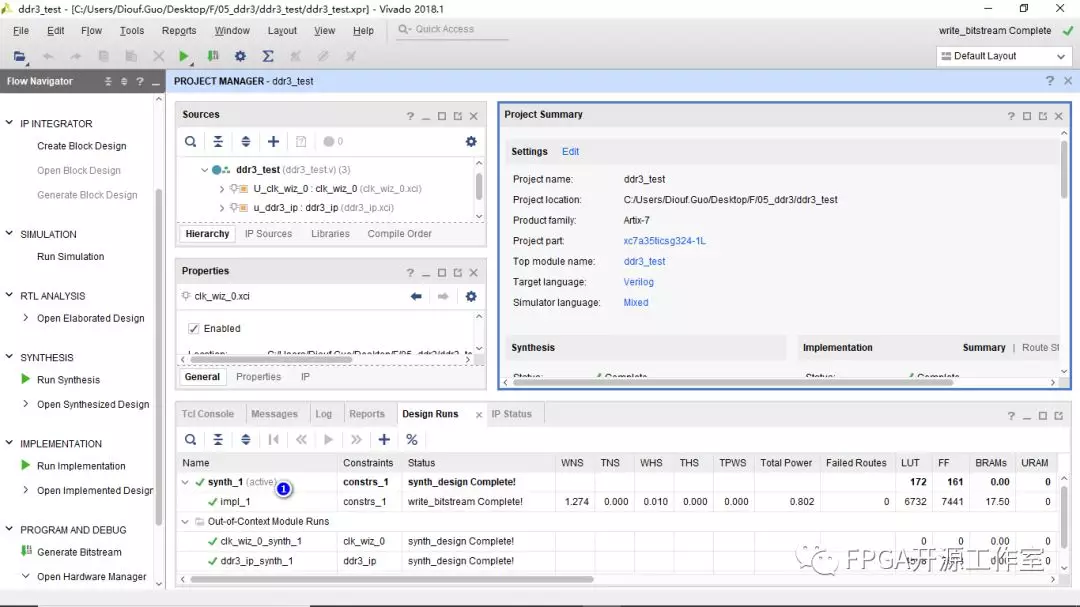

在Demo的頂層文件ddr3_test_top.v中有如下幾句話:

inputtest1; outputout_test1; assignout_test1=test1;

且test1和out_test1與Design中的其他邏輯沒有任何的關系,然而,當我把它刪除的時候,卻發(fā)現(xiàn)原本運行正常的Demo卻出錯了!!!

于是乎,先去檢查這兩個引腳是否和硬件相關,在LPF文件中找到其相關約束:

LOCATECOMP"test1"SITE"F5"; IOBUFPORT"test1"IO_TYPE=SSTL15_I; LOCATECOMP"out_test1"SITE"B1"; IOBUFPORT"out_test1"IO_TYPE=SSTL15_I;

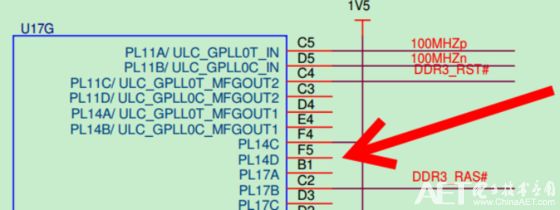

然后查看EVDK開發(fā)板的原理圖:

握草,這是什么鬼?

于是乎,進一步做測試,把test1和out_test1替換為其他的引腳試試看呢。結(jié)果發(fā)現(xiàn):當test1在Bank7上時,Demo功能正常,當test1不在Bank7上時,功能則不正常!

想了好久,奈何我這種小菜鳥卻怎么也想不明白,于是請教了大牛!

二、問題分析

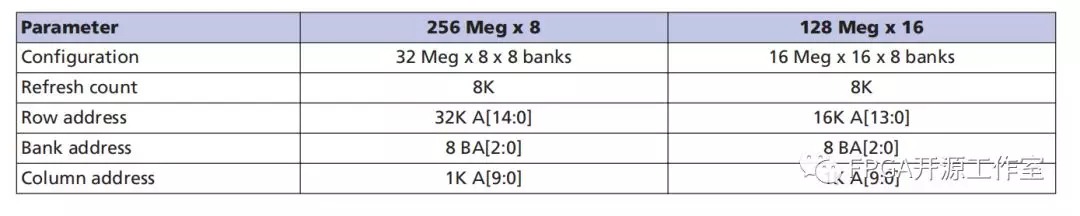

首先,還是檢查原理圖和LPF文件,由于EVDK板子上有兩個Mircon的DDR3的內(nèi)存顆粒,且均為x16的Configuration。也就是DQ的寬度為16bit,兩個顆粒合并為32bit的DQ。其中顆粒一對應DQ0~DQ15,顆粒二對應DQ16~DQ31。DQ0~DQ15連接到了Bank6上面,而DQ16~DQ31連接到了Bank7上面。但是需要注意的是,一些控制信號(如RST、CS、WE、DM等)則分布在Bank6和Bank7上,換句話說,即使Design中只需要使用一個DDR3顆粒,也需要同時使用Bank6和Bank7。

因為DDR3采用的是SSLT15 I電平標準,所以需要設置Bank6和Bank7的VREF。在LPF文件中,我們可以找到:

LOCATEVREF"BANK_6_VREF"SITE"V4"; LOCATEVREF"BANK_7_VREF"SITE"J7";

檢查原理圖,發(fā)現(xiàn)V4和J7引腳也正確地連接到了參考電壓上。

此時,我們再次將上文提到的ddr3_test_top.v中的test1和out_test1相關的幾條語句刪除,并刪除LPF文件中的相關語句。

然后從新綜合、MAP,并PAR,此時在PAR的報告中可以發(fā)現(xiàn)如下的警告:

WARNING - par: LOCATE VREF "BANK_7_VREF" preference has been ignored, because no PIO in bank "7" uses this VREF.

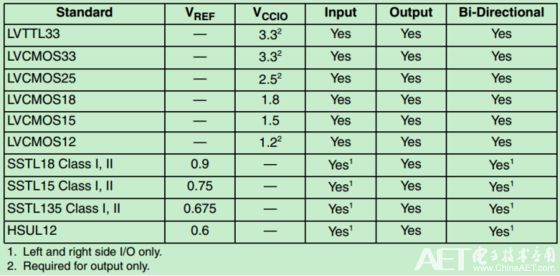

也就是說Diamond認為,我們的Design中并沒有使用Bank7中的PIO,所以不需要VREF,并忽略了LPF文件中給出的約束。所以Bank7的VREF引腳并未被設置為VREF模式,而是作為普通IO的(默認模式)。但是DDR3使用的是SSLT15 I電平標準,需要VERF引腳為其提供0.75V的參考電壓(一般使用1.5V的VCCIO分壓即可),如下圖所示:

檢查ECP5數(shù)據(jù)手冊,發(fā)現(xiàn)如下一句話:

The VREF voltage is used to set the threshold for the referencedinputbuffers, such as SSTL.

注意是input!這就解釋了為什么當test1引腳分配在Bank7上可以,分配在其他引腳上就不行的原因了。因為如果Bank7上沒有input的話,Diamond就會認為此時為Bank7設置VREF是沒有必要的,所以也就忽略了LPF中的約束。

難道是ECP5的數(shù)據(jù)手冊寫錯了?難道是DDR的output也需要VREF?

其實不然,再次檢查EVDK板的原理圖,發(fā)現(xiàn)Bank6和Bank7的VREF實際上連接的是同一個電壓(換句話說,這兩個VREF是直接連在一起的)。但是合理的硬件設計方式是,不同Bank的VREF獨立(即不要連接在一起)。也正是這種不合理的設計方式,導致了本文所討論的問題。

在我們的設計中實際上只需要給Bank6設置VREF即可,Bank7實際上是不需要的,但是為什么不給Bank7 VREF的話,DDR卻不能正常工作呢?原因在于,如果Bank7的J7引腳(VREF1_7)沒有被配置為VREF輸入模式的話,其默認為上拉的。而J7引腳(VREF1_7)的上拉會影響到VREF的電壓,進而影響到Bank6上的V4引腳(VREF1_6)的VREF輸入,最終導致Bank6沒有穩(wěn)定有效的VREF,因此DDR不能正常工作。

為了讓J7引腳(VREF1_7)不影響VREF的電壓,顯然最好是將其也設置成VREF輸入模式,為了防止我們的設置被Diamond優(yōu)化掉,才出現(xiàn)了本文前面所討論的這一問題。

三、關于SSTL電平(更新內(nèi)容)

這里來分析一下為什么DDR3的相關IO的輸入需要參考電壓,而輸出卻不需要。DDRx SDRAM普通IO采用的是SSTL電平標準(clk和dqs等采用的是SSTL的差分版本SSTLD),而SSTL實際上是一種偽差分電平。

所謂偽差分電平,就是信號的接收端是一個差分的接收器,但是其中一端固定接參考電壓VREF,而另一端接單端信號線。輸入信號電壓與參考電壓之間進行比較,作為判決輸入信號高低的標準。而偽差分標準的輸出驅(qū)動器則是單端信號標準中常見的推挽式的結(jié)構(gòu)(Push-Pull),顯然是不需要參考電壓VREF的。

由于偽差分電平的信號輸出的擺幅較小,瞬態(tài)的電流較小,保持信號完整性要相對容易些。因此,這種電平主要應用在高速的存儲器接口中,如DDRx SDRAM、QDR SRAM和RLDRAM等中。

這種結(jié)構(gòu)的好處是,其輸入信號只需要在VREF上下小幅度擺動即可被輸入驅(qū)動器正確地接收。這樣信號的噪聲余量就很大,信號能否被正確接收下來,VREF將起到關鍵作用,因此設計時需要保證VREF較高的精度。

-

電平

+關注

關注

5文章

367瀏覽量

40578 -

開發(fā)板

+關注

關注

25文章

5669瀏覽量

104516

原文標題:【博文連載】EVDK DDR3 Demo調(diào)試筆記(關于VREF的問題)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應用ChinaAET】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

基于Digilent的Arty Artix-35T FPGA開發(fā)板的DDR3讀寫控制

基于Arty Artix-35T FPGA開發(fā)板的DDR3和mig介紹

如何提高DDR3的效率

【創(chuàng)龍TMS320C665x DSP開發(fā)板】DDR3加載程序的問題與解決方法

6678開發(fā)板DDR3布線約束的問題

6657的DDR3初始化不成功

請問誰有LATTICE ECP3系列的開發(fā)資料嗎?

【Combat FPGA開發(fā)板】配套視頻教程——DDR3的讀寫控制

DDR3芯片讀寫控制及調(diào)試總結(jié)

紫光同創(chuàng)FPGA入門指導:DDR3 讀寫——紫光盤古系列50K開發(fā)板實驗教程

Xilinx DDR3最新VHDL代碼(通過調(diào)試)

基于FPGA的DDR3 SDRAM控制器用戶接口設計

安捷倫科技推DDR3協(xié)議調(diào)試和測試套件,具備最齊全的行業(yè)功能

lattice DDR3 IP核的生成及調(diào)用過程

調(diào)試Lattice EVDK開發(fā)板上的DDR3 Demo時的問題

調(diào)試Lattice EVDK開發(fā)板上的DDR3 Demo時的問題

評論