聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

ADS1220

+關注

關注

24文章

488瀏覽量

125529

發布評論請先 登錄

相關推薦

熱點推薦

廣立微YAD貫穿全鏈路良率診斷分析

長期以來,良率一直被視為芯片廠商和晶圓代工廠的生命線,其不僅是成本控制的關鍵因素,更是提升生產效率、增加產能以及增強市場競爭力的核心驅動力。

三星在4nm邏輯芯片上實現40%以上的測試良率

較為激進的技術路線,以挽回局面。

4 月 18 日消息,據韓媒《ChosunBiz》當地時間 16 日報道,三星電子在其 4nm 制程 HBM4 內存邏輯芯片的初步測試生產中取得了40% 的良率,這高于

發表于 04-18 10:52

三星電子1c nm內存開發良率里程碑推遲

據韓媒報道,三星電子已將其1c nm DRAM內存開發的良率里程碑時間推遲了半年。原本,三星計劃在2024年底將1c nm制程DRAM的良率提升至70%,以達到結束開發工作、順利進入量

三星1c nm DRAM開發良率里程碑延期

據韓媒MoneyToday報道,三星電子已將其1c nm(1-cyano nanometer)DRAM內存開發的良率里程碑時間從原定的2024年底推遲至2025年6月。這一變動可能對三星在HBM4

ADS8472采樣率可調嗎?

問題如下:

1、ADS8472手冊中第一頁的features里寫到“0 to 1-MHz Sample Rate”,是不是指這款adc采樣率可調?我沒有在手冊里看到可調的方法。

2,、待采信號叫S

發表于 12-25 08:29

ADS1292R采樣率與預期不符,為什么?

高電平, 250, 500采樣率下也是每10秒比預期少3-4次DRDY。中斷和循環讀取的方式都試過。ADS1292R是數據連續讀取模式.

請幫忙分析一下,非常感謝!

發表于 11-20 06:15

淺談影響晶圓分選良率的因素(2)

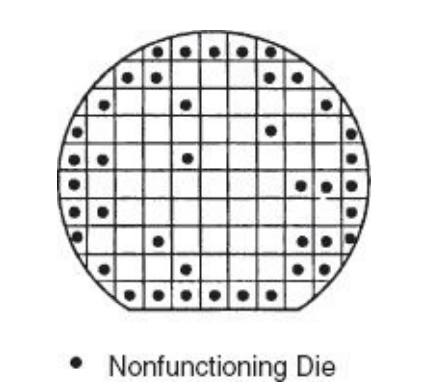

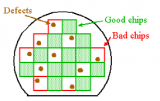

在晶圓制造良率部分討論的工藝變化會影響晶圓分選良率。在制造區域,通過抽樣檢查和測量技術檢測工藝變化。檢查抽樣的本質是并非所有變化和缺陷都被檢測到,因此晶圓在一些問題上被傳遞。這些問題在晶圓分選中顯現為失敗的設備。

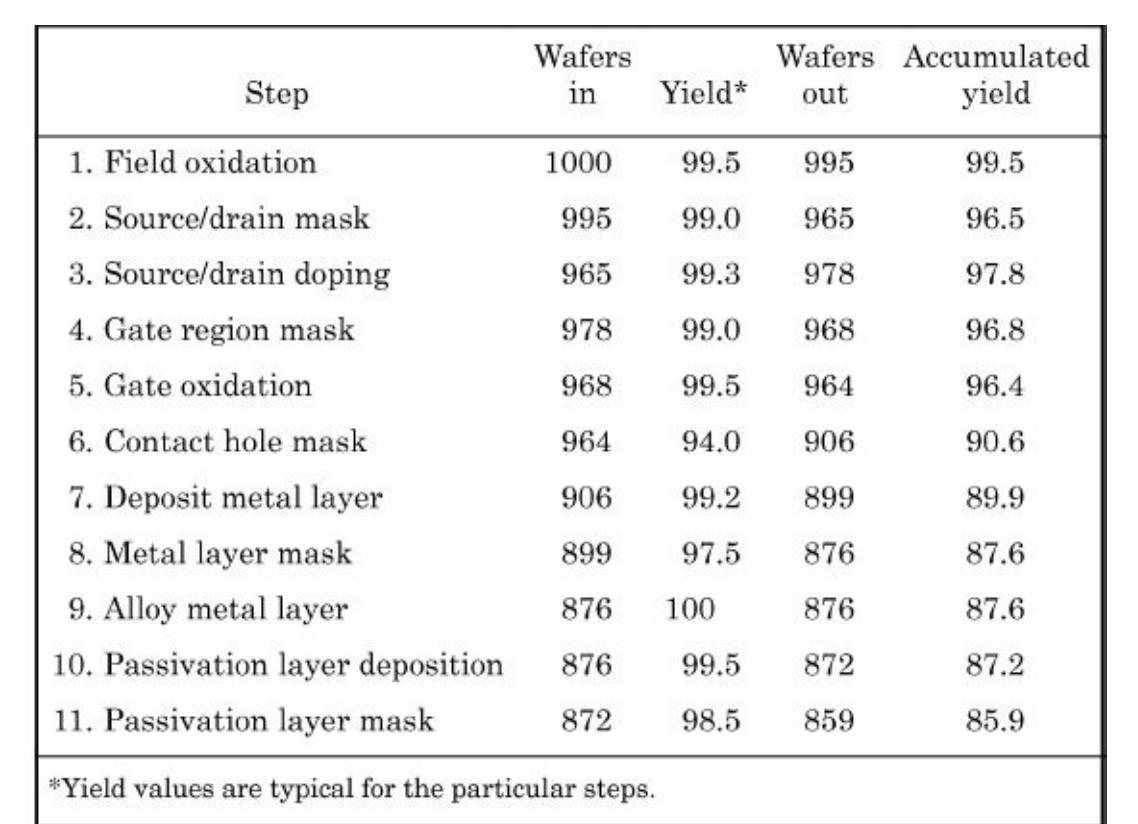

半導體工藝之生產力和工藝良率

晶圓實際被加工的時間可以以天為單位來衡量。但由于在工藝站點的排隊以及由于工藝問題導致的臨時減速,晶圓通常在制造區域停留數周。晶圓等待的時間越長,增加了污染的機會,這會降低晶圓分選良率。向準時制制造的轉變(見后面章節)是提高良

傳三星電子12nm級DRAM內存良率不足五成

近日,據韓國媒體報道,三星在其1b nm(即12nm級)DRAM內存生產過程中遇到了良率不足的挑戰。目前,該制程的良率仍低于業界一般目標的80%~90%,僅達到五成左右。為了應對這一局

ADS中文基礎教程(良率分析)

ADS中文基礎教程(良率分析)

評論