設(shè)計(jì)背景:

在我們?cè)O(shè)計(jì)工程中我們會(huì)用到100M,500M等時(shí)鐘,如果我們的晶振達(dá)不到我們就需要倍頻,再上一個(gè)文檔中我們了解到了分頻,可是倍頻我們改怎么做了,這里我們就用了altera的IP核鎖相環(huán)。

今天我們將去學(xué)習(xí)簡(jiǎn)單的IP核的調(diào)用和生成。

設(shè)計(jì)原理:

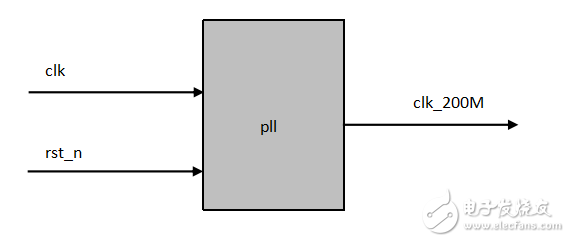

本次的設(shè)計(jì)我們調(diào)用IP核鎖相環(huán)了生成一個(gè)200M的時(shí)鐘,下面我們就來(lái)學(xué)習(xí)和使用簡(jiǎn)單的IP核。

設(shè)計(jì)架構(gòu)圖:

設(shè)計(jì)流程:

新建工程打開(kāi)tools,然后選擇:

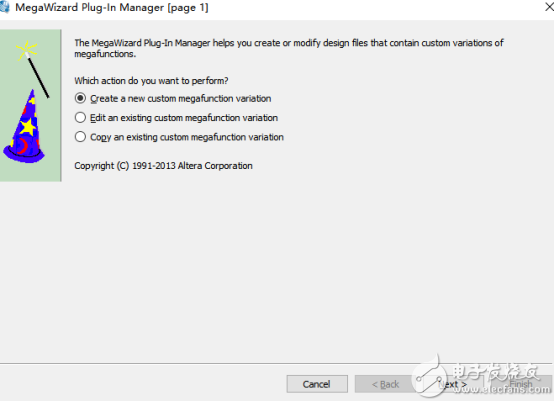

然后出現(xiàn)下面的界面,第一個(gè)句是建立新的IP核,第二個(gè)打開(kāi)你建立好的以便于我們修改,第三個(gè)是復(fù)制一個(gè),我們選擇第一個(gè)選擇,建立一個(gè),然后下一步.

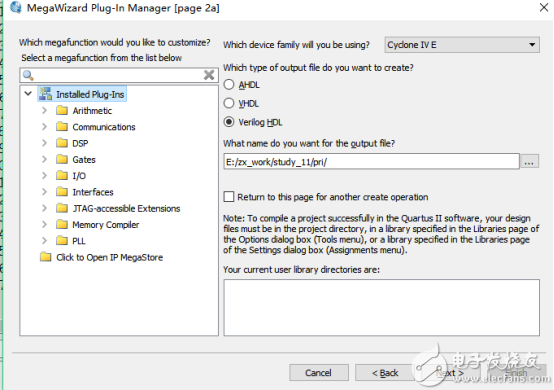

然后跳出下面的界面,我們選擇下面的

然后在右邊選擇我們的語(yǔ)言verilog ,然后給我們建立的IP核起一個(gè)名字。

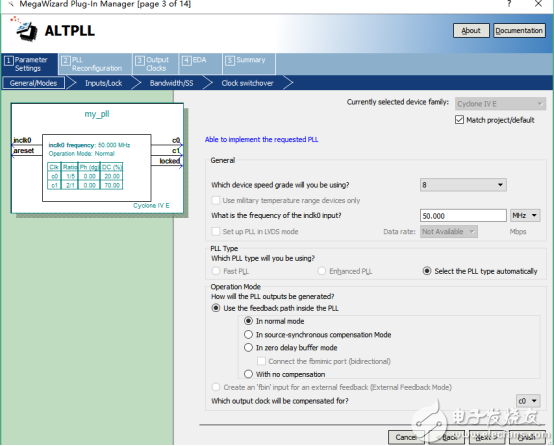

然后跳出下面的界面,inclk0位輸入我們默認(rèn)為50M,areset位復(fù)位高電平有效,c0位輸出,locked位輸出標(biāo)志位,然后輸入我們100M改為50M,下一步。

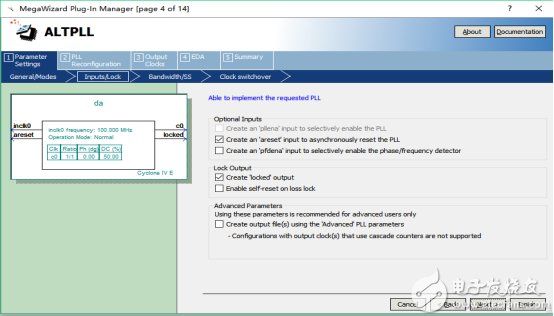

為了只觀的看到各個(gè)引腳的情況,我們下一步,不進(jìn)行操作。

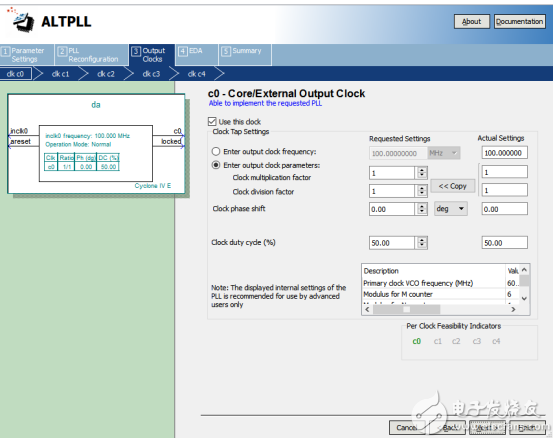

我們可以改我們的輸出時(shí)鐘為多少,可以改輸出時(shí)鐘的相位,占空比,我們寫(xiě)入輸出位200M,占空比為50%,然后下一步。

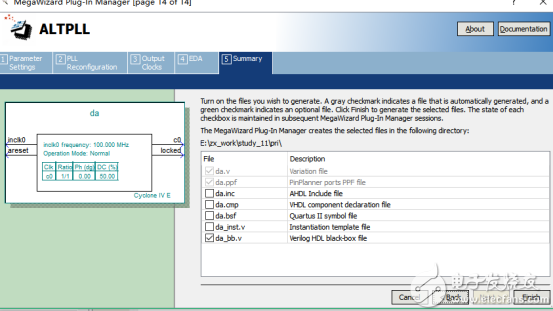

之后不停的下一步,出現(xiàn)下面的界面,就點(diǎn)擊完成Finish,這樣就完成了IP核的建立。

之后我們打開(kāi)我們生成的IP核代碼,然后例化。

設(shè)計(jì)代碼:

設(shè)計(jì)模塊

0modulepll(clk,clk_200M,rst_n,locked);

1inputclk;

2inputrst_n;

3

4outputclk_200M;

5outputlocked;

6

7

8 my_pll my_pll_inst(//例化IP核

9 .areset(~rst_n),

10 .inclk0(clk),

11 .c1(clk_200M),

12 .locked(locked)

13);

14endmodule

測(cè)試模塊

0`timescale1ns/1ps

1

2modulepll_tb();

3regclk;

4regrst_n;

5

7wireclk_200M;

8wirelocked;

9initialbegin

10 clk=1'b1;

11 rst_n=1'b0;

12 #200.1rst_n=1'b1;

13

14 #2000.1$stop;

15

16 end

17

18 always#10clk=~clk;

19 pll pll_dut(

20 .clk(clk),

21 .rst_n(rst_n),

23 .clk_200M(clk_200M),

24 .locked(locked)

25 );

26endmodule

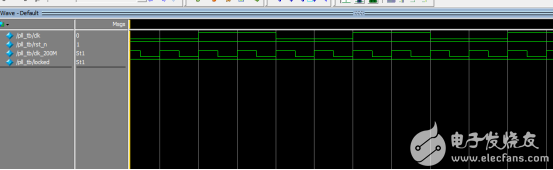

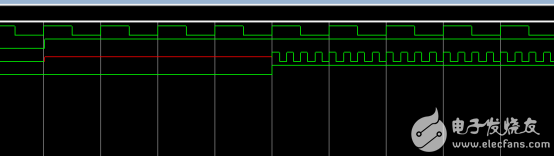

仿真圖:

????

????

在仿真中我們看一看到我們生成的時(shí)鐘是200M,然后我們可以用鎖相環(huán)生成的標(biāo)志位給用200M時(shí)鐘的電路當(dāng)復(fù)位,如下:

-

FPGA

+關(guān)注

關(guān)注

1643文章

21941瀏覽量

613352 -

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

592瀏覽量

88416

發(fā)布評(píng)論請(qǐng)先 登錄

關(guān)于鎖相環(huán)(PLL)的工作原理

FPGA學(xué)習(xí)系列:鎖相環(huán)pll設(shè)計(jì)

LabVIEW鎖相環(huán)(PLL)

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

如何設(shè)計(jì)并調(diào)試鎖相環(huán)(PLL)電路

詳解FPGA數(shù)字鎖相環(huán)平臺(tái)

FPGA學(xué)習(xí)系列:14. 鎖相環(huán)pll設(shè)計(jì)

FPGA學(xué)習(xí)系列:14. 鎖相環(huán)pll設(shè)計(jì)

評(píng)論