鎖相環(huán)英文名稱PLL(Phase Locked Loop),中文名稱相位鎖栓回路,現(xiàn)在簡單介紹一下鎖相環(huán)的工作原理。

鎖相環(huán)通常由鑒相器(PD)、環(huán)路濾波器(LF)和壓控振蕩器(VCO)三部分組成,鎖相環(huán)組成的原理框圖如圖1所示。

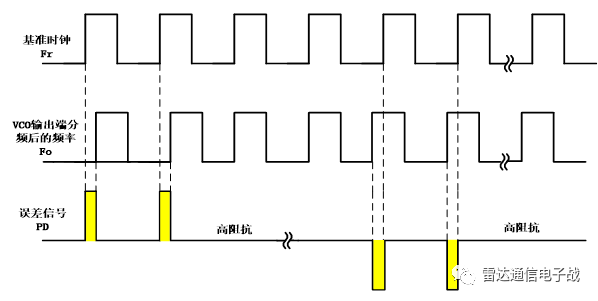

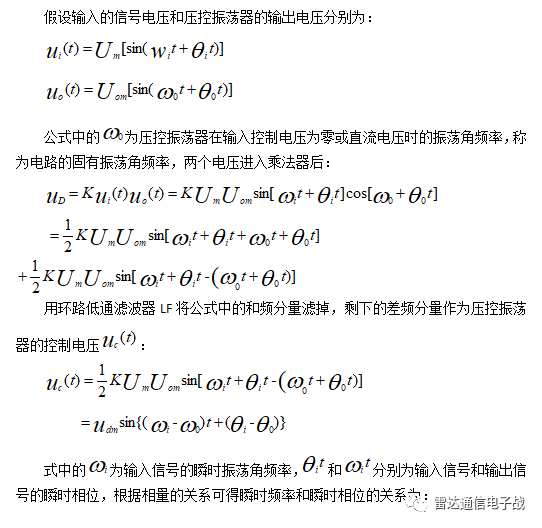

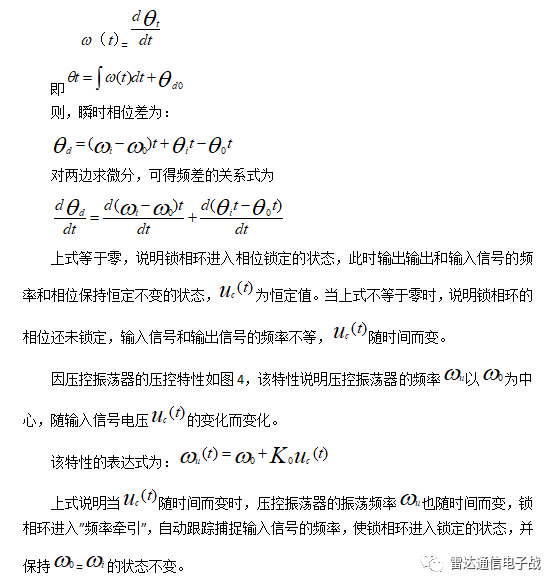

鎖相環(huán)中的鑒相器又稱為相位比較器,它的作用是檢測輸入信號和輸出信號的相位差,并將檢測出的相位差信號(PD),經環(huán)路濾波器濾波后形成電壓VR來控制壓控振蕩器的電壓,該電壓對振蕩器輸出信號的頻率實施控制。 假設外部基準時鐘產生的頻率為Fr,電壓振蕩器VCO產生的頻率為Fo,當Fr和Fo輸入相位比較器的輸入端時,比較器就會輸出比較誤差信號PD,如圖2所示:

當Fr>Fo時,也就是VCO分頻后的振蕩頻率比基準頻率低的時候,此時相位比較器的輸出PD如圖2所示,比較器會輸出正脈沖信號,使VCO的振蕩頻率提高。

當Fr時,也就是vco分頻后的振蕩頻率比基準頻率高的時候,此時相位比較器的輸出pd如圖2所示,比較器會輸出負脈沖信號,使vco的振蕩頻率降低。<>

誤差信號PD通過環(huán)路濾波器的積分,便可以得到直流電壓VR,由于控制電壓VR發(fā)生變化,VOC振蕩頻率會發(fā)生變化,使得Fr=Fo,當Fr=Fo時,誤差信號PD會成為高阻狀態(tài),使得PLL鎖栓。

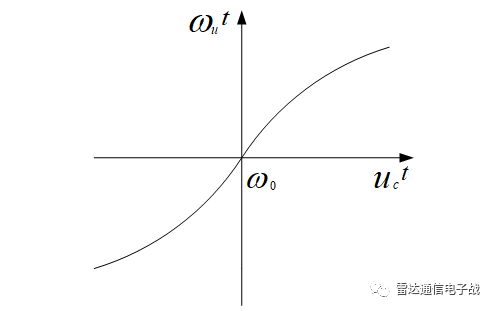

鎖相環(huán)中的鑒相器由模擬乘法器組成的鑒相器電路如圖3所示:

實際應用中,假設外部基準時鐘100MHz,VCO輸出為1000Mhz,那么可以將VOC輸出的頻率進行2分頻為500MHz運用到實際應用電路中,將VOC輸出的頻率進行10分頻為100MHz運用到實際應用電路中,需要單獨輸出一路對VCO進行10分頻到和外部基準時鐘一樣的頻率用來校準VCO輸出的1000Mhz時鐘。

總之,外部的100MHz的基準時鐘不是用來使PLL產生時鐘的,是PLL會產生一個時鐘VCO,但是這個時鐘是一個不穩(wěn)定的時鐘,需要用外界一個穩(wěn)定的晶體時鐘進行校準。

審核編輯:湯梓紅

-

鎖相環(huán)

+關注

關注

35文章

592瀏覽量

88453 -

濾波器

+關注

關注

162文章

8065瀏覽量

180967 -

振蕩器

+關注

關注

28文章

3965瀏覽量

140397 -

pll

+關注

關注

6文章

880瀏覽量

136028 -

鑒相器

+關注

關注

1文章

62瀏覽量

23520

原文標題:關于鎖相環(huán)(PLL)的工作原理

文章出處:【微信號:電子工程師筆記,微信公眾號:電子工程師筆記】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

LabVIEW鎖相環(huán)(PLL)

小數(shù)分頻鎖相環(huán)的工作原理

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

鎖相環(huán)(PLL)電路設計與應用

PLL鎖相環(huán)的基本結構及工作原理

PLL鎖相環(huán)的特性、應用與其基本工作過程

關于鎖相環(huán)(PLL)的工作原理

關于鎖相環(huán)(PLL)的工作原理

評論