聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1643文章

21950瀏覽量

613744 -

Altera

+關注

關注

37文章

799瀏覽量

155425

發布評論請先 登錄

相關推薦

熱點推薦

請問FPGA 中PLL時鐘的問題

請問,想通過FPGA的PLL倍頻產生個500MHz的時鐘來使用,以此時鐘來做定時精密延遲,不知道PLL倍頻倍數有什么要求,比如好像有的器件支

發表于 01-03 17:04

MAX 10 FPGA的特性

10月1日正式開始提供的MAX 10 FPGA的一些特性,我們也來探究一下它是否真的“實至名歸”。圖1 Altera公司產品營銷資深總監Pa

發表于 07-01 08:14

請問FPGA PLL產生的時鐘信號和AD9779A的數據時鐘信號的相位關系?

你們好,

我們正在使用AD9779A進行設計,有如下疑問:

(1) 使用AD9779A的數據時鐘信號(DATACLK)作為FPGA內部PLL的參考時鐘,再用

發表于 12-20 07:12

基于FPGA 的新的DDS+PLL時鐘發生器

針對直接數字頻率合成(DDS)和集成鎖相環(PLL)技術的特性,提出了一種新的DDS 激勵PLL 系統頻率合成時鐘發生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用濾波的方法

發表于 12-14 10:22

?36次下載

Xilinx FPGA普通IO作PLL時鐘輸入

普通IO可以通過BUFG再連到PLL的時鐘輸入上,但要修改PLL的設置 input clk的選項中要選擇"No Buffer";

發表于 02-09 12:54

?7423次閱讀

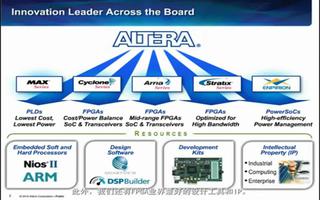

Altera? MAX? 10 FPGA介紹(特性、優勢、電路圖)

控制面板,汽車電子,工業控制和消費類電子產品.本文介紹了Altera MAX 10 FPGA主要優勢,Altera MAX 10

發表于 05-22 10:11

?5733次閱讀

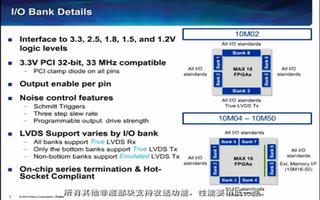

MAX 10 FPGA GPIO的特點優勢

MAX 10 FPGA GPIO培訓,可編程邏輯一般用作膠合邏輯,連接電路板上的大量數字邏輯器件,這些器件通常有不同的I/O標準、電壓電平和協議。這里列出了我們I/O

FPGA設計:PLL 配置后的復位設計

先用FPGA的外部輸入時鐘clk將FPGA的輸入復位信號rst_n做異步復位、同步釋放處理,然后這個復位信號輸入PLL,同時將clk也輸入PLL

發表于 03-29 17:19

?3005次閱讀

用FPGA的鎖相環PLL給外圍芯片提供時鐘

用FPGA的鎖相環PLL給外圍芯片提供時鐘 FPGA鎖相環PLL(Phase-Locked Loop)是一種廣泛使用的

FPGA的時鐘電路結構原理

FPGA 中包含一些全局時鐘資源。以AMD公司近年的主流FPGA為例,這些時鐘資源由CMT(時鐘管理器)產生,包括DCM、

發表于 04-25 12:58

?2572次閱讀

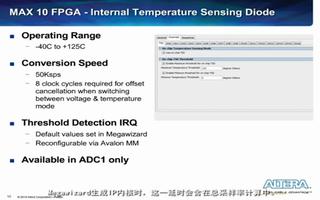

關于MAX 10 FPGA PLL和時鐘特性選項的培訓

關于MAX 10 FPGA PLL和時鐘特性選項的培訓

評論