在嵌入式系統(tǒng)開發(fā)中,硬件電路設(shè)計是確保數(shù)據(jù)可靠性的關(guān)鍵環(huán)節(jié)。本期我們將重點探討硬件設(shè)計中的兩個重要方面:數(shù)據(jù)讀寫保護(hù)和掉電保護(hù)。

?硬件電路設(shè)計

?硬件電路設(shè)計

在嵌入式系統(tǒng)開發(fā)中,硬件電路設(shè)計對于確保數(shù)據(jù)的可靠性和系統(tǒng)的穩(wěn)定性起著至關(guān)重要的作用。電源管理、信號完整性、電磁兼容性(EMC)、數(shù)據(jù)讀寫保護(hù)和掉電保護(hù)等都是硬件電路設(shè)計的關(guān)鍵方面。這些要素相互配合,共同構(gòu)建了一個既可靠又高效的硬件平臺。今天,我們將重點深入探討數(shù)據(jù)讀寫保護(hù)和掉電保護(hù)這兩個至關(guān)重要的環(huán)節(jié)。 ?數(shù)據(jù)讀寫保護(hù)

?數(shù)據(jù)讀寫保護(hù)

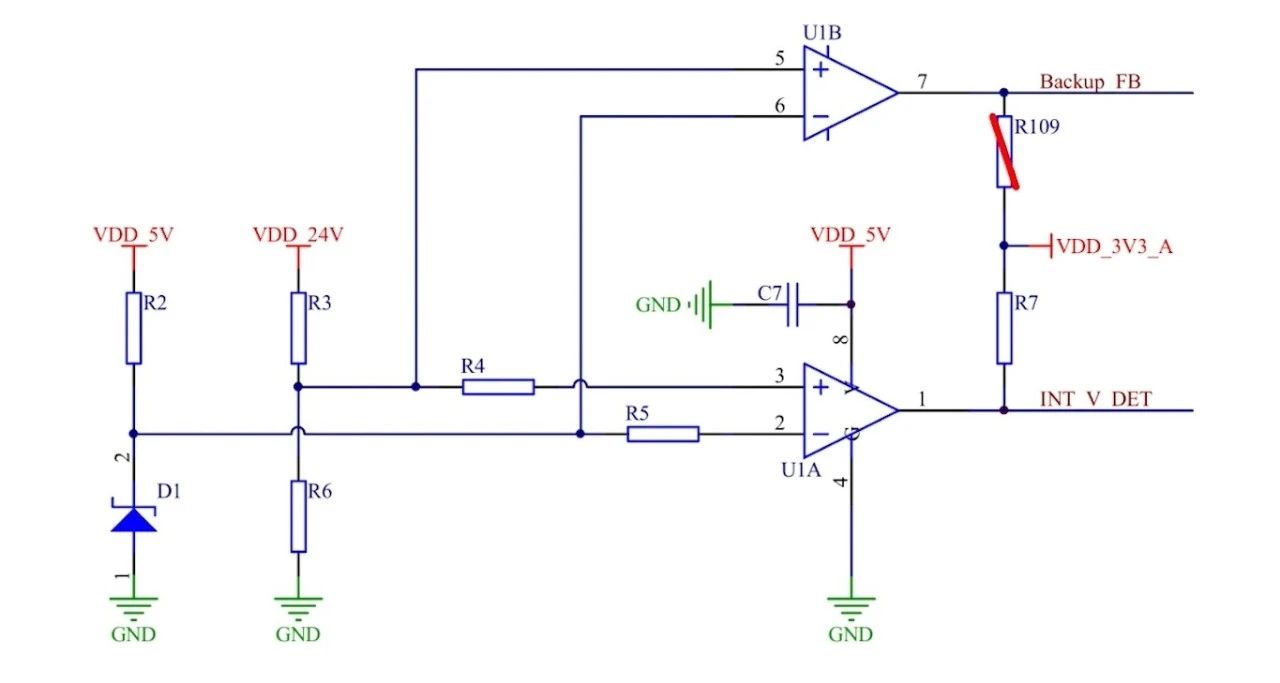

在硬件電路設(shè)計中,數(shù)據(jù)讀寫保護(hù)是確保數(shù)據(jù)完整性和安全性的關(guān)鍵。NAND Flash芯片通常配備一個寫保護(hù)引腳(#WP),但在實際設(shè)計中,許多工程師往往會忽略這個引腳,導(dǎo)致芯片始終處于可寫狀態(tài)。這種設(shè)計存在潛在風(fēng)險,可能會導(dǎo)致數(shù)據(jù)被意外寫入或覆蓋,從而影響數(shù)據(jù)的完整性和可靠性。

圖1 帶NAND寫保護(hù)的電路圖

1. 寫保護(hù)引腳(#WP)的作用

寫保護(hù)引腳(#WP)是NAND Flash芯片的一個重要特性,用于防止數(shù)據(jù)被意外寫入或覆蓋。當(dāng)#WP引腳被設(shè)置為低電平時,芯片進(jìn)入只讀模式,數(shù)據(jù)無法被寫入或修改。當(dāng)#WP引腳被設(shè)置為高電平時,芯片進(jìn)入可寫模式,可以進(jìn)行數(shù)據(jù)寫入操作。

2. GPIO控制#WP引腳

建議在硬件設(shè)計時,使用一個GPIO引腳來控制#WP引腳。這樣可以確保芯片在大多數(shù)時間處于只讀狀態(tài),僅在需要寫入數(shù)據(jù)時才切換到可寫模式。這種設(shè)計不僅提高了數(shù)據(jù)的安全性,還減少了因意外寫入導(dǎo)致的數(shù)據(jù)損壞風(fēng)險。具體實現(xiàn)方法:

HAL_GPIO_WritePin(GPIOx, GPIO_PIN_x,GPIO_PIN_RESET);// 設(shè)置WP引腳為低電平,進(jìn)入只讀模式HAL_GPIO_WritePin(GPIOx, GPIO_PIN_x,GPIO_PIN_SET); // 設(shè)置WP引腳為高電平,進(jìn)入可寫模式

3. 數(shù)據(jù)完整性校驗

除了硬件保護(hù),還可以通過軟件實現(xiàn)數(shù)據(jù)完整性校驗。例如,使用CRC校驗或ECC糾錯技術(shù),確保數(shù)據(jù)在寫入和讀取過程中的完整性。這些技術(shù)可以有效檢測和糾正數(shù)據(jù)傳輸中的錯誤,進(jìn)一步提高數(shù)據(jù)的可靠性。

?掉電保護(hù)

?掉電保護(hù)

掉電保護(hù)是硬件設(shè)計中另一個容易被忽視的環(huán)節(jié)。許多數(shù)據(jù)丟失或系統(tǒng)損壞問題都是由系統(tǒng)異常掉電引起的。通過增加掉電保護(hù)電路,可以有效規(guī)避這些問題。

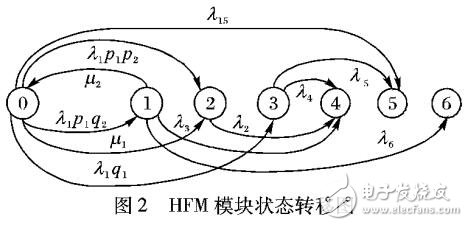

1. 掉電檢測電路

掉電檢測電路可以檢測電源電壓的下降,并向處理器發(fā)送中斷信號。常見的實現(xiàn)方法是使用電壓比較器(如LM393)設(shè)計一個簡單的掉電檢測電路。當(dāng)電源電壓下降到一定值時,電壓比較器輸出低電平,觸發(fā)處理器的中斷引腳。

圖2 掉電檢測電路參考具體實現(xiàn)方法:

- 硬件連接:將電壓比較器的輸出引腳連接到微控制器的一個中斷引腳。

- 軟件處理:在中斷處理函數(shù)中,執(zhí)行數(shù)據(jù)保存和系統(tǒng)關(guān)閉流程。

voidHAL_GPIO_EXTI_Callback(uint16_t GPIO_Pin){ if(GPIO_Pin == GPIO_PIN_x) {// 檢測到掉電中斷 // 保存關(guān)鍵數(shù)據(jù) SaveCriticalData(); // 關(guān)閉系統(tǒng) ShutdownSystem(); }}

2. 后備電源

后備電源可以在主電源中斷時提供足夠的電力,確保系統(tǒng)能夠完成必要的善后工作。常見的后備電源包括超級電容和備用電池。超級電容具有快速充放電的特性,適合短時間的后備電源需求;備用電池則可以提供更長時間的電力支持。具體實現(xiàn)方法:

- 硬件連接:將超級電容或備用電池連接到系統(tǒng)的電源輸入端,并通過一個切換電路確保在主電源中斷時自動切換到后備電源。

- 軟件處理:在系統(tǒng)檢測到掉電中斷后,立即啟動數(shù)據(jù)保存和系統(tǒng)關(guān)閉流程,確保在后備電源耗盡之前完成所有關(guān)鍵操作。

3. 中斷處理

系統(tǒng)接收到中斷信號后,立即啟動數(shù)據(jù)保存和系統(tǒng)關(guān)閉流程。這包括保存關(guān)鍵數(shù)據(jù)、關(guān)閉外設(shè)、關(guān)閉文件系統(tǒng)等操作,確保數(shù)據(jù)的完整性和系統(tǒng)的穩(wěn)定性。具體實現(xiàn)方法:

- 數(shù)據(jù)保存:將關(guān)鍵數(shù)據(jù)寫入非易失性存儲器(如EEPROM或Flash)。

- 關(guān)閉外設(shè):關(guān)閉所有外設(shè),確保它們處于安全狀態(tài)。

- 關(guān)閉文件系統(tǒng):關(guān)閉文件系統(tǒng),確保文件系統(tǒng)的完整性。

voidSaveCriticalData(){ // 將關(guān)鍵數(shù)據(jù)寫入非易失性存儲器 WriteDataToFlash(criticalData);}

voidShutdownSystem(){ // 關(guān)閉外設(shè) ClosePeripherals(); // 關(guān)閉文件系統(tǒng) CloseFileSystem(); // 關(guān)閉系統(tǒng) HAL_PWR_EnterSLEEPMode(PWR_SLEEPENTRY_WFI);}

?ZLG致遠(yuǎn)電子邊緣技術(shù)產(chǎn)品

?ZLG致遠(yuǎn)電子邊緣技術(shù)產(chǎn)品

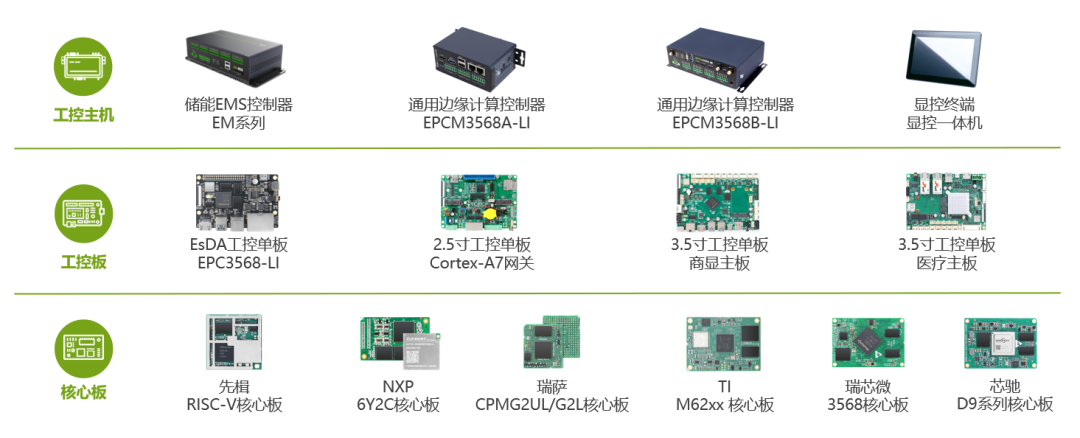

ZLG致遠(yuǎn)電子在設(shè)計產(chǎn)品時,充分考慮了數(shù)據(jù)讀寫保護(hù)和掉電保護(hù)的需求。通過精心設(shè)計的硬件電路,確保了數(shù)據(jù)的可靠性和系統(tǒng)的穩(wěn)定性。我們采用的GPIO控制WP引腳和掉電檢測電路,為數(shù)據(jù)可靠性提供了堅實的硬件基礎(chǔ)。

圖2 ZLG致遠(yuǎn)電子邊緣技術(shù)產(chǎn)品

-

嵌入式

+關(guān)注

關(guān)注

5157文章

19727瀏覽量

318376 -

電路設(shè)計

+關(guān)注

關(guān)注

6713文章

2546瀏覽量

215125 -

硬件電路

+關(guān)注

關(guān)注

39文章

256瀏覽量

29824

發(fā)布評論請先 登錄

硬件電路的可靠性

嵌入式系統(tǒng)產(chǎn)品的可靠性

開發(fā)高可靠性嵌入式系統(tǒng)的技巧有哪些?

如何對嵌入式軟件進(jìn)行可靠性測試

嵌入式軟件可靠性測試方法是什么

嵌入式軟件的安全可靠性控制

嵌入式系統(tǒng)軟件可靠性設(shè)計

嵌入式系統(tǒng)的可靠性設(shè)計

軍用嵌入式系統(tǒng)的可靠性考慮因素

嵌入式系統(tǒng)硬件可靠性分析

高可靠性嵌入式主板設(shè)計

【技術(shù)指南】提升嵌入式數(shù)據(jù)可靠性,從元器件選型開始!

【干貨速遞】嵌入式數(shù)據(jù)可靠性,軟件設(shè)計的這些細(xì)節(jié)不能忽視!

【深度解析】硬件電路設(shè)計:如何確保嵌入式數(shù)據(jù)可靠性?

【深度解析】硬件電路設(shè)計:如何確保嵌入式數(shù)據(jù)可靠性?

評論