對設計的合并可能會很棘手。通常當你需要解決一個問題時,變化會影響設計的其他部分,從而不可避免地會出現其他問題。在2017.3我們推出了一項新功能可以幫助您解決這個問題。該功能被稱作可配置報告。

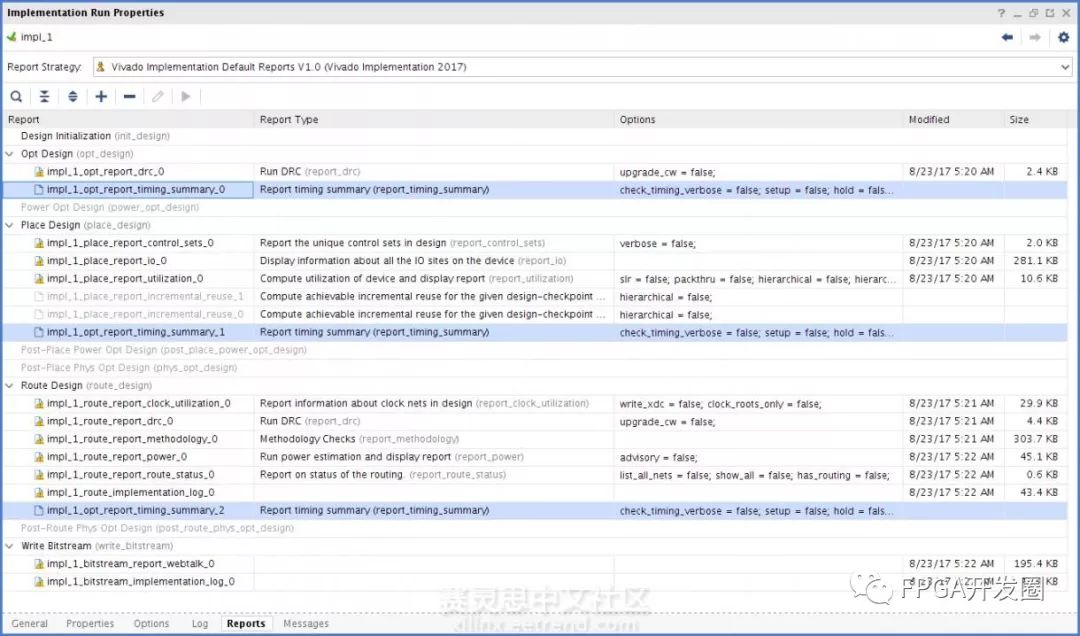

可配置的報告是一項全新的Vivado項目功能,可讓您在流程的任何步驟運行任何報告。例如,假設您在實現后出現一個關鍵路徑,而且您不確定如何解決它。為了理解這條關鍵路徑如何在流程間“演變”,可配置的報告使得您可以在完成邏輯優化,布局設計,布線設計以及這之間的任何步驟報告那條確切路徑的時序情況。圖1顯示了被添加到每個實現流程步驟的報告時序總結。了解每個步驟的時序可以幫助您理解問題是綜合問題,利用率問題,時鐘分配問題還是布線擁塞問題。

圖 1. 在運行實現屬性選項卡中配置時序統計報告在三個流程運行完成之后再生成

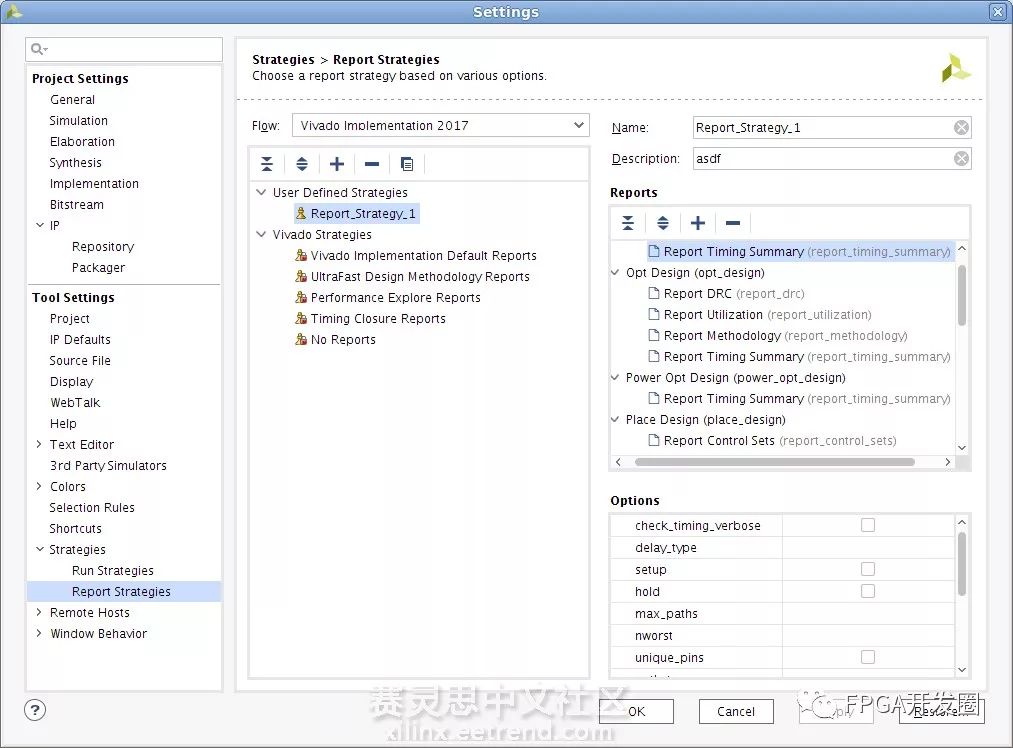

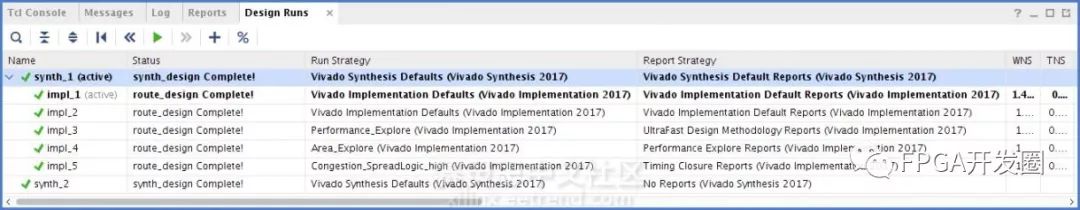

基于上文對可配置報告的描述,我們將介紹報告策略的概念。類似于運行策略允許您調整Vivado的性能以滿足您的獨特需求,報告策略允許您根據您的設計定制報告。 您可以配置報告策略并在不同運行甚至不同項目間復用。我們提供了幾個預先配置的策略,包括:UltraFast方法報告,性能探索報告,時序收斂報告,或者,如果您僅僅想運行的更快,可以選擇no reports選項。圖2顯示了工具設置窗口,用戶可以在其中創建自己的自定義策略或查看Xilinx推薦的策略。圖3顯示了設計運行窗口,其中包含多個配置了不同運行和報告策略的實現和綜合運行。

圖 2. 工具設置窗口,允許用戶創建自己的自定義策略

圖 3. 設計運行窗口顯示了幾種運行和報告策略

可配置的報告可讓您靈活地決定哪些報告對您的設計最為關鍵,并使您能夠專注于解決您的獨特問題。 當你最終推動并結束您的設計時,唯一會遇到的問題就是打開慶祝酒瓶的軟木塞子!“砰!”Bingo!

關于作者Brian Lay是Vivado IDE和支持基礎架構的高級產品營銷經理。作為IDE營銷經理,他曾參與Xilinx許多不同的項目,包括時序約束向導,部分重新配置的項目支持以及運行時硬件調試等。Brian擁有伊利諾伊大學厄巴納-香檳分校電氣工程碩士學位和明尼蘇達大學的本科學位。他曾在Sun Microsystem和Advanced Micro Devices工作過,擁有超過17年的經驗。他的技能包括全定制電路設計,綜合布局布線,時鐘分配設計,全芯片集成以及時序,噪聲,功耗,DRC,IR壓降的各個方面,以驗證CPU,GPU和FPGA中的這些電路。

-

Vivado

+關注

關注

19文章

835瀏覽量

68762

原文標題:Vivado一項全新項目功能——可配置的報告

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Vivado下顯示指定路徑時序報告的流程

求助,如何把一個非CubeMX項目變成STM32CubeMX可配置?

Xilinx 發布Vivado2013.3新增全新設計方法及功能

VIVADO中使用MB如何配置冷啟動

Vivado Design Suite的部分重配置的新功能介紹

如何創建Vivado HLS項目

印刷電路板(PCB)可配置邏輯功能

全新的Vivado項目功能 可配置的報告

全新的Vivado項目功能 可配置的報告

評論