文章來源:學習那些事

原文作者:小陳婆婆

本文介紹了SOI的器件類型、工作原理和制備技術。

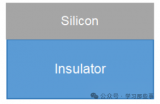

絕緣體上硅(SOI)技術作為硅基集成電路領域的重要分支,其核心特征在于通過埋氧層(BOX)實現有源層與襯底的電學隔離,從而賦予場效應晶體管獨特的電學特性。

本文分述如下

SOI器件類型和工作原理

SOI器件與電路特性優勢

SOI襯底材制備技術

SOI器件類型和工作原理

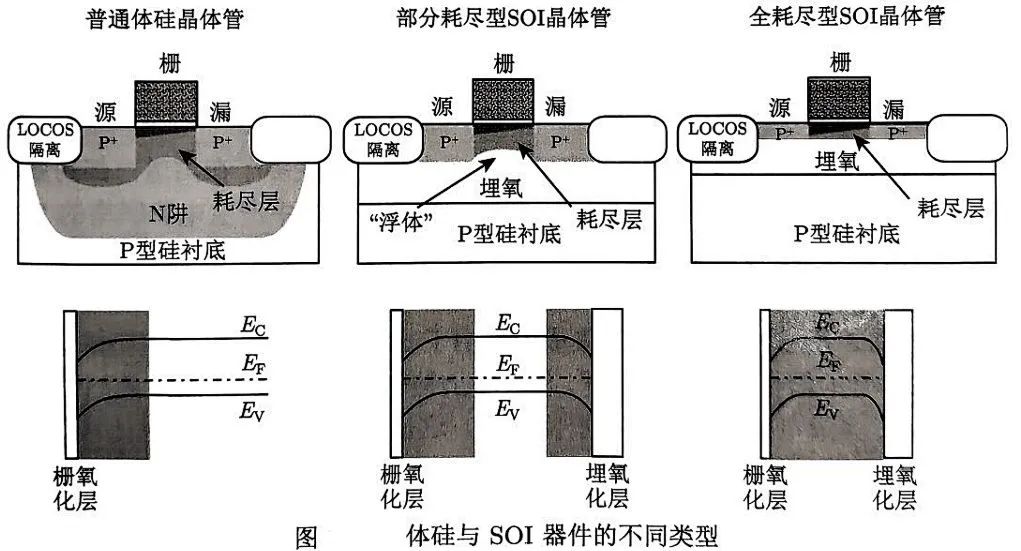

從器件維度分析,SOI技術可劃分為部分耗盡(PD-SOI)與全耗盡(FD-SOI)兩大類別,二者在結構設計與工作機理上呈現顯著差異。

PD-SOI器件的有源層厚度較大,通常超過兩倍最大耗盡層寬度(Tsi> 2Xdmax),其電勢分布特性與體硅器件高度近似,背柵調制效應較弱,閾值電壓的物理模型可沿用傳統體硅器件的表達式,主要依賴頂柵電壓對前溝道的控制。相比之下,FD-SOI器件的有源層厚度極薄(Tsi< 2Xdmax),在正向偏置下可實現全耗盡狀態,形成前后雙柵協同調控的獨特機制,此時電勢分布呈現前溝道與背溝道的強耦合效應,閾值定義需區分耗盡型與積累型兩種工作模式。

當前SOI技術發展呈現兩大趨勢:其一,材料端突破持續深化,超薄硅膜(<10nm)與高k埋氧層的組合方案成為研究熱點,法國CEA-Leti近期報道的12nm FD-SOI技術已實現0.7V低壓下1.8GHz/mW的能效表現;其二,應用場景加速拓展,FD-SOI在射頻前端、低功耗物聯網及汽車電子領域展現顯著優勢。

SOI器件與電路特性優勢

絕緣體上硅(SOI)技術憑借其獨特的器件結構與工作模式,在電學性能、集成可靠性及環境適應性方面展現出顯著優勢。

從核心電學特性來看,SOI晶體管的埋氧層(BOX)將有源區與襯底完全隔離,這一結構帶來雙重效益:其一,源漏結深與結面積得到有效控制,顯著降低短溝道效應及源漏寄生電容,從而提升電路工作頻率與動態響應速度;其二,背柵電極的引入使閾值電壓(VTH)具備動態調控能力,為低功耗電路設計提供了更高的靈活度,該特性在移動計算與物聯網領域已得到廣泛應用,例如AMD基于SOI工藝的CPU便通過背柵偏置技術實現了功耗與性能的優化平衡。

聚焦全耗盡型(FD-SOI)器件,其超薄有源層(Tsi< 2Xdmax)使溝道工作于全耗盡狀態,靜電勢完整因子(EI)較體硅器件提升30%以上,有效抑制了閾值電壓滾降(Roll-off)與漏致勢壘降低(DIBL)效應,在亞10nm工藝節點下仍能維持優異的短溝道控制能力。

相比之下,部分耗盡型(PD-SOI)器件因有源層厚度較大,雖接近體硅器件的電學特性,但易引發浮體效應——多子在溝道區域的積累導致輸出特性出現Kink現象,需通過體接觸或摻雜優化進行抑制,該特性限制了其在高精度模擬電路中的應用。

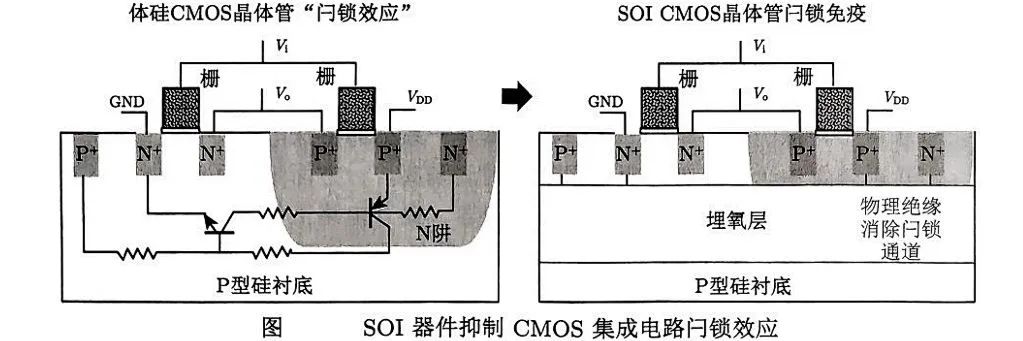

在CMOS集成層面,SOI技術的埋氧層阻斷了寄生PNPN晶體管的形成路徑,從根本上消除了體硅電路中常見的閂鎖效應,顯著提升了電路可靠性。

GlobalFoundries的22FDX工藝平臺通過背柵偏置技術,實現了動態功耗調整功能,在2.5GHz工作頻率下功耗較傳統方案降低30%,該技術已成功應用于汽車電子與5G通信領域。

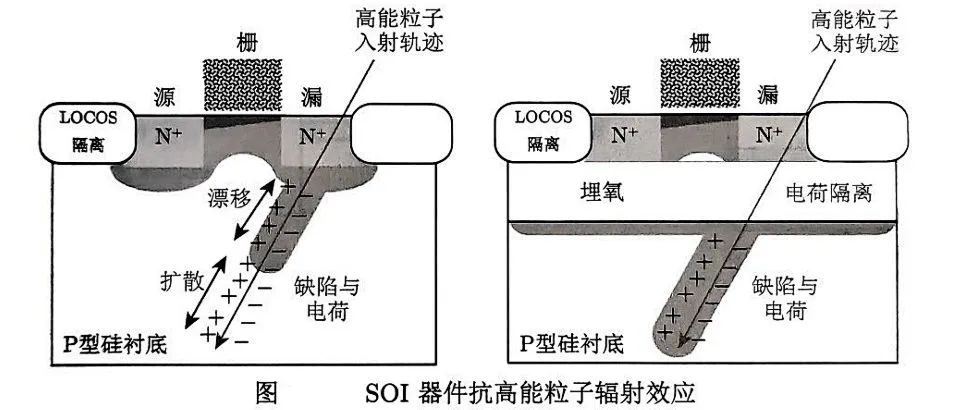

此外,SOI在抗輻射加固方面的優勢尤為突出,埋氧層有效阻隔了高能粒子在襯底中產生的損傷電荷對表面溝道的影響,實驗數據顯示,SOI器件的單粒子翻轉(SEU)敏感度較體硅器件降低兩個數量級,該特性使其成為宇航級集成電路的首選方案,NASA最新一代星載處理器便采用SOI工藝實現了輻射環境下的高可靠性運行。

SOI襯底材制備技術

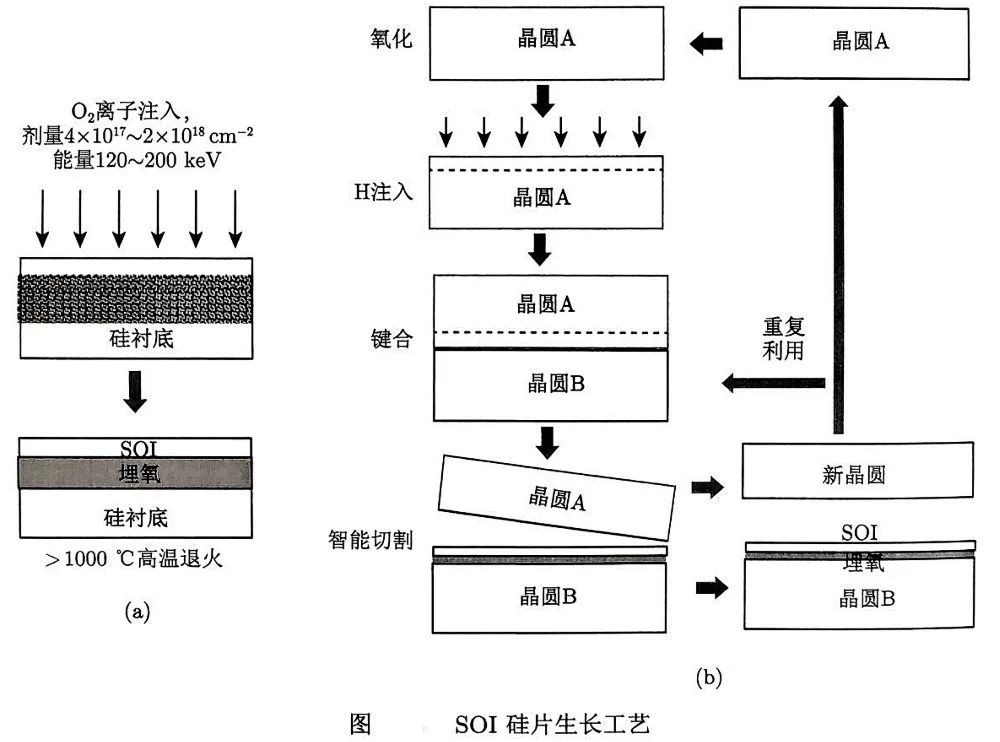

絕緣體上硅(SOI)襯底材料的制備技術因其獨特的層狀結構需求,需采用特殊工藝實現有源層與埋氧層(BOX)的精準構建,其技術復雜度與成本顯著高于傳統體硅晶圓。當前主流制備方案聚焦于注入埋氧(SIMOX)與智能鍵合轉移(Smart-cut)兩大技術路徑,二者在工藝原理、材料特性及量產適用性上呈現差異化特征。

SIMOX技術由日本東芝公司于20世紀80年代率先開發,是首個實現規模化量產的SOI襯底制備方案。其核心工藝流程如下圖(a),在普通硅襯底中高劑量注入氧離子(劑量需達5×101? cm?2以上),隨后通過高溫退火促使注入氧原子與硅基體反應,形成連續的埋氧層。然而,該技術存在固有局限——氧離子注入的濃度分布呈高斯曲線特性,導致表面硅層與埋氧層之間形成較寬的過渡區(通常超過50nm),難以滿足超薄全耗盡型(FD-SOI)器件對陡峭界面及精準厚度控制的需求。此外,高劑量氧注入易引發晶格損傷,雖可通過退火修復部分缺陷,但仍可能對材料電學性能產生微妙影響,限制了其在先進制程節點下的應用拓展。

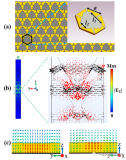

相較之下,法國Soitec公司開發的Smart-cut技術通過氫離子注入與鍵合剝離機制,實現了SOI襯底的高質量制備。其工藝流程如上圖(b):首先在供體硅片A表面生長氧化層作為隔離層,隨后通過低劑量氫離子注入(劑量通常為5×101?~1×101? cm?2)在硅基體內形成斷裂層;將硅片A倒置與受體硅片B鍵合后,經熱處理使氫注入層產生微裂紋,實現硅膜的精準剝離;最終通過化學機械拋光(CMP)對剝離后的硅膜進行平坦化處理,獲得表面質量優異的SOI襯底。該技術的核心優勢在于:氫注入劑量顯著低于SIMOX的氧注入,大幅減少了晶格損傷;斷裂層控制精準,表面硅層與埋氧層界面陡峭度可達納米級(<10nm過渡區),特別適用于超薄FD-SOI晶圓的制備;此外,供體硅片A在剝離后可重復利用,顯著降低了材料成本。目前,Smart-cut技術已成為全球SOI襯底量產的主流方案,支撐了從28nm到12nm節點的FD-SOI工藝開發。

?

-

集成電路

+關注

關注

5429文章

12126瀏覽量

368832 -

汽車電子

+關注

關注

3037文章

8366瀏覽量

170314 -

晶體管

+關注

關注

77文章

10026瀏覽量

141972

原文標題:SOI集成電路技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

絕緣體上硅有什么優點?

科學家在拓撲激子絕緣體相研究取得突破性進展

為什么在絕緣體中,光子會受到“拓撲保護”

首次在零磁場下實現了量子反常霍爾絕緣體的陳數調控

什么是拓撲絕緣體,它有沒有可能替代硅

拓撲絕緣體材料有望成為硅替代品?

為什么會有半導體和導體絕緣體

可再生能源觸發可持續電絕緣體發展

探討一下2D和3D拓撲絕緣體

微帶線兼容的新型拓撲絕緣體結構:助力拓撲器件工程化

一文詳解絕緣體上硅技術

一文詳解絕緣體上硅技術

評論