簡介:本文介紹如何利用FPGA和DMA技術處理來自AD9280和AD9708 ADC的數據。首先,探討了這兩種ADC的特點及其與FPGA的接口兼容性。接著,詳細說明了使用Xilinx VIVADO環境下DMA IP核來實現高效數據傳輸的步驟,包括創建項目、配置ADC接口、添加和連接DMA IP核、設計控制邏輯、生成比特流、軟件開發及系統集成。文章還強調了系統實現中不可或缺的ip_repo文件的重要性和作用。

1. FPGA在數據處理中的應用

在現代數據處理領域,現場可編程門陣列(FPGA)技術因其高性能、低延遲和高度可定制性而成為關鍵技術。FPGA能夠通過硬件加速實現復雜的并行計算,這對于要求高實時性和高效能處理的應用場景尤為關鍵。

FPGA在數據處理中的一個顯著優勢在于其能夠定制邏輯電路來直接處理數據流,從而減少數據在軟件層面上的處理需求。例如,在高速數據采集和信號處理應用中,FPGA可以實現數Gbps級的數據吞吐率,同時還能保證微秒級的低延遲。

在本章節中,我們將探討FPGA如何在數據處理中發揮作用,并分析其在不同行業,如通信、醫療成像、雷達信號處理和金融交易系統中的具體應用案例。我們會從基礎概念出發,逐步深入到FPGA設計的核心要素,并簡述它如何提升系統整體性能。

2. AD9280和AD9708 ADC的主要特性

2.1 AD9280的性能分析

2.1.1 AD9280的參數規格

AD9280是Analog Devices公司生產的8位模數轉換器(ADC),它能夠以最高125 MSPS的采樣率處理信號。AD9280的主要參數規格包括:

采樣速率:125 MSPS(最大)

分辨率:8位

輸入帶寬:130 MHz

模擬輸入范圍:1Vp-p至2Vp-p

電源電壓:+3.3 V單電源供電

功耗:170 mW(典型值)

這些參數規格意味著AD9280適用于處理各種中速、中等精度要求的信號,尤其在成本敏感和功耗受限的應用中非常受歡迎。

2.1.2 AD9280的應用場景

AD9280 ADC特別適合用在便攜式醫療設備、便攜式儀器和通信基礎設施中。其8位分辨率雖然不適用于高性能的圖像和雷達信號處理,但在許多基礎的數據采集和信號處理場景中是足夠的。

由于其低功耗的特點,AD9280也是電池供電設備的理想選擇。例如,在無線傳感器網絡和遠程監控系統中,減少功耗可以顯著增加電池壽命,從而降低維護成本。

2.2 AD9708的性能分析

2.2.1 AD9708的參數規格

AD9708同樣由Analog Devices生產,是一款10位、1 GSPS的高速數模轉換器。它的參數規格包括:

采樣速率:1 GSPS(最大)

分辨率:10位

輸入帶寬:700 MHz

模擬輸入范圍:1Vp-p至2Vp-p

電源電壓:+3.3 V單電源供電

功耗:1.7 W(典型值)

AD9708以其高速度和高精度而聞名,是需要處理高頻信號,如雷達、軟件定義無線電和高速數據采集系統的理想選擇。

2.2.2 AD9708的應用場景

AD9708的高采樣速率和高分辨率使其在需要高性能模擬輸出的場景中具有很高的應用價值。例如,在雷達系統的信號生成中,高采樣率可以產生更高精度的波形,這對于提高目標檢測的精確度至關重要。

在軟件定義無線電(SDR)平臺中,AD9708可以作為FPGA或DSP的數字上變頻器,支持將基帶信號轉換成射頻信號。高精度和高速轉換能力使AD9708成為數字信號處理鏈路中的關鍵組件。

接下來的內容將繼續分析AD9708的應用場景,并探討其與FPGA結合使用的潛力。

3. DMA技術及其在FPGA中的作用

3.1 DMA技術的基本原理

3.1.1 DMA技術的工作機制

直接內存訪問(DMA)是一種允許硬件子系統直接讀寫系統內存的技術,而無需CPU的干預。在FPGA環境中,DMA技術可以極大地提高數據傳輸的效率,因為數據傳輸操作不需要占用寶貴的CPU周期。DMA的工作機制通常涉及以下幾個步驟:

初始化 :DMA控制器被配置以指向內存地址,并指定傳輸數據的大小。

觸發傳輸 :一個硬件信號或軟件命令啟動DMA傳輸。

數據傳輸 :DMA控制器直接管理數據在內存和硬件設備(如ADC)之間的傳輸,CPU可以在此期間執行其他任務。

傳輸完成 :數據傳輸完成后,DMA控制器可以通過中斷或狀態寄存器通知CPU。

3.1.2 DMA技術的優勢分析

DMA技術的優勢在于它提高了數據傳輸的效率和系統的整體性能。主要優勢包括:

減少CPU負擔 :通過卸載內存傳輸任務,CPU可以更加專注于處理任務。

提高傳輸速率 :DMA控制器可以提供比CPU更快的數據傳輸速率,因為CPU不必干預數據傳輸。

降低延遲 :由于CPU不需要參與數據傳輸,系統響應時間縮短,降低了延遲。

支持更大數據量 :DMA可以處理比CPU緩沖區更大的數據量,這對于大數據處理非常重要。

3.2 DMA技術在FPGA中的應用

3.2.1 FPGA與DMA技術的結合

在FPGA中使用DMA技術可以實現高效的數據傳輸和處理。結合FPGA和DMA技術,可以完成高速數據采集、信號處理以及與主機系統的數據交換等任務。FPGA通常包含專用的DMA控制器,或者可以集成專用的IP核來實現DMA功能。

FPGA與DMA結合的架構通常包括以下幾個部分:

FPGA邏輯 :負責硬件邏輯的實現,如數據采集、信號處理等。

DMA控制器 :負責管理內存與FPGA邏輯之間的數據流。

主機系統 :通常是運行控制軟件的計算機,它可以配置DMA傳輸并接收處理后的數據。

3.2.2 DMA技術在數據采集中的角色

在數據采集應用中,DMA技術扮演著核心角色。以FPGA為基礎的采集系統可以使用DMA來實現連續或突發數據的快速、高效傳輸。數據采集系統中,DMA的優勢主要表現在以下方面:

實時數據處理 :DMA允許FPGA快速處理實時數據流,如直接將采集的數據傳輸到內存中的特定緩沖區。

高速傳輸 :通過DMA,FPGA可以實現與主機內存的高速數據交換,這對于高速采樣率來說非常關鍵。

系統資源優化 :DMA減少了CPU在數據傳輸上的工作,使得CPU可以處理其他任務,如用戶界面操作或數據后處理。

3.2.3 使用DMA進行數據傳輸的代碼示例

在本節中,我們將以VHDL代碼為例,演示如何在FPGA設計中實現DMA控制器的一個基本框架。請注意,此代碼示例僅用于展示目的,并非一個完整的DMA控制器實現。

libraryIEEE;useIEEE.STD_LOGIC_1164.ALL;useIEEE.NUMERIC_STD.ALL;-- 使用數值庫entitydma_controllerisPort( clk :inSTD_LOGIC;-- 時鐘信號 reset :inSTD_LOGIC;-- 復位信號 start :inSTD_LOGIC;-- 開始信號 mem_address :outSTD_LOGIC_VECTOR(31downto0);-- 內存地址輸出 mem_data :inoutSTD_LOGIC_VECTOR(31downto0);-- 內存數據 mem_read :outSTD_LOGIC;-- 內存讀使能 mem_write :outSTD_LOGIC;-- 內存寫使能 done :outSTD_LOGIC-- 完成信號 );enddma_controller;architectureBehavioralofdma_controlleris-- DMA控制器的內部信號定義signalcurrent_address :STD_LOGIC_VECTOR(31downto0) := (others=>'0'); signalword_counter :INTEGERrange0to1023:=0; typestate_typeis(IDLE, READ_MEMORY, WRITE_MEMORY, DONE); signalstate : state_type := IDLE;beginprocess(clk, reset) beginifreset ='1'then-- 同步復位邏輯-- ...elsifrising_edge(clk)then-- DMA控制器的主要工作狀態機casestateiswhenIDLE => -- 等待start信號并初始化ifstart ='1'then state <= READ_MEMORY; ? ? ? ? ? ? ? ? ? ? ? ? current_address <= (others?=>'0'); word_counter <=?0; ? ? ? ? ? ? ? ? ? ?endif; ? ? ? ? ? ? ? ?when?READ_MEMORY => -- 從內存讀取數據到FPGA-- ... mem_address <= current_address; ? ? ? ? ? ? ? ? ? ? mem_read <=?'1'; ? ? ? ? ? ? ? ? ? ? state <= WRITE_MEMORY; ? ? ? ? ? ? ? ?when?WRITE_MEMORY => -- 將數據寫回內存-- ... mem_write <=?'1'; ? ? ? ? ? ? ? ? ? ? current_address <=?std_logic_vector(unsigned(current_address) +?4); ? ? ? ? ? ? ? ? ? ? word_counter <= word_counter +?1; ? ? ? ? ? ? ? ? ? ?if?word_counter >=1023then state <= DONE; ? ? ? ? ? ? ? ? ? ?else? ? ? ? ? ? ? ? ? ? ? ? ?state <= READ_MEMORY; ? ? ? ? ? ? ? ? ? ?endif; ? ? ? ? ? ? ? ?when?DONE => -- 完成傳輸,通知系統 done <=?'1'; ? ? ? ? ? ? ? ? ? ?-- ...? ? ? ? ? ? ? ? ? ? ?state <= IDLE; ? ? ? ? ? ?endcase; ? ? ? ?endif; ? ?endprocess;end?Behavioral;

此代碼段描述了一個簡化的DMA控制器狀態機,它可以在FPGA中實現基本的讀寫內存操作。每個狀態下的具體實現細節(例如,讀寫內存的具體邏輯)已省略,但提供了DMA控制器工作流的框架。狀態機在IDLE狀態下等待start信號,然后依次執行讀內存和寫內存操作,直到完成整個數據塊的傳輸,并通過done信號通知系統。

邏輯分析和參數說明

current_address :追蹤當前讀寫內存的地址。

word_counter :記錄當前傳輸的數據字數。

state :控制DMA操作的四個狀態:IDLE(等待),READ_MEMORY(讀內存),WRITE_MEMORY(寫內存),DONE(完成)。

mem_address :輸出到內存的地址信號。

mem_data :內存數據的雙向總線,用于讀寫內存。

mem_read 和mem_write:控制內存讀寫的使能信號。

done :指示DMA傳輸完成的信號。

請注意,實際的DMA控制器實現要復雜得多,需要考慮內存一致性、中斷處理、DMA通道管理等高級特性。此代碼示例提供了一個基礎框架,并突出了DMA控制器的關鍵組成部分。

通過本節內容的分析,我們已經對DMA技術在FPGA中的作用有了基本的理解。下一節,我們將繼續深入探討如何在FPGA設計中利用DMA技術,包括對控制邏輯和采樣數據管理的設計。

4. VIVADO項目創建和配置

VIVADO是Xilinx公司推出的一款綜合設計環境,用于簡化FPGA的開發流程。它提供了一套完整的工具來設計FPGA,包括邏輯設計、仿真、綜合、實現、驗證以及生成用于配置FPGA的比特流。對于任何FPGA項目而言,從項目的創建到配置都是一項基礎而關鍵的任務,直接關系到后續開發的便捷性與項目的成功。本章將詳細介紹如何使用VIVADO創建和配置項目,以確保設計能夠在FPGA上順利實現。

4.1 VIVADO項目的創建流程

VIVADO項目的創建是進行FPGA設計的第一步,它涉及了項目設置、設備選擇、約束文件導入等重要環節。通過一個清晰的創建流程,可以為后續的設計工作打下良好的基礎。

4.1.1 新建VIVADO項目

打開VIVADO軟件后,首先映入眼簾的是啟動界面,該界面提供了一個友好的入口來創建新的項目。

選擇項目類型:在啟動界面點擊“Create New Project”,然后選擇“RTL Project”作為項目類型,這表示項目將以硬件描述語言(HDL)為主要設計輸入。

輸入項目名稱和位置:在彈出的項目名稱對話框中,為你的項目命名,并選擇項目文件的存儲路徑。一個清晰的項目名稱和合理的項目路徑有助于提高工作效率。

指定RTL源文件:如果之前已經有設計文件,可以選擇“Add Sources”將它們導入到項目中。

選擇目標FPGA設備:下一步需要選擇目標FPGA設備。VIVADO會顯示一個器件選擇對話框,根據設計要求選擇合適的FPGA芯片型號。

添加仿真源文件(可選):如果打算進行設計的仿真驗證,可以在此步驟中添加仿真源文件。

完成項目創建:完成以上設置后,點擊“Finish”按鈕,VIVADO將創建項目并打開設計的主界面。

4.1.2 項目配置參數設置

項目創建完成后,需要對其進行必要的配置。這些配置包括添加約束文件,設置綜合和實現策略等。

添加約束文件:約束文件(如XDC文件)定義了設計中特定信號的引腳位置、時鐘約束等。在VIVADO中,可以通過“Add Sources”->“Add or Create Constraints”添加或創建約束文件。

設置綜合策略:在綜合設置中可以定義優化目標,例如性能優化(速度優先)或面積優化(成本優先)。

配置實現策略:實現階段包含綜合后的布局布線(Place & Route)。此階段的配置涉及時序約束、功耗約束等,這些對于最終設計的性能至關重要。

4.2 VIVADO項目中的配置

在項目創建和初步配置完成后,深入到項目的配置細節,可以更有效地控制設計的實現過程,確保FPGA設計的成功。

4.2.1 FPGA的引腳布局

FPGA的引腳布局對于硬件接口的正確連接至關重要。VIVADO提供了引腳規劃工具,可以直觀地進行引腳分配。

打開引腳規劃工具:在項目導航器中,點擊“IP Catalog”,然后選擇“Constraints”下的“I/O Planning”。

導入引腳約束:如果已經有引腳約束文件(.UCF/.XDC),可以直接導入。否則,可以手動分配引腳,并設置必要的電氣特性(如上拉/下拉電阻、驅動強度等)。

保存并驗證引腳配置:完成引腳分配后,確保保存配置,并使用VIVADO的驗證工具檢查配置是否有誤。

4.2.2 時鐘域和資源分配

對于涉及多個時鐘域或需要高效利用FPGA資源的設計,合理的時鐘管理和資源分配是關鍵。

時鐘域管理:使用VIVADO的時鐘向導(Clocking Wizard)IP核可以方便地生成所需的時鐘信號。在項目中添加該IP核,并根據設計需求配置時鐘參數。

資源分配:對于特定功能模塊,如DSP單元、存儲器塊(BRAM)或高速串行收發器(如GTX/GTH),要合理規劃它們的使用,避免資源沖突。可以通過資源利用率報告和可視化的分配圖來輔助這一過程。

資源利用率報告:VIVADO提供了資源利用率報告,其中詳細列出了所有可用資源的使用情況。通過分析這些報告,可以發現資源使用上的瓶頸并進行優化。

下面的示例代碼塊展示了如何在VIVADO中創建一個簡單的時鐘約束:

# 創建一個新的時鐘約束create_clock-period10.000-name sys_clk[get_ports sys_clk]

在這段TCL代碼中: -create_clock是VIVADO中定義時鐘約束的命令。 --period10.000表示定義的時鐘周期為10納秒,即頻率為100MHz。 --namesys_clk是給時鐘信號命名。 -[get_ports sys_clk]表示這個時鐘約束應用于名為sys_clk的端口。

通過以上創建和配置流程,可以完成VIVADO項目的基礎工作,為FPGA設計的后續開發提供了一個扎實的平臺。

5. ADC接口與DMA IP核的配置和連接

在FPGA系統設計中,ADC(模擬-數字轉換器)接口的配置和DMA(直接內存訪問)IP核的集成是數據處理和傳輸的關鍵步驟。這確保了模擬信號可以被精確地轉換成數字形式,并高效地傳輸到數據處理單元或存儲器中。

5.1 ADC接口的配置

5.1.1 AD9280接口配置

AD9280是一款8位的高速模數轉換器,具有80MSPS的采樣率。其接口配置通常包括差分時鐘信號(CLK+/-)和數據輸出接口(D0-D7)的設置。

flowchart LR CLK[CLK+/-] -->|差分時鐘輸入| ADC[AD9280] D[模擬信號] -->|模擬輸入| ADC ADC -->|數據輸出| FPGA[FPGA]

在配置AD9280時,需要注意其時鐘和數據線的電氣特性,以及如何通過SPI接口對其內部寄存器進行配置,以調整其采樣率和輸出格式。

5.1.2 AD9708接口配置

AD9708是一款14位的高速電流輸出DAC(數字-模擬轉換器),具有125MSPS的更新率。AD9708的配置需要關注數據接口(D0-D13)、數據時鐘(I/O UPDATE)和參考電壓(IREF)等信號線。

flowchart LR DATA[D0-D13] -->|數據輸入| DAC[AD9708] CLK[I/O UPDATE] -->|數據時鐘輸入| DAC REF[IREF] -->|參考電壓| DAC DAC -->|模擬輸出| A[模擬信號]

根據數據手冊的指導,配置AD9708的工作模式和輸出電流范圍,是確保其正確工作的重要步驟。

5.2 DMA IP核的集成與配置

5.2.1 DMA IP核的參數設置

集成DMA IP核到FPGA設計中,可以減少CPU的負擔,直接將數據從ADC傳輸到FPGA內存或外部存儲器。在VIVADO中,可以使用IP Catalog來集成DMA IP核,并進行相應的配置。

{"DMA_IP_Core_Config":{"AXI.stream_width":"64","Memory_map_data_width":"32","Max_transfer_bytes":"1048576","Use_read_performance_counter":"1","Use_write_performance_counter":"1"}}

上述JSON片段表示了DMA IP核配置中的一些關鍵參數,包括AXI流數據寬度、內存映射數據寬度、最大傳輸字節數以及性能計數器的使用。

5.2.2 DMA與ADC的邏輯連接

DMA IP核需要與ADC的數據輸出接口進行邏輯連接。這通常通過FPGA內部的邏輯資源完成,可能涉及到了多個AXI總線接口的橋接和路由。

// 偽代碼示例:連接DMA與ADCaxi_stream_ifadc_data(); // ADC數據接口axi_stream_ifdma_data(); // DMA數據接口// ADC到DMA的數據路由axi_stream_route( .adc_data(adc_data), .dma_data(dma_data), .route_enable(1'b1) );// DMA控制信號配置dma_controller( .clk(clk), .rst(rst), .route_enable(route_enable), // 其他控制信號...);

在上述Verilog代碼示例中,我們定義了ADC數據接口和DMA數據接口,并通過axi_stream_route函數將它們連接起來。dma_controller模塊負責配置DMA IP核和控制信號。

通過這樣的配置和連接,系統能夠實時地處理和傳輸ADC采集到的數據,而不占用CPU資源,從而提高了整體系統的效率。

-

FPGA

+關注

關注

1646文章

22063瀏覽量

619374 -

接口

+關注

關注

33文章

9029瀏覽量

153863 -

adc

+關注

關注

99文章

6720瀏覽量

549503 -

數據采集

+關注

關注

40文章

7225瀏覽量

116650

原文標題:FPGA利用DMA IP核進行AD9280/AD9708 ADC數據采集的實現方法

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

利用FPGA自帶的IP核實現雙口RAM用于2片MCU進行數據交換時多次讀數據后RAM中數據變為了0

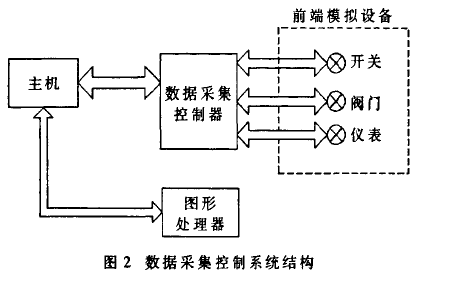

基于FPGA的數據采集控制器IP核的設計方案和實現方法研究

FPGA實現數據采集的方式對比(傳統串口、數據采集卡及外設計接口)

基于PCIe DMA的多通道數據采集和回放IP

如何利用PCIe DMA總線實現一個基于FPGA的PCIe 8位數據采集卡?

ARM系統中DMA方式在數據采集中的應用

在FPGA中利用IP核實現SOC系統中的串口收發接口的設計

如何使用FPGA進行仿真系統數據采集控制器IP核設計的資料概述

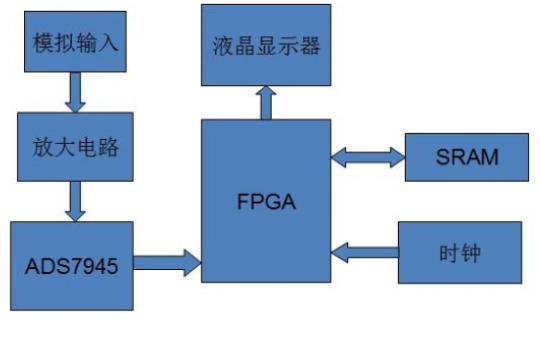

如何使用FPGA實現ADC采集系統的設計

FPGA利用DMA IP核實現ADC數據采集

FPGA利用DMA IP核實現ADC數據采集

評論