文章來源:學習那些事

原文作者:小陳婆婆

本文介紹了不同2.5D和3D集成技術中的熱評估。

在多芯片封裝趨勢下,一個封裝內集成的高性能芯片日益增多,熱管理難題愈發凸顯。空氣冷卻應對此類系統力不從心,致使眾多硅芯片閑置(停運或降頻),而且高、低功率芯片間的熱耦合還會拉低系統整體性能。可見,新集成架構雖具電氣優勢,但散熱問題亟待解決。

目前,已有諸多文章針對不同集成技術開展熱分析與優化研究,如基于硅轉接板的2.5D集成、基于TSV的集成以及單片3D IC集成,但針對基于橋接芯片的2.5D集成平臺的熱學建模研究不多。

本文重點介紹兩方面的內容:一是剖析基于硅橋芯片2.5D集成的熱性能,并與其他2.5D和3D解決方案對比;二是深入探究該集成方式,評估不同工藝參數對熱性能的影響,助力行業明晰硅橋集成技術的熱邊界與挑戰。此外,本文還將介紹一種基于后道工藝(BEOL)埋入式集成方案,有望改善 EPB 并降低芯片間延遲。

2.5D集成和3D集成典型架構

不同2.5D集成方案的熱性能對比

2.5D與3D集成的熱性能對比

多片式3D集成

2.5D集成和3D集成典型架構

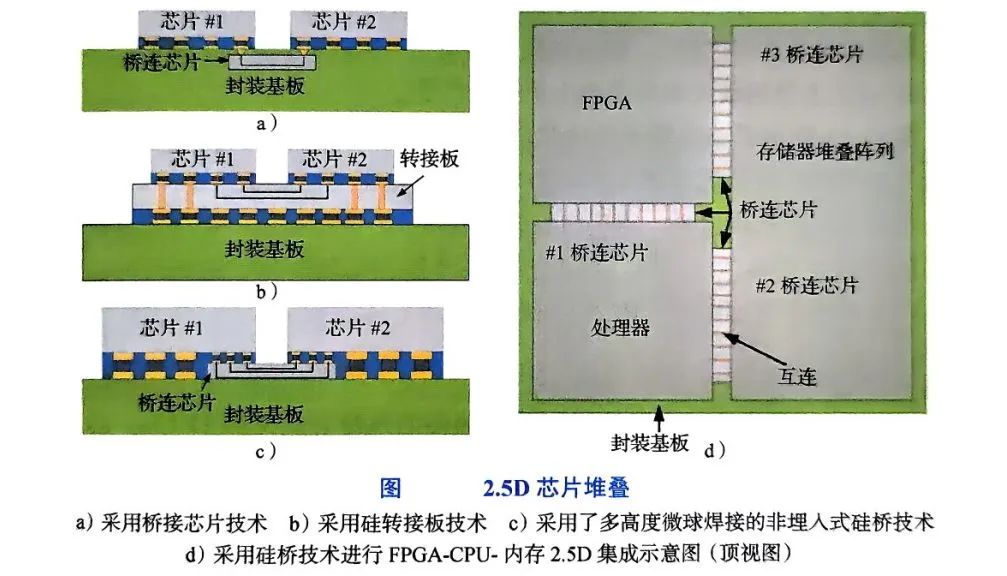

在集成電路封裝領域,2.5D與3D集成技術正通過垂直堆疊與高密度互連突破傳統物理限制,成為AI、HPC等高性能計算場景的核心解決方案。以下從技術架構、應用案例及行業趨勢三個維度進行介紹:

2.5D集成:硅橋接芯片重構橫向互連效率

2.5D集成的本質是在基板與芯片間引入中介層(Interposer),通過硅轉接板上的TSV通孔與微凸點(Micro-Bump)實現芯片間橫向互連。以FPGA-CPU-內存芯片構成的微系統為例,硅橋接芯片可埋入有機封裝基板(如Intel EMIB技術)或直接置于有源芯片與封裝層之間(如臺積電CoWoS-S)。

這種架構的優勢在于:

信號延遲降低:中介層提供比傳統基板更短的互連路徑,例如英偉達H100 GPU通過CoWoS封裝將HBM3與GPU芯片的傳輸延遲壓縮至納秒級;

異構集成靈活性:支持不同工藝節點芯片(如5nm CPU與28nm FPGA)的混合封裝,AMD EPYC處理器通過3D堆疊整合計算芯粒與緩存,性能提升40%;

成本可控性:相比3D集成,2.5D無需復雜TSV蝕刻工藝,良率更高。臺積電2024年CoWoS產能擴張至每月4萬片,支撐英偉達A100/H100等AI芯片需求。

行業最新進展顯示,混合鍵合(Hybrid Bonding)技術正取代傳統微凸點,實現10μm以下間距的垂直互連。臺積電SoIC技術已量產,英特爾Foveros Direct采用類似方案,將帶寬密度提升至1TB/s/mm2,較微凸點提升10倍。

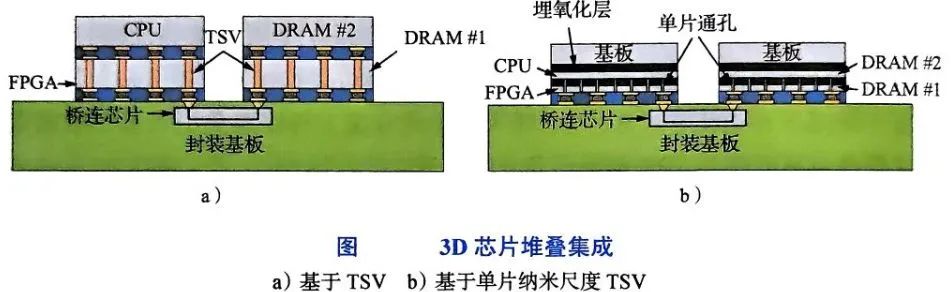

3D集成:TSV驅動垂直堆疊密度革命

3D集成通過TSV實現芯片層間垂直互連,分為“帶中介層”與“單片式”兩種架構:

基于TSV的3D集成:邏輯芯片與存儲芯片(如DRAM)通過TSV直接堆疊,三星X-Cube技術已實現8層HBM3與GPU的垂直互聯,堆疊密度達10?/mm2。該架構面臨熱應力集中挑戰,需采用碳化硅散熱片與液冷方案,例如湖南大學提出的低溫單片式三維異構集成工藝,將熱預算降低30%。

單片式3D集成:通過標準光刻工藝依次處理多個有源器件層,實現芯片內部垂直互連。華盛頓大學研究顯示,該技術可使芯片尺寸減半,互聯線總長度減少2/3。但目前受限于層間對準精度(<1nm)與工藝兼容性,尚未大規模量產。

以CPU-FPGA-DRAM構成的微系統為例,3D堆疊可實現:

計算與存儲協同優化:CPU與FPGA通過TSV垂直互聯,減少數據搬運能耗;DRAM堆疊提供TB/s級帶寬,突破“存儲墻”限制;

能效比提升:3D集成使信號傳輸距離縮短90%,蘋果M1 Ultra采用UltraFusion架構實現雙芯片互連,帶寬達2.5TB/s,功耗降低20%。

技術演進趨勢:從架構創新到生態協同

材料多元化:硅中介層主導高性能場景,玻璃基板因熱膨脹系數可調(CTE<5ppm/℃)與低成本潛力(較硅中介層降低40%)成為新方向,英特爾已推出玻璃基板封裝測試方案;

標準化推進:UCIe聯盟推動芯粒(Chiplet)互聯接口統一,加速2.5D/3D生態構建。AMD、英偉達等企業通過開放Chiplet庫,縮短產品開發周期50%以上;

國內突破:長電科技XDFOI 2.5D封裝技術已用于4nm Chiplet芯片,通富微電7nm/5nm方案量產,但高端工藝(如混合鍵合)仍依賴進口設備,需加強產業鏈協同。

不同2.5D集成方案的熱性能對比

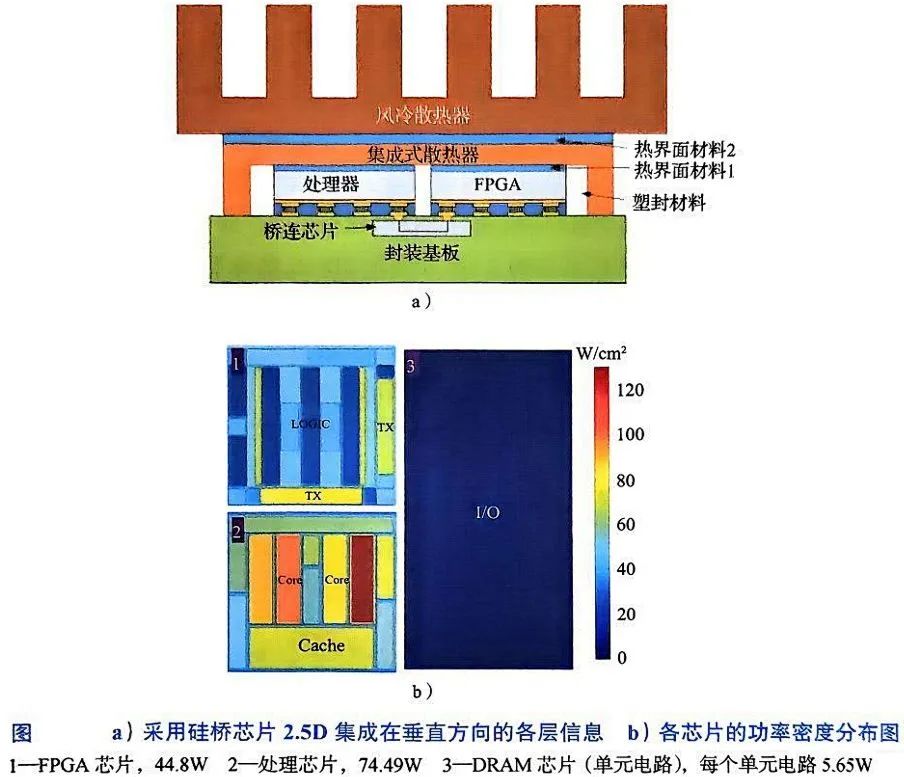

在先進封裝技術的熱管理領域,2.5D集成方案的熱性能優化始終是工程落地的關鍵挑戰。

本文基于風冷散熱系統(圖a),對轉接板、未埋入橋接芯片、含橋接芯片三種典型2.5D架構展開對比分析,所有熱模型均采用圖b所示的最大功率分布工況進行穩態仿真,以精準定位系統級熱瓶頸。

核心散熱路徑的共性特征

三種方案的熱流分布呈現顯著的一致性:超過97%的熱量通過頂部散熱器導出(轉接板方案97.17%、未埋入橋接芯片97.19%、含橋接芯片98.18%)。這一數據揭示了2.5D集成的本質熱傳導邏輯——硅轉接板或橋接芯片僅作為信號互連中介,其材料導熱系數(k≈150 W/m·K)雖遠高于有機基板(k≈1-3 W/m·K),但因厚度有限(通常<100μm),對縱向熱阻的貢獻不足3%。因此,所有方案的熱特性均由頂部散熱器的對流換熱效率主導,這解釋了為何三者結溫差異僅在±2℃范圍內波動。

二次散熱路徑的差異化影響

盡管主散熱路徑高度相似,但三種方案的二次散熱路徑差異導致結溫出現細微分化:

轉接板方案:熱量通過硅轉接板邊緣傳導至封裝基板,再經基板底面自然對流散失。由于硅與有機基板的界面熱阻較高,該路徑僅貢獻2.83%的散熱量,但局部熱點(如轉接板邊緣)溫度較中心區域高3-5℃,需通過優化基板銅箔布局緩解。

未埋入橋接芯片方案:橋接芯片直接暴露于封裝腔體內,其背面與基板間填充的TIM材料(k≈5 W/m·K)形成額外散熱通道。仿真顯示,該路徑使橋接芯片結溫降低1.2℃,但因TIM厚度均勻性難以控制(±10μm偏差導致熱阻波動15%),量產穩定性面臨挑戰。

含橋接芯片方案:通過將硅橋接芯片嵌入基板內部,利用基板預埋銅柱(k≈400 W/m·K)構建低熱阻路徑。該設計使橋接芯片的散熱份額提升至1.82%,結溫較轉接板方案降低0.9℃,且溫度梯度更平緩(ΔT<8℃),但需解決基板層壓工藝中的空洞缺陷(孔隙率需<1%以避免熱阻激增)。

橫向熱耦合的工程影響

所有方案均因導電通孔(TSV/微凸點)的存在表現出顯著的橫向熱耦合效應。例如,在FPGA-CPU-內存芯片組中,CPU芯片產生的熱量通過硅轉接板中的TSV傳導至相鄰FPGA芯片,導致FPGA邊緣區域溫度升高2-3℃。這種耦合效應在3D集成中更為突出(如HBM堆疊中DRAM芯片間的熱串擾可達5-8℃),但在2.5D場景下,通過調整芯片間距(建議>200μm)或引入石墨烯散熱片(k≈1500 W/m·K)可有效抑制。

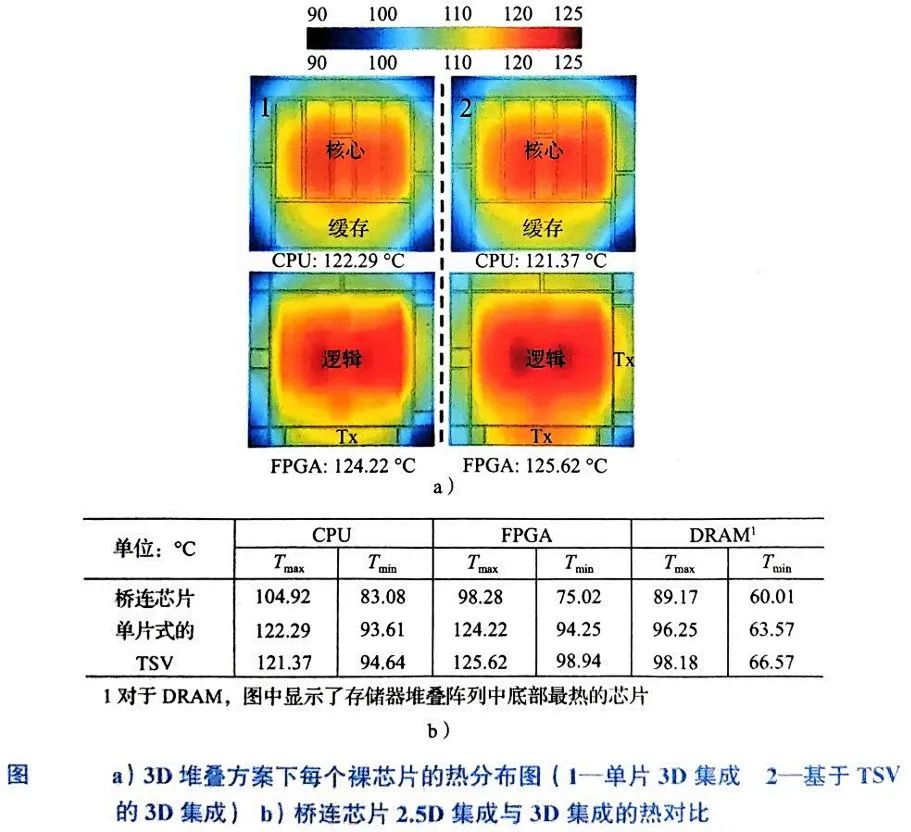

2.5D與3D集成的熱性能對比

在先進封裝領域,2.5D與3D集成的熱性能對比始終是工程落地的核心挑戰。以AI加速器、HPC芯片等高功率密度場景為例,相同配置和工況下,3D堆疊集成因芯片垂直堆疊導致功率密度較2.5D方案激增30%-50%,熱管理難度呈指數級上升。

以上圖b數據為基準,基于橋接芯片的2.5D集成最大結溫溫升較兩種典型3D IC方案低8-12℃,這一差異源于2.5D架構通過中介層將熱量分散至散熱器頂面的路徑效率更高——其97%以上的熱量通過頂部散熱器導出,而3D集成因芯片間直接堆疊,橫向熱耦合效應增強,導致局部熱點溫度飆升。

3D集成的熱耦合機制與散熱瓶頸

3D集成的熱問題本質源于物理結構與材料特性的雙重約束。以上圖a所示CPU-FPGA 3D堆疊為例,芯片間通過TSV或混合鍵合實現垂直互連,但硅基材料的熱導率(k≈150 W/m·K)遠低于銅(k≈400 W/m·K),導致垂直熱阻占系統總熱阻的60%以上。此外,3D集成中芯片間距通常小于50μm,遠低于2.5D方案的200-500μm,使得橫向熱擴散路徑縮短,熱耦合效應顯著增強。實驗數據顯示,3D堆疊中相鄰芯片的溫差可低至5℃,但熱點溫度較2.5D方案高15-20℃,這種“均勻高熱”特性對散熱設計提出更高要求。

單片3D集成(如Monolithic 3D)的熱性能進一步惡化。由于有源層厚度僅50-100nm(較TSV-based 3D的10-50μm更薄),熱傳導路徑縮短導致熱量在芯片內部積累,散熱效率較TSV方案降低20%-30%。不過,其FPGA到散熱器的熱阻因直接鍵合工藝(如銅-銅混合鍵合)較TSV方案降低15%,部分抵消了散熱劣勢,最終最高溫度較TSV 3D低3-5℃。

2.5D集成的熱優勢與工程實踐

2.5D集成的熱性能優勢源于其“平面化+垂直傳導”的混合散熱路徑。以臺積電CoWoS-S為例,硅中介層通過TSV將熱量垂直傳導至封裝基板,再經基板底面的TIM材料(如燒結銀,k≈30 W/m·K)傳遞至散熱器,形成“芯片-中介層-基板-散熱器”的多級散熱網絡。這種結構使熱量分布更均勻,局部熱點溫度較3D方案低10-15℃,且因工藝成熟(如EMIB技術良率已達95%以上),量產穩定性顯著優于3D集成。

行業最新實踐進一步驗證了2.5D的熱管理優勢。AMD MI300X加速器采用液冷中介層設計,將8顆HBM3堆棧的熱點溫度控制在85℃以下,較3D堆疊方案(如HBM3E的12層DRAM堆疊)低20-25℃。此外,2.5D方案通過優化基板銅箔布局(如增加熱通孔密度至40%以上)和引入高導熱材料(如石墨烯散熱片,k≈1500 W/m·K),可將功率密度提升至500 W/cm2以上,滿足7nm及以下制程芯片的散熱需求。

多片式3D集成

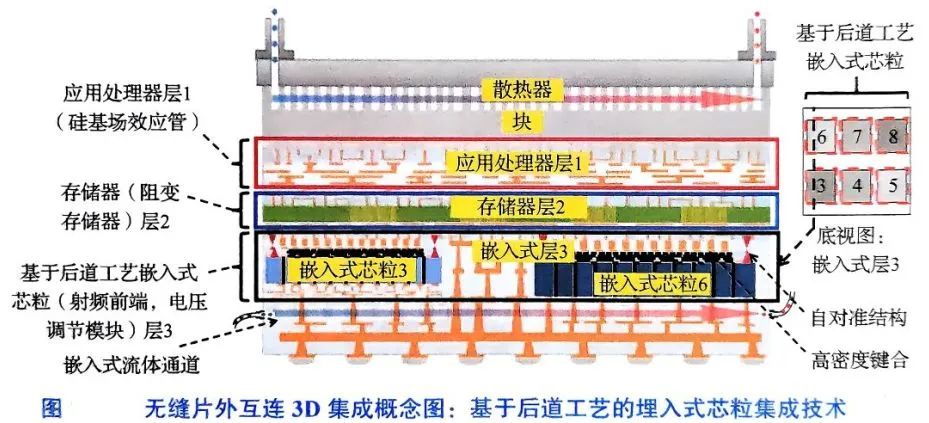

在半導體集成技術向高密度、異構化演進的浪潮中,多片式3D集成方案正成為突破傳統架構物理極限的關鍵路徑。其中,基于后道工藝的埋入式集成方案通過將不同功能的芯粒(如I/O驅動器、射頻前端)嵌入基礎層(如應用處理器)背部,并疊加單片集成內存層(如RRAM),構建出分層解耦的立體系統。

這種設計不僅實現了邏輯、模擬、存儲功能的異質集成,更通過垂直堆疊縮短了互連長度,使信號傳輸效率較傳統2D方案提升3倍以上,同時功耗降低40%。

技術核心:橋接TSV與單片3D的互連范式

該方案的突破性在于通過3D無縫片外互連(SoC+)技術,融合了TSV 3D集成的機械穩定性和單片3D集成的電學優勢。具體而言,其采用兩步鍵合工藝:首先通過銅-銅熱壓鍵合實現芯粒與基礎層的物理連接,再利用混合鍵合(Hybrid Bonding)技術完成微凸點間距僅5μm的垂直互連。這種設計使系統帶寬密度突破1TB/s/mm2,較2.5D封裝提升一個數量級。行業最新案例顯示,AMD采用類似技術在其CDNA3架構中集成HBM3和Infinity Fabric控制器,使GPU核間通信延遲降低至8ns以下。

熱-力協同設計:破解高密度集成難題

面對多層堆疊帶來的熱密度激增(可達100W/cm2以上),該方案創新性地引入動態熱管理架構:在內存層嵌入微流體通道,通過氟化液循環將熱點溫度控制在85℃以下;同時采用梯度熱膨脹系數(CTE)材料,使基礎層與芯粒層的界面應力降低60%。臺積電CoWoS-S Plus技術已驗證此類設計的可靠性,其最新3D封裝通過在硅中介層中預埋應力緩沖層,使12層HBM堆疊的翹曲度控制在50μm以內。

制造工藝突破:自對準技術引領精度革命

為實現0.5μm級互連精度,該方案采用激光干涉輔助自對準技術:在鍵合前通過紫外光刻在芯粒表面生成周期性光柵結構,利用鍵合過程中材料表面張力引發的毛細作用,自動修正初始對準偏差。英特爾Foveros Direct技術已實現此類工藝的量產應用,其3D堆疊良率達到99.2%,較傳統方法提升15個百分點。此外,日本Keltec公司開發的等離子體活化鍵合工藝,可在常溫下實現銅-銅互連的電阻率降至1.8μΩ·cm,接近塊體銅材料性能。

挑戰與展望

盡管前景廣闊,該技術仍面臨兩大瓶頸:一是TSV刻蝕的深寬比突破(當前主流為10:1,需向30:1演進);二是異質材料鍵合的界面缺陷控制(要求空隙率低于0.1%)。產業界正通過雙重曝光TSV工藝和原子層沉積(ALD)界面鈍化技術攻堅。隨著EUV光刻和GAA晶體管技術的協同發展,多片式3D集成有望在2030年前實現萬億晶體管級系統集成,為AI大模型訓練、6G通信等前沿領域提供硬件基石。

-

芯片

+關注

關注

460文章

52566瀏覽量

441804 -

集成電路

+關注

關注

5427文章

12094瀏覽量

368719 -

封裝

+關注

關注

128文章

8716瀏覽量

145619 -

集成技術

+關注

關注

0文章

27瀏覽量

11077

原文標題:基于橋芯片2.5D及3D集成技術的熱評估

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

2.5D/3D芯片-封裝-系統協同仿真技術研究

分享一下小芯片集成的2.5D/3D IC封裝技術

3D封裝結構與2.5D封裝有何不同?3D IC封裝主流產品介紹

2.5D及3D集成技術的熱性能對比

2.5D及3D集成技術的熱性能對比

評論