以下文章來源于OpenFPGA,作者碎碎思

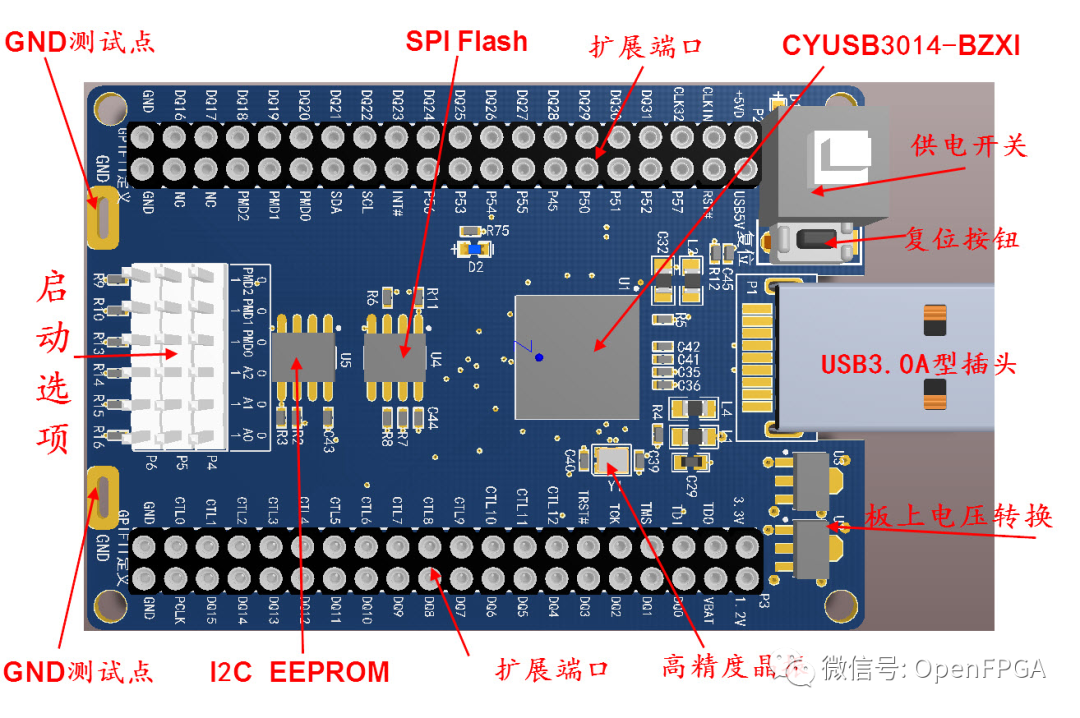

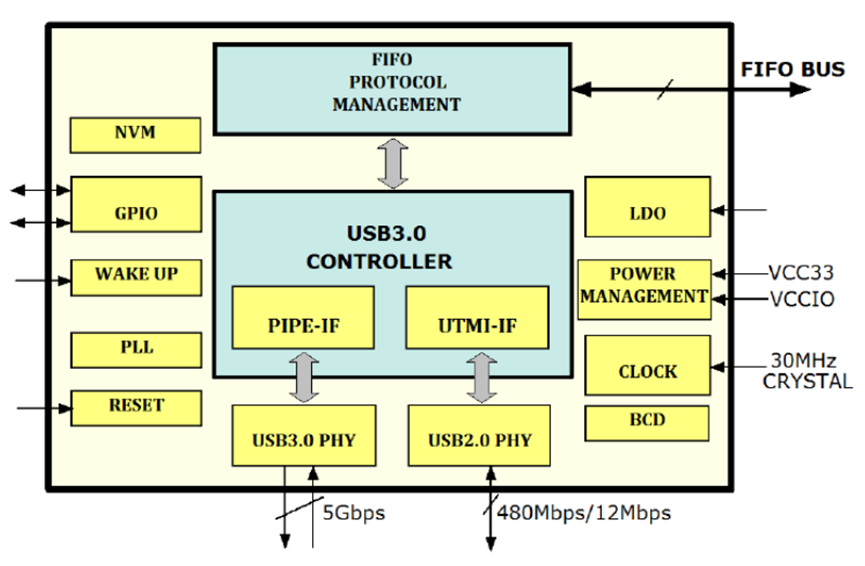

本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下稱 FX3),該芯片是標準的USB3.0 PHY,可以大大簡化使用USB通信時FPGA的設計,主需要使用狀態(tài)機進行FIFO的讀寫控制即可,同時該芯片還具有ARM核+I2S、I2C、SPI、UART等接口,大大增加了該芯片的使用范圍。

FX3應用中后半部分測試已經(jīng)完成暨FX3和PC之間的通信:

接下來就是通過FX3這個“橋梁”實現(xiàn)FPGA與PC之間的通信。

上面基本把各個通信都打通了,本節(jié)將從零開始一步一步搭建一個工業(yè)攝像頭(入門版本)。

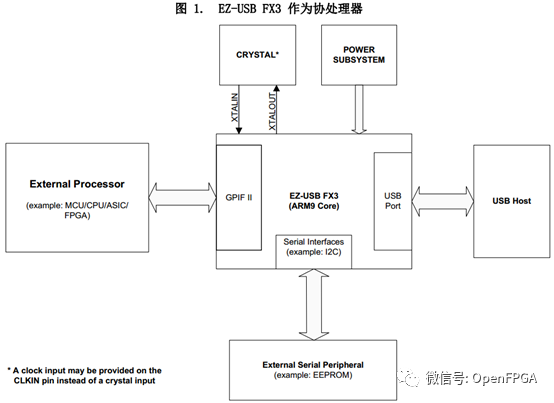

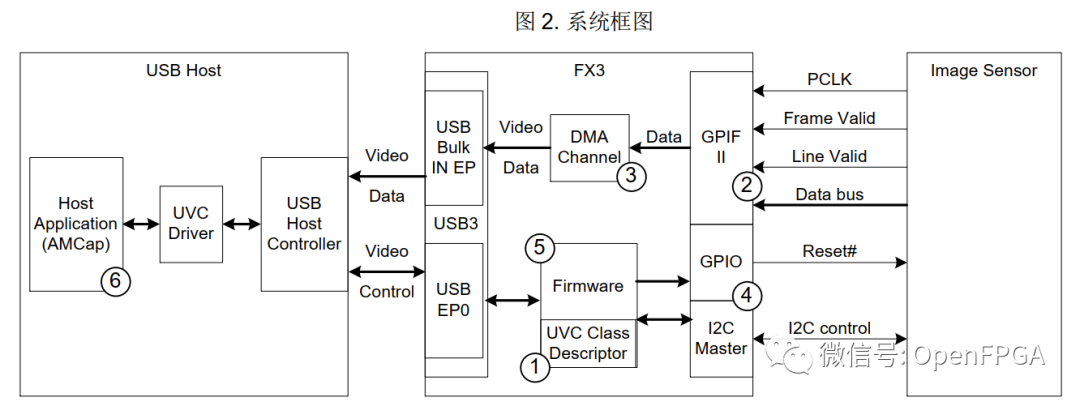

其實不需要FPGA,使用單獨的FX3即可實現(xiàn)一個UVC攝像頭,具體代碼及教程(中英文都有)可以查看官方:

AN75779 - How to Implement an Image Sensor Interface Using EZ-USB FX3 in a USB Video Class (UVC) Framework

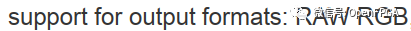

官方的架構如下:

但是這不符合我們的設計要求,考慮到ISP等處理,我們還是需要FPGA參與(還是需要參考官方歷程的),所以下面就開始我們UVC的設計之路。

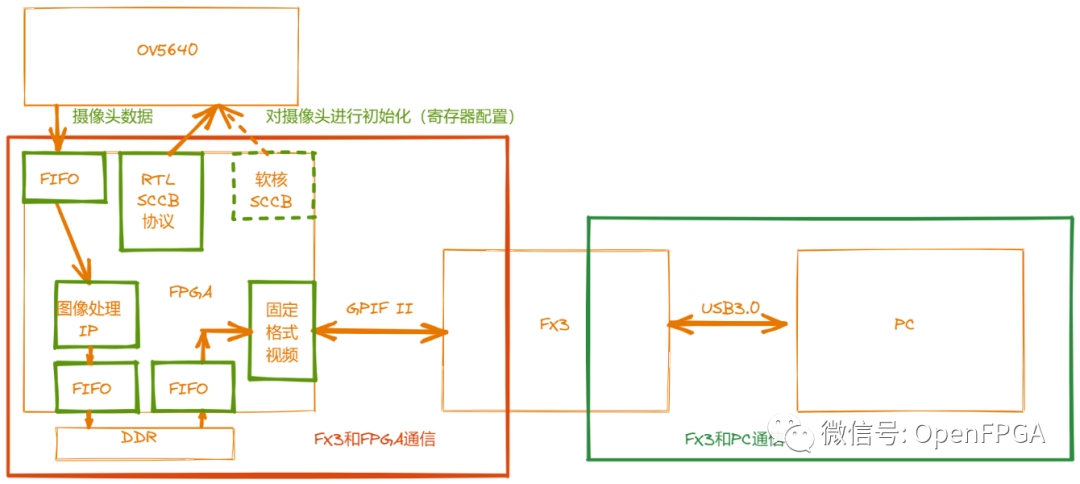

方案設計

首先上電第一步需要通過SCCB(類I2C)接口對攝像頭進行初始化操作,這里有兩種方式:一種是使用FPGA以查找表方式逐個寫入攝像頭中;第二種方式就是通過軟核(Xilinx MicroBlazeAltera NISO II)對攝像頭進行配置,這里廠商都是推薦軟核進行配置,不僅靈活還節(jié)省資源。我們還是“頭鐵”的使用RTL進行配置,配置完成后攝像頭將輸出RAW數(shù)據(jù),接下來FPGA將信號采集到內(nèi)部進行接下來的操作。

在內(nèi)部,視頻數(shù)據(jù)先要經(jīng)過一個FIFO,進行時鐘域轉換,接著RAW數(shù)據(jù)經(jīng)過一個Xilinx的IP核(RAW轉RGB),然后在轉換成YUV(RGB轉YUV),最后通過FIFO寫入到DDR中,最后通過FIFO讀出來的數(shù)據(jù)轉換成可以傳輸進FX3的固定格式視頻,PC端就可以通過一些UVC攝像頭軟件采集到攝像頭(OV5640)數(shù)據(jù)。

PS:關于上面的一些術語,像RAW數(shù)據(jù)、RGB、YUV等可以查看《ISP(圖像信號處理)算法概述、工作原理、架構、處理流程》。

上面方案以FPGA為核心的話,需要三個個部分:1、FPGA和FX3之間通信;2、FPGA和OV5640;3、FPGA和DDR。

其中最簡單的是FPGA和DDR,使用官方IP核即可;

FPGA和FX3通信我們參考官方:

AN75779 - How to Implement an Image Sensor Interface Using EZ-USB FX3 in a USB Video Class (UVC) Framework

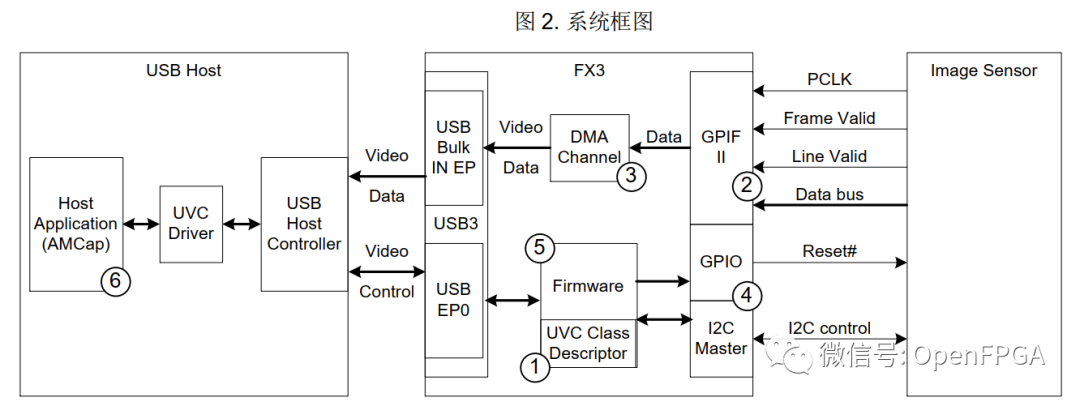

文檔即官方UVC攝像頭應用,只不過把攝像頭換成FPGA即可(后面會有詳細框圖)。

FPGA和OV5640通信也是比較簡單的,網(wǎng)上很多配置寄存器的文件,參考一下即可。

重點就是FPGA和FX3通信。

數(shù)據(jù)流分析

很多人覺得上面的流程比較繁瑣,直接RAW轉RGB(常規(guī)的轉換,RAW數(shù)據(jù)大部分都需要轉換成RGB數(shù)據(jù)再進行后續(xù)的處理)進行傳輸就好了,何必還轉換成YUV呢?

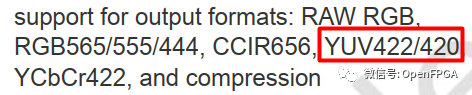

其實這種固定傳輸?shù)慕涌跀?shù)據(jù)流最好分析了,不論后續(xù)時SDI接口、CameraLink接口、HDMI接口,還是我們這次UVC傳輸?shù)腢SB接口,這些接口都是非常標準的接口,需要輸出的數(shù)據(jù)都是標準的,我們這次使用的UVC傳輸?shù)腢SB接口,就是傳輸?shù)腨UV422非壓縮顏色格式數(shù)據(jù),所以我們最后傳輸?shù)木褪荵UV422數(shù)據(jù)。

PS:這里需要的YUV數(shù)據(jù)格式如下:

亮度值 Y 是為所有像素采樣的,而色度值 U 和 V 是僅針對偶像素進行采樣的。也就是說,在解析端,每個像素都由獨立的亮度值 Y,而每 2 個相鄰像素需要共用 1 個色度值 U 和 V。例如,我們以數(shù)字代表第幾個像素,那么頭 6 個像素的數(shù)據(jù)采樣值為:

Y0、U0、Y1、V0 (頭兩個像素) Y2、U2、Y3、V2 (接下兩個像素) Y4、U4、Y5、V4 (接下兩個像素)

整個數(shù)據(jù)流最開始就是RAW數(shù)據(jù)-->XXX-->YUV422,而攝像頭輸出也是RAW RGB數(shù)據(jù),所以第一步是:RAW RGB--> RGB,第二步就是RGB--> YUV422.

OV5640數(shù)據(jù)手冊

OV5640數(shù)據(jù)手冊

FPGA和FX3通信

下面再把官網(wǎng)的應用摘抄下來:

修改一下:

毫無PS痕跡

FX3固件編譯

固件參考 Cypress 的應用筆記 AN75779

GPIF II接口設置

打開桌面應用程序

打開工程

選擇

XXXfirmwarecyfxuvc_an75779fx3_uvc.cydsn

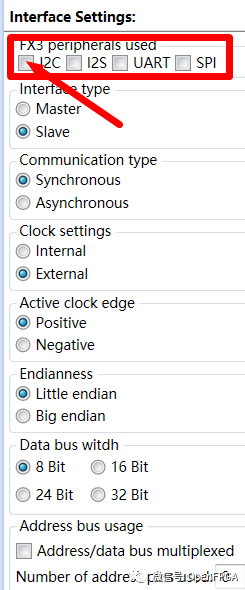

在官方的文件基礎上去掉I2C(官方是直接接攝像頭,需要通過I2C對攝像頭進行配置),我們的配置是通過FPGA進行配置的,所以就不需要I2C。其他都不變

Build--> Build setting

就設置OutPut Location(理論任何位置都可以,方便分類我們放到工程文件夾下):

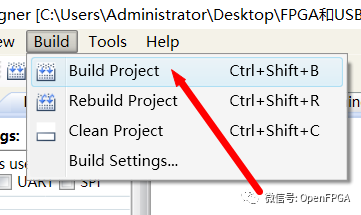

Build--> Build Project

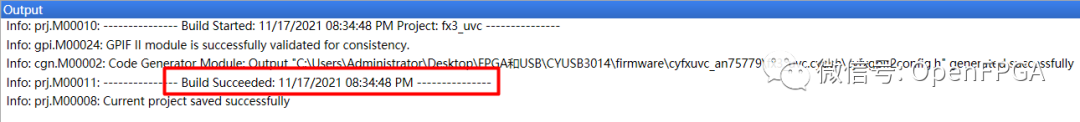

會在OutPut窗口提示編譯成功:

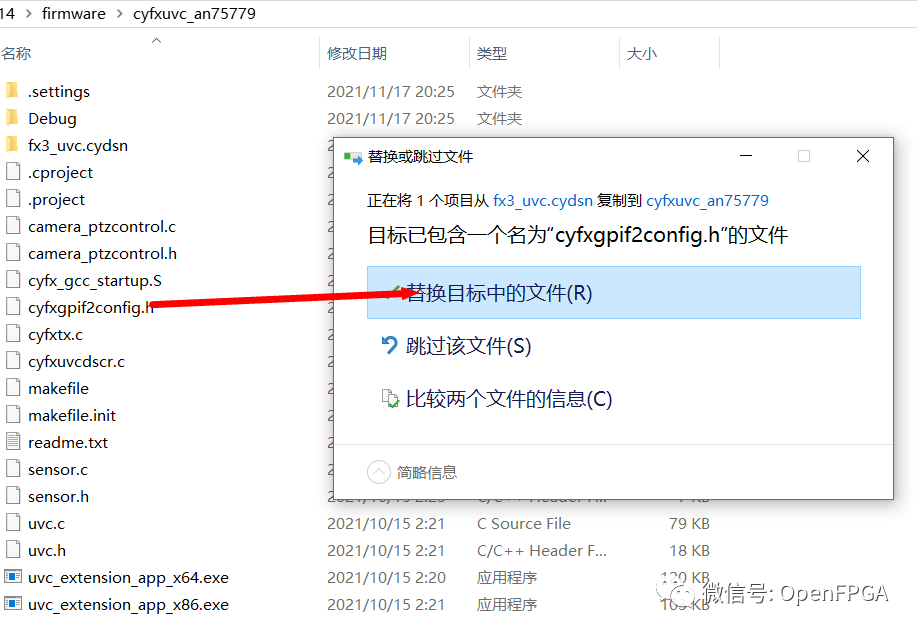

會在設置的文件下產(chǎn)生我們需要的配置頭文件

將上面的文件拷貝到《AN75779》SDK工程文件夾下,替換原來的文件。

產(chǎn)生所需要的FX3固件

打開SDK

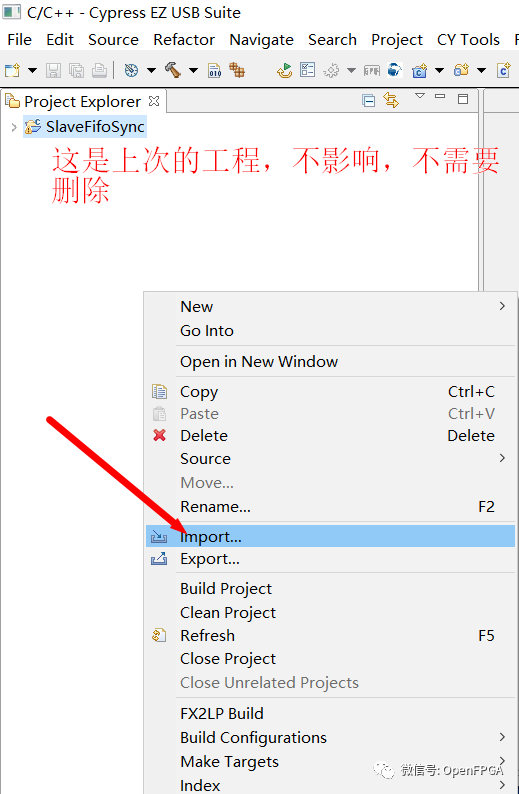

右擊--Import ,導入工程

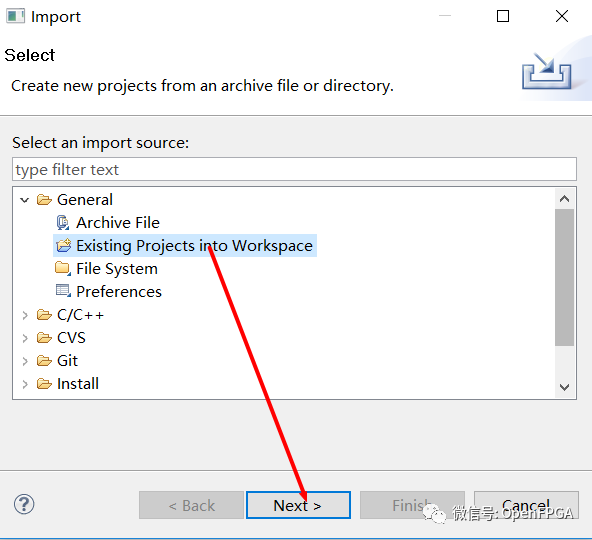

按照下圖設置,點擊【Next】

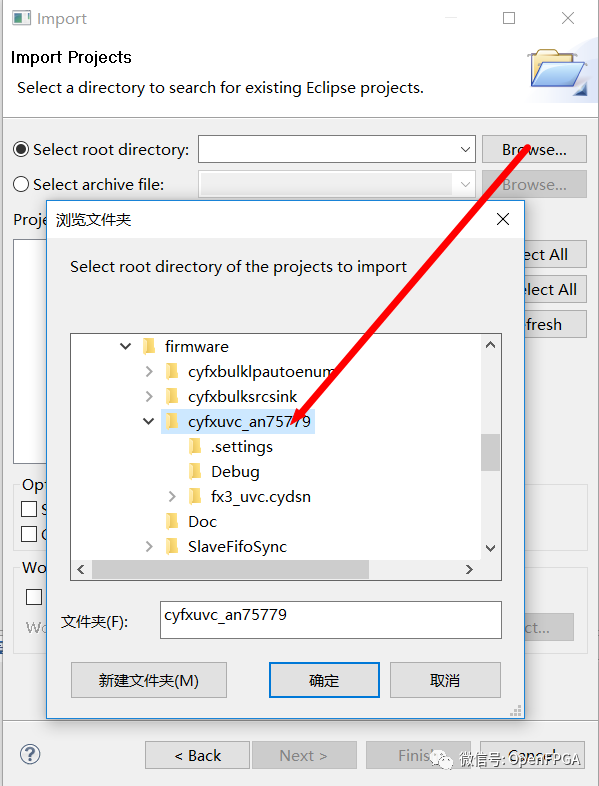

點擊【Browse】選擇剛剛復制配置頭文件的工程文件夾。

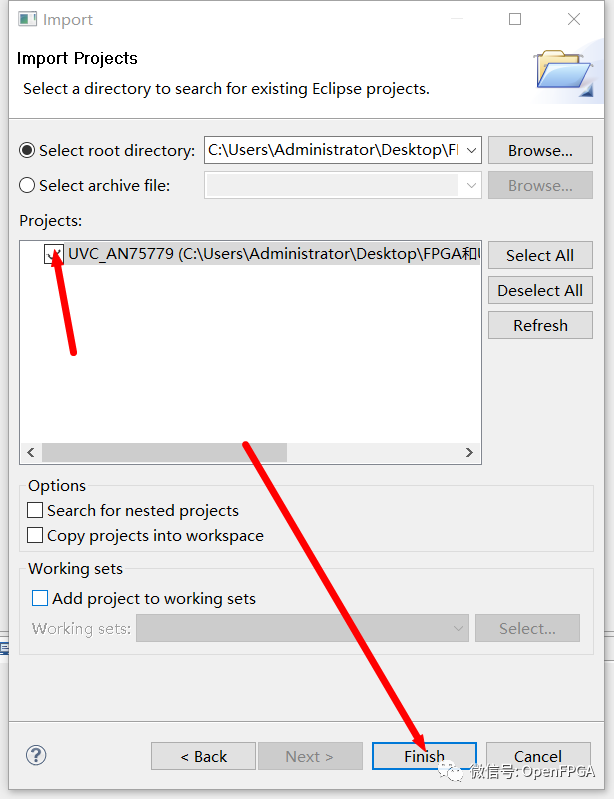

會識別到工程,然后勾選選擇,點擊【FINISH】

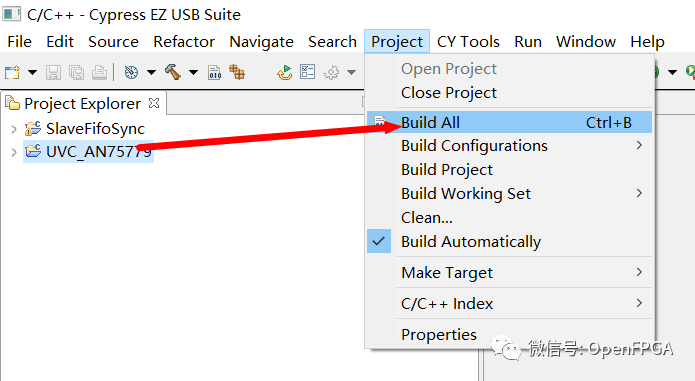

選中工程,Project-> Build All

等待編譯完成,會輸出下列打印信息。

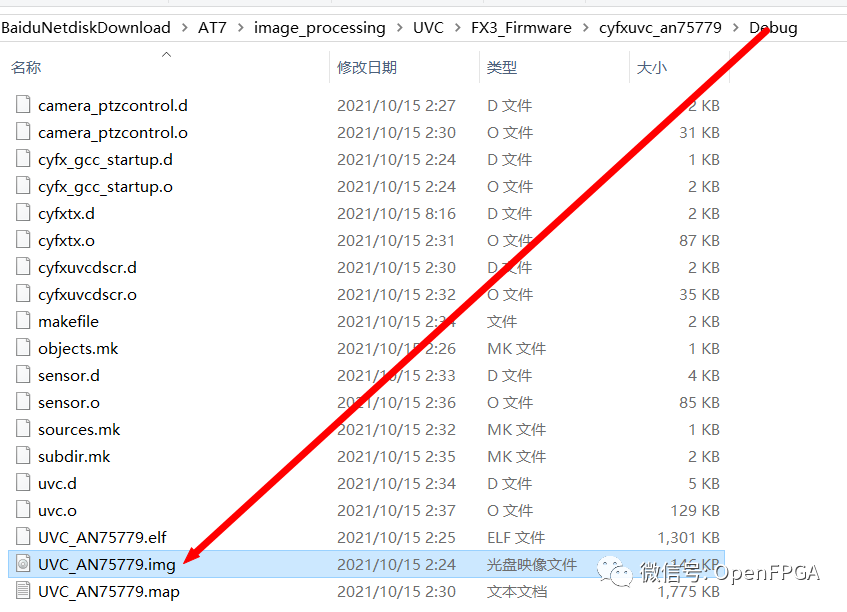

會在Debug文件下產(chǎn)生我們所需要的固件。

下載固件

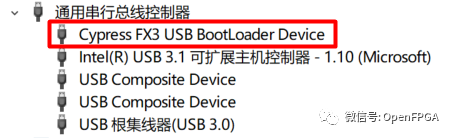

選擇FX3啟動模式從【USB啟動 】,插入PC的USB3.0接口:

設備管理器的信息。

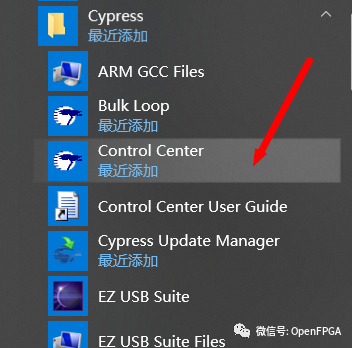

啟動Control Center

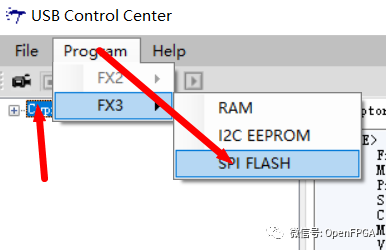

選中需要下載的設備,Program-->FX3-->SPI Flash

選擇剛剛生成的固件

查看進度:

看到下圖的提示,表示下載成功。

斷電重啟,設備管理器里就可以看到攝像頭設備:

關于SDK中的一些修改及配置,請參考Cypress官方AN75779 - UVC圖像采集應用筆記。

內(nèi)有中文版詳細說明,篇幅有限請自行查看。

FPGA端RTL設計

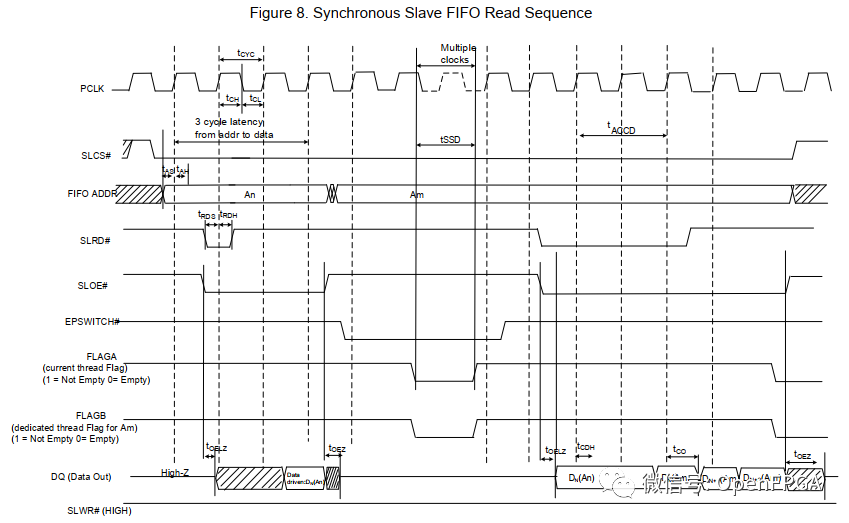

這部分主要參考《FPGA和USB3.0通信-聯(lián)合測試(一)》中的同步時序,這里貼一下:

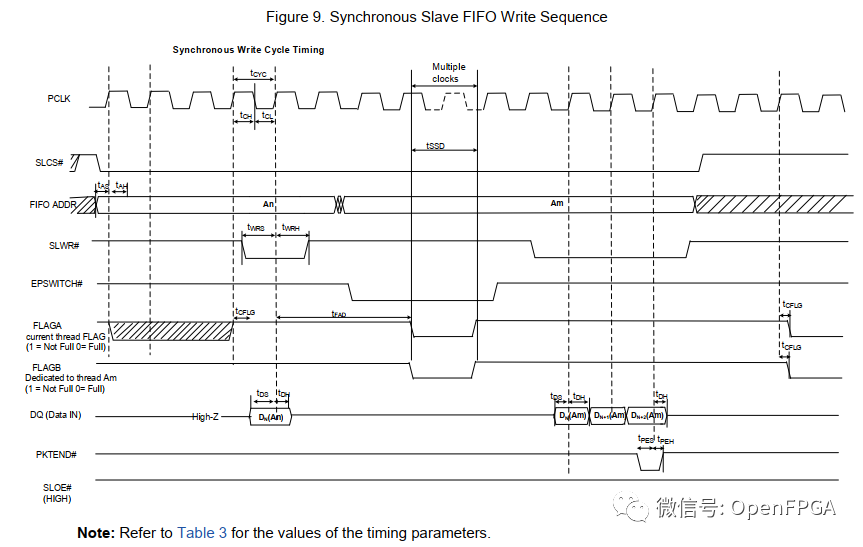

對于這次應用主要使用寫應用,寫應用的時序如下:

1.FIFO地址穩(wěn)定且SLCS#信號被激活。

2.外部主設備/外設將數(shù)據(jù)輸出到數(shù)據(jù)總線上。

3.SLWR#被激活。

4.當SLWR#被激活時,數(shù)據(jù)將被寫入到FIFO內(nèi),并且,F(xiàn)IFO指針將在PCLK的上升沿上遞增。

5.從時鐘的上升沿起,經(jīng)過tCFLG的延遲后,F(xiàn)IFO標志將被更新。

突發(fā)寫入時將發(fā)生相同的事件序列。

注意:在突發(fā)模式下,SLWR#和SLCS#在整個突發(fā)寫入過程中保持激活狀態(tài)。在突發(fā)寫入模式下,SLWR#被激活 后,每當PCLK的上升沿到來時,都會將數(shù)據(jù)總線上的值寫入到FIFO內(nèi)。此外,F(xiàn)IFO指針也在PCLK的每個上升沿 上得到更新。

短數(shù)據(jù)包:通過PKTEND#信號可將某個短數(shù)據(jù)包發(fā)送到USB主機。需要設計外部器件/處理器,使之在傳輸最后數(shù)據(jù) 字時同時激活與該字相應的SLWR#脈沖和PKTEND#。PKTEND#激活期間,F(xiàn)IFOADDR需要保持不變。同時激活 PKTEND#和SLWR#時,GPIFII狀態(tài)機會將數(shù)據(jù)包視為短數(shù)據(jù)包,并將其發(fā)送到USB接口。如果協(xié)議不要求傳輸任 何短數(shù)據(jù)包,則PKTEND#信號可被置高。

請注意,執(zhí)行讀操作時,沒有任何具體信號表示已從USB獲取了短數(shù)據(jù)包。空標志必須由外部主設備監(jiān)控,以確定讀 取完所有數(shù)據(jù)的時間。

零長度數(shù)據(jù)包:外部器件/處理器可僅通過激活PKTEND#,而沒有激活SLWR#來傳輸一個零長度數(shù)據(jù)包(ZLP)。必須驅動SLCS#和地址,如圖5所示。

標志使用情況:外部處理器監(jiān)控標志信號來控制流量。標志信號由EZ-USBFX3器件輸出。通過配置各標志,可顯示 專用線程或當前尋址線程的空/滿/局部狀態(tài)。

上面是針對寫FIFO時序進行說明,針對UVC使用時還需要注意視頻幀格式傳輸,我們上面分析了FX3 UVC是屬于YUV422格式,格式的具體分析上面也有了。

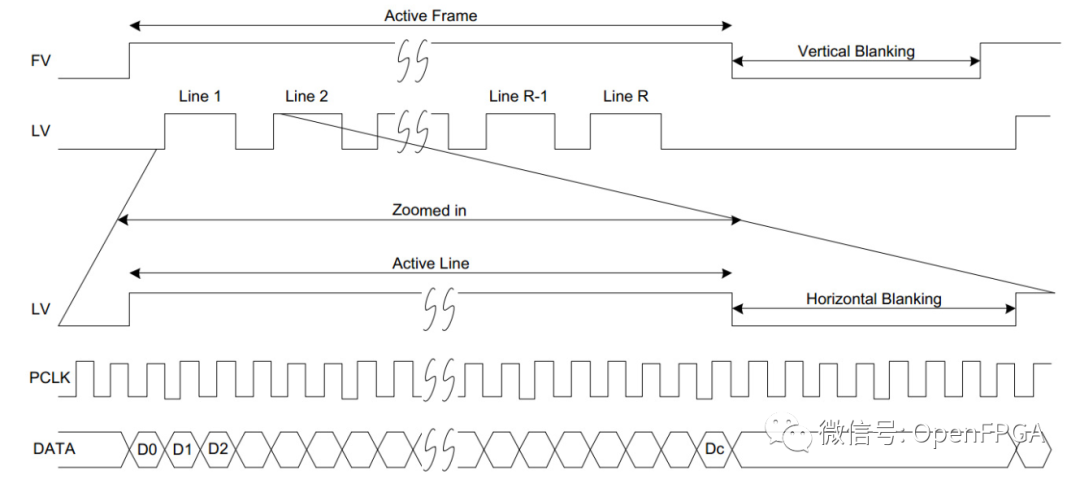

通過上面圖片我們知道這次應用FPGA和FX3的引腳關系,具體說明如下:

| 信號名 | 功能描述 | FX3 引腳 |

|---|---|---|

| FV | 幀有效(表示幀的開始和結束) | GPIO[29] |

| LV | 行有效(表示行的開始和結束) | GPIO[28] |

| PCLK | 像素時鐘(即同步接口的時鐘) | GPIO[16] |

| Data[7:0] | 8bit位寬的圖像數(shù)據(jù) | DQ[7:0] |

具體時序如下:

PS:大家記住FV LV等信號定義,這在視頻處理領域是非常常見的。

FPGA和攝像頭通信

攝像頭配置

上電第一步就是配置攝像頭,這次設計使用寄存器進行配置,配置參數(shù)參考《CrazyBingo》曾經(jīng)的OV5640寄存器配置:

這部分整體思路就是通過查找表上電后將寄存器通過SCCB接口一個一個寫入OV5640中,其他的攝像頭網(wǎng)上也有配置好的寄存器文件,自行查找替換即可。

讀取攝像頭數(shù)據(jù)

配置完成攝像頭就需要讀取攝像頭數(shù)據(jù),我們只需要按照下面的時序寫進FIFO即可。

FPGA主要RTL模塊說明

RGB 轉 YUV 說明

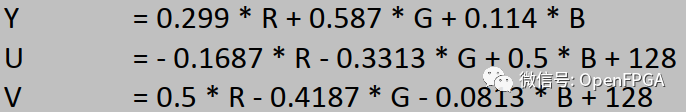

這部分在之前分享的《視頻技術手冊》中有詳細說明,這里截圖一下:

如果R'B'G'數(shù)據(jù)的取值范圍為0~255(計算機體系中是這樣),公式需要在后面+128,經(jīng)過一些測試及更改,目前的公式變成:

FPGA實現(xiàn)時,無法對小數(shù)進行操作,所以要對計算進行放大,然后計算結果再縮小即可:

工程使用說明

連接相應的硬件,下載程序到FPGA中,通過VIO選擇相應的輸出源(1:輸出16階灰色;0:攝像頭輸出。為了對比方便看攝像頭輸出)。

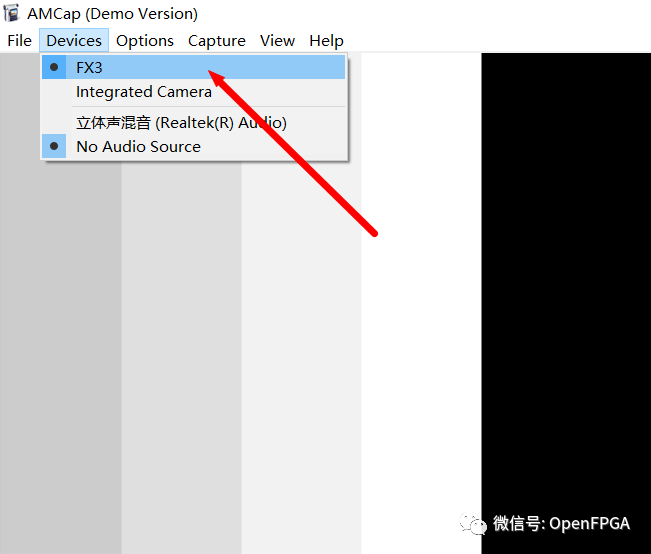

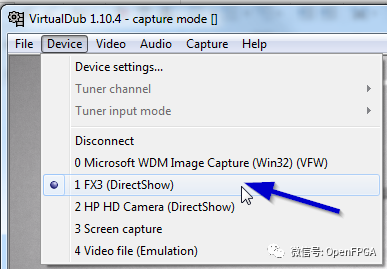

PC端打開AMCap(收費,好用), VirtualDUB(開源,地址:http://virtualdub.sourceforge.net/):

AMCap:

只需要在Devices-->FX3就可以顯示我們輸出到PC端視頻了。

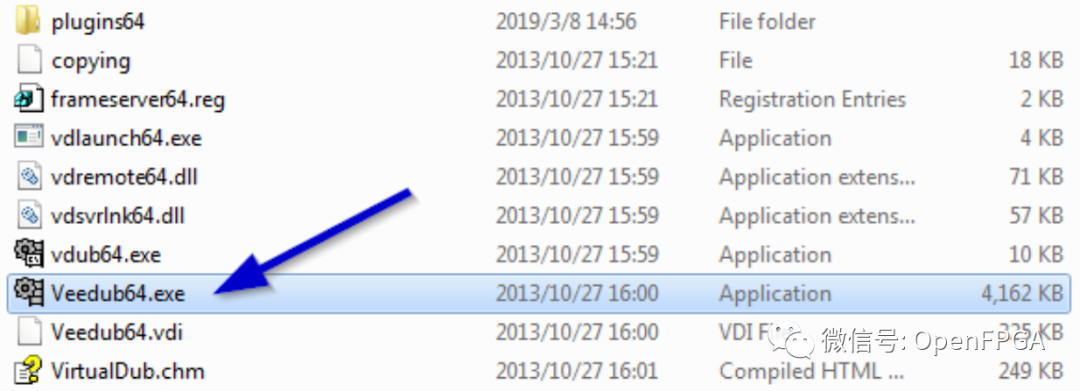

VirtualDUB:

運行上圖中的程序;

菜單 Fil --> Capture AVI…

菜單 Device-->FX3 (DirectShow)

視頻效果:

VIO選擇1:輸出16階灰色

VIO選擇0:輸出攝像頭數(shù)據(jù)

PS:如果上述兩個軟件選擇不了FX3,請先檢查設備管理器里有沒有識別到FX3,如果沒有請查看之前的文章把硬件測試做一下。

總結

最后在說明一下上面的操作其實是沒必要的,攝像頭是直接可以輸出YUV422的(這種應用就是為什么攝像頭可以直接和FX3對接的原因),我們是為了后續(xù)的視頻處理才選擇RGB(很多算法都是基于RGB顏色空間)。

這一些列文章就結束了,由于作者水平有限,不免有些錯誤,大家可以在后臺或者加微信留言說明,謝謝大家支持。

-

FPGA

+關注

關注

1646文章

22054瀏覽量

618783 -

USB3.0

+關注

關注

1文章

274瀏覽量

80917 -

通信

+關注

關注

18文章

6207瀏覽量

137860 -

攝像機

+關注

關注

3文章

1706瀏覽量

61454

原文標題:FPGA和USB3.0通信-UVC攝像機

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

基于FPGA+USB3.0的UVC Camera實現(xiàn)方案

FPGA和USB3.0通信-FX3硬件設計資料分享

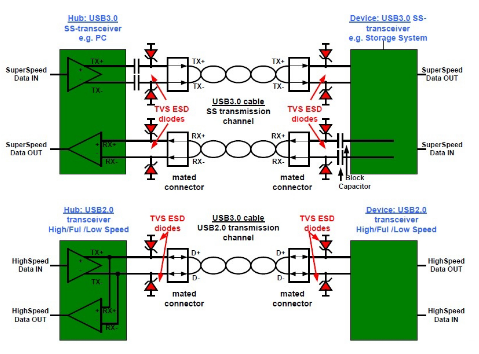

USB3.0系統(tǒng)的ESD防護設計方案

FPGA和USB3.0通信-USB3.0協(xié)議簡介

FPGA和USB3.0通信-硬件測試之SDK的安裝

FPGA和USB3.0通信-FX3硬件設計簡談

基于FPGA的USB3.0 HUB設計方案

基于FPGA和USB3.0通信的UVC攝像機設計方案

基于FPGA和USB3.0通信的UVC攝像機設計方案

評論